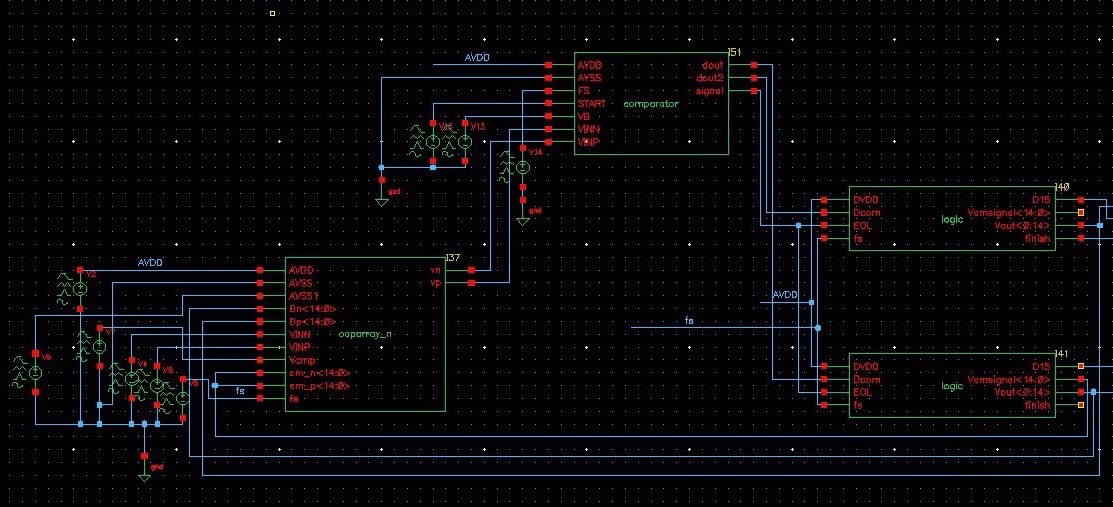

【16位SAR ADC 逐次逼近型ADC模拟集成电路设计】 16位SAR ADC 同步时序; 采样率1MHz; 动态比较器; 栅压自举采样开关; 测试电路; 精度为14.61; 台湾65nm工艺 下载后可直接使用,保证仿出正确波形。 有matlab代码,FFT,计算ENOB SNDR SFDR SNR THD 附带自己收集的的一些珍贵adc资料何乐年,sar adc 仿真教程

在模拟集成电路设计的领域里,16 位 SAR ADC(逐次逼近型模数转换器)一直是个备受关注的存在。今天就来和大家唠唠我在这方面的一些实践与心得。

设计关键要素

同步时序

同步时序在整个设计中起着节拍器的作用。它确保了 ADC 各个模块有条不紊地工作。就好比一场精心编排的舞蹈,每个舞者(模块)都在特定的时间点做特定的动作。在代码实现上,这可能涉及到一系列的时钟信号控制逻辑。比如在 Verilog 中,可以这样简单示意:

verilog

module sync_timing (

input wire clk, // 时钟信号

input wire rst_n, // 复位信号,低电平有效

output reg sample_en, // 采样使能信号

output reg convert_en // 转换使能信号

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

sample_en <= 0;

convert_en <= 0;

end else begin

// 这里可以根据具体的时序要求,比如采样阶段和转换阶段的时间分配来设置逻辑

// 假设先进行采样,然后进行转换

if (!sample_en) begin

sample_en <= 1;

end else if (sample_en &&!convert_en) begin

sample_en <= 0;

convert_en <= 1;

end

end

end

endmodule这段代码通过时钟信号和复位信号来控制采样使能和转换使能信号的产生,从而实现同步时序。

采样率 1MHz

1MHz 的采样率决定了 ADC 对输入信号的采样频率。这就像你给一幅画拍照,每秒拍 100 万次,这个频率要和整个系统的需求相匹配。过高的采样率可能会增加系统的负担,而过低则可能丢失信号的重要信息。

动态比较器

动态比较器是 SAR ADC 中的核心部件之一。它在转换过程中比较输入信号和 DAC 输出信号的大小。动态比较器的优势在于其功耗低、速度快。以简单的两级动态比较器为例,在电路设计中,其工作原理大概可以用以下代码片段(以 VHDL 为例)来表示:

vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity dynamic_comparator is

Port ( inp : in STD_LOGIC;

ref : in STD_LOGIC;

clk : in STD_LOGIC;

rst_n : in STD_LOGIC;

outp : out STD_LOGIC);

end dynamic_comparator;

architecture Behavioral of dynamic_comparator is

signal preamp_out : STD_LOGIC;

begin

process(clk, rst_n)

begin

if rst_n = '0' then

preamp_out <= '0';

outp <= '0';

elsif rising_edge(clk) then

-- 前置放大器阶段

if inp > ref then

preamp_out <= '1';

else

preamp_out <= '0';

end if;

-- 锁存阶段

outp <= preamp_out;

end if;

end process;

end Behavioral;这里通过时钟信号和复位信号,实现了输入信号与参考信号的比较以及结果的锁存。

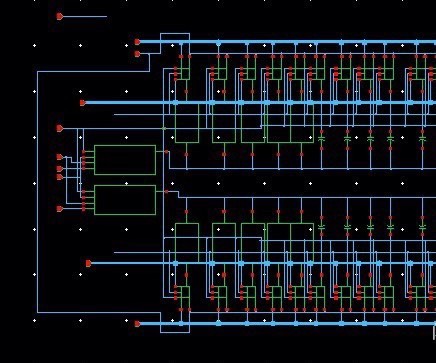

栅压自举采样开关

栅压自举采样开关在采样过程中发挥着重要作用。它能够在采样阶段高效地对输入信号进行采样,并保持信号。其原理是利用自举电容来提升开关管的栅源电压,从而提高开关的导通能力。在电路版图设计中,要特别注意自举电容的布局和参数设置,以确保其性能。

测试电路

测试电路是验证 ADC 性能的关键。它需要能够产生各种测试信号,对 ADC 的各项指标进行检测。比如可以设计一个简单的测试电路,通过生成不同频率和幅度的正弦波信号作为 ADC 的输入,然后观察输出结果。在 Matlab 中可以这样生成测试信号:

matlab

fs = 1000000; % 采样率 1MHz

t = 0:1/fs:0.01; % 10ms 的时间序列

f = 10000; % 输入信号频率 10kHz

x = sin(2*pi*f*t); % 生成正弦波信号这段代码生成了一个 10kHz 的正弦波信号,采样率为 1MHz,时长为 10ms,可用于测试 ADC。

性能指标与工艺

本次设计精度达到了 14.61,采用的是台湾 65nm 工艺。这个工艺节点在当今的集成电路制造中有着广泛的应用,它在成本和性能之间达到了较好的平衡。

代码与资料

设计中包含了 Matlab 代码,通过 FFT(快速傅里叶变换)来计算 ENOB(有效位数)、SNDR(信噪失真比)、SFDR(无杂散动态范围)、SNR(信噪比)以及 THD(总谐波失真)等重要指标。例如计算 SNR 的 Matlab 代码:

matlab

% 假设 y 是 ADC 的输出数字信号

y = adc_output;

P_signal = sum(abs(y).^2)/length(y);

noise = y - mean(y);

P_noise = sum(abs(noise).^2)/length(noise);

SNR = 10*log10(P_signal/P_noise);此外,还附带了自己收集的一些珍贵 ADC 资料,像何乐年的 SAR ADC 仿真教程,对于深入理解 SAR ADC 的设计和仿真有很大的帮助。而且下载后可直接使用,保证能仿出正确波形,方便大家进一步学习和研究。希望这些内容能给对 16 位 SAR ADC 设计感兴趣的朋友一些启发和帮助。