上一章我们搞懂了触发器的底层逻辑,知道它是计算机"记忆功能"的最小单元。而今天的主角------寄存器,正是触发器的"组合升级版"。如果说触发器是"能存1位数据的小抽屉",那寄存器就是"能存多位数据的贴身文件柜",直接镶嵌在CPU内部,是连接全加器等运算单元与内存的核心枢纽。

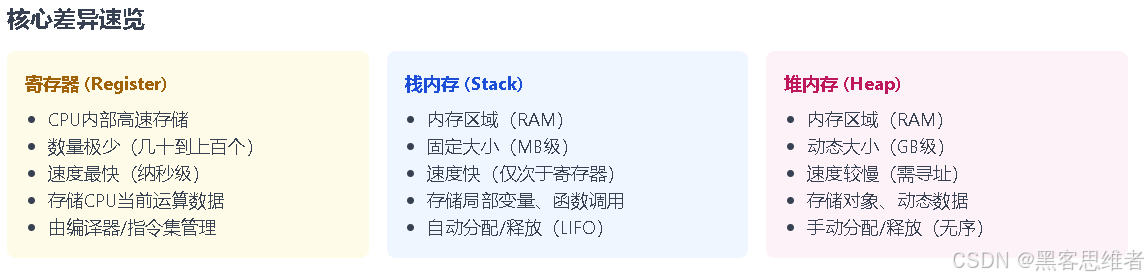

在搞懂寄存器之前,我们先回顾一个关键痛点:全加器的运算速度是纳秒级,但内存的读写速度是几十纳秒------如果CPU每次运算都要从内存读取数据、运算后再写回内存,运算效率会被内存速度严重拖累。而寄存器的出现,就是为了解决"运算速度与存储速度不匹配"的问题------它是CPU的"贴身高速仓库",让运算单元能直接访问高频数据,大幅提升效率。

这一章我们就把寄存器彻底讲透:从它的核心原理(如何由触发器组成?为什么这么快?),到常见类型(通用寄存器、专用寄存器)的区别与具体用途,再到它如何组成寄存器组、流水线寄存器等复杂电路,最后拆解它在计算机中的实际应用,以及对我们理解底层逻辑和编程的意义------搞懂寄存器,你才能真正明白"CPU如何高效处理数据",也能解释清楚很多编程中的性能优化问题。

一、先搞懂核心:寄存器的本质是什么?为什么能成为"高速仓库"?

寄存器的核心定位是"CPU内部的高速临时存储单元",专门存储CPU正在处理、即将处理的数据和指令。要理解它的本质,我们需要从"组成原理"和"速度优势根源"两个维度拆解。

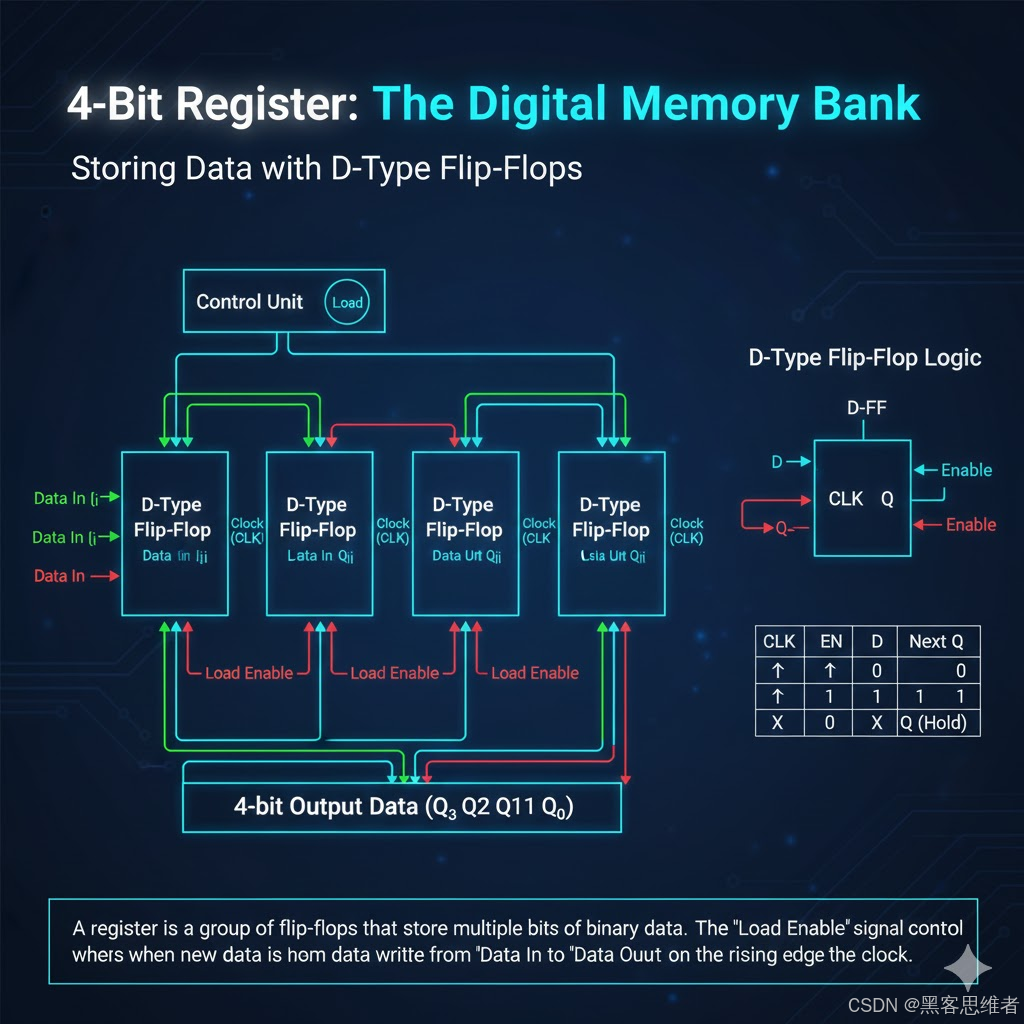

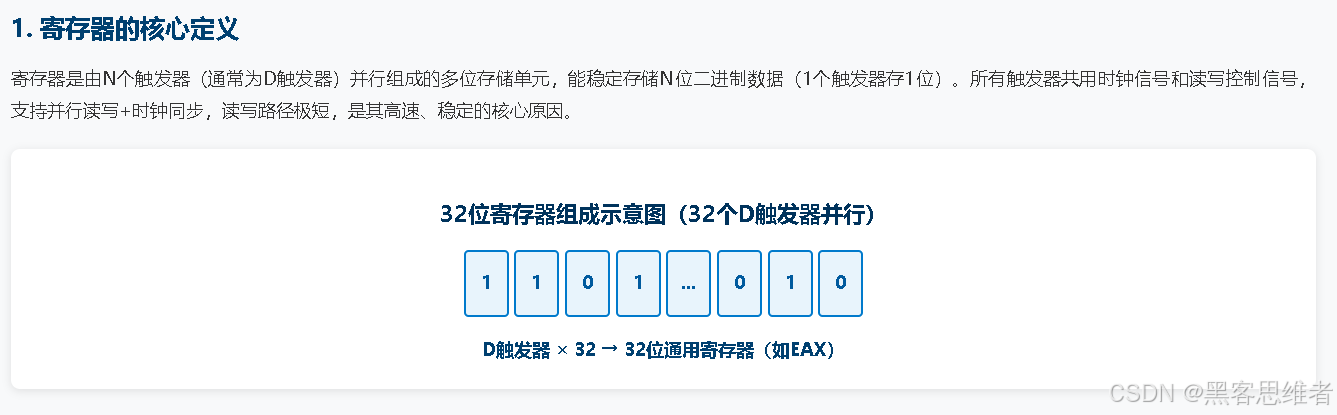

1. 寄存器的核心定义:由多个触发器并行组成的多位存储单元

寄存器的本质很简单:由N个触发器(通常是D触发器)并行连接而成,能稳定存储N位二进制数据(1个触发器存1位)。比如我们常说的32位通用寄存器(如eax),就是由32个D触发器并行组成的;64位寄存器则是由64个D触发器组成。

-

组成逻辑细节:所有触发器共用一个时钟信号(CP)和一组读写控制信号;当读写控制信号有效且时钟信号触发时(比如上升沿),N位数据会同时写入所有触发器(并行写入);读取时,所有触发器的状态也会同时输出(并行读取);

-

核心特性:并行读写+时钟同步,这是它"高速"和"稳定"的核心原因------相比内存的"地址译码→定位单元→串行读写",寄存器的读写路径极短,几乎没有延迟。

举个通俗的例子:寄存器就像你办公桌上的"即时文件架",放着你正在处理的文件(数据),伸手就能拿到;而内存就像办公室的"档案柜",存放大量文件,但需要起身、找钥匙、翻档案,耗时更长。全加器(就像你正在工作的大脑)处理数据时,直接从"即时文件架"拿数据,效率自然极高。

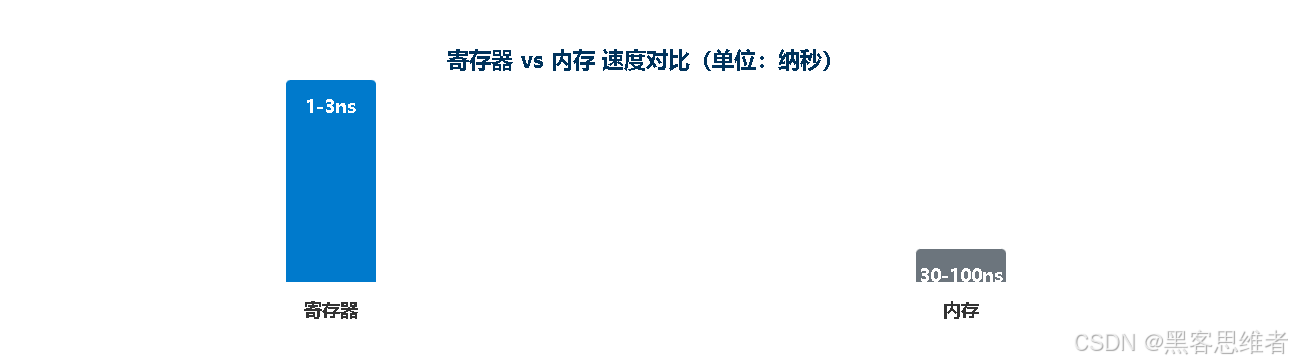

2. 寄存器的速度优势根源:物理位置+简化结构

寄存器的读写速度比内存快100倍以上(寄存器:1-3纳秒;内存:30-100纳秒),核心原因有两个,都和硬件设计直接相关:

-

物理位置极近:寄存器直接集成在CPU芯片内部,与ALU(运算单元)、控制单元(CU)的距离极近------数据传输路径短,传输延迟几乎可以忽略;而内存是CPU外部的独立硬件,数据需要通过"CPU引脚→地址总线→数据总线→内存控制器→内存芯片"的漫长路径传输,每一步都有延迟;

-

结构极简无冗余:寄存器的核心是"触发器+简单控制逻辑",没有复杂的地址译码器、存储阵列刷新电路(内存需要不断刷新才能保持数据)------读写时只需控制触发器的时钟和读写信号,操作逻辑极简,自然速度快;

-

补充:为什么寄存器容量小? 速度快的代价是"成本高、占用空间大"------一个64位寄存器需要64个D触发器(每个触发器约20个晶体管),共1280个晶体管;如果CPU要集成1000个64位寄存器,就需要128万个晶体管,占用大量芯片面积(芯片面积直接影响成本和功耗)。因此,CPU的寄存器数量通常只有几十个(比如x86架构32位有8个通用寄存器,64位扩展到16个),以"小容量、高速度"为核心定位。

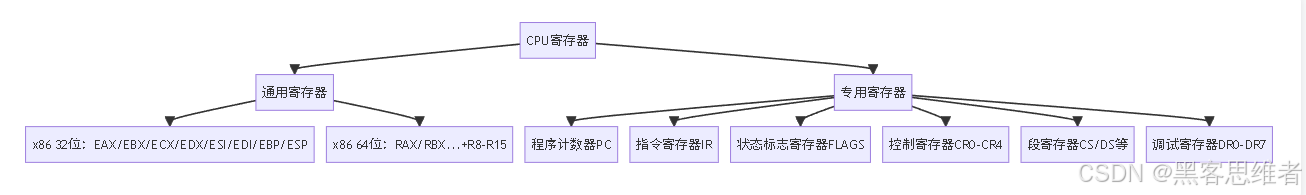

二、寄存器的常见类型:按功能分类,各司其职支撑CPU工作

CPU内部的寄存器按"功能定位"可分为两大类:通用寄存器(可自由使用,存储任意数据)和专用寄存器(有固定用途,只能存储特定类型的数据/状态)。每种类型下又有具体的细分寄存器,我们逐一拆解,重点讲清每种的核心用途和实际作用。

1. 通用寄存器:程序员的"万能数据容器"

通用寄存器是最灵活的寄存器,没有固定用途,程序员(或编译器)可以用它存储正在运算的数据、临时变量、内存地址等。不同CPU架构的通用寄存器数量和命名不同,我们以最常见的x86(32位)和x86-64(64位)架构为例讲解。

(1)x86架构32位通用寄存器(8个)

-

EAX(累加器) :最常用的寄存器,专门用于算术运算(比如全加器的输入/输出数据)、函数返回值存储;很多指令默认使用EAX作为运算目标,比如

add eax, ebx(EAX = EAX + EBX); -

EBX(基址寄存器):常用于存储内存地址的"基地址",比如访问数组时,EBX存储数组的起始地址,再通过偏移量定位具体元素;

-

ECX(计数器) :专门用于循环计数,比如

for循环中,ECX存储循环次数,每循环一次自动递减,直到为0时循环结束; -

EDX(数据寄存器):常与EAX配合使用,存储64位数据的高32位(EAX存低32位),或存储乘法/除法的余数、高位结果;

-

ESI(源变址寄存器):用于"数据复制"场景,存储源数据的内存地址,比如从内存读取数据到寄存器时,ESI指向源数据地址;

-

EDI(目的变址寄存器):与ESI配合使用,存储目的数据的内存地址,比如把ESI指向的数据复制到EDI指向的内存地址;

-

EBP(基址指针寄存器):专门用于维护函数的"栈帧"(函数调用时的局部变量、参数存储区域),EBP存储栈帧的基地址,通过EBP+偏移量可以精准访问函数的局部变量和参数;

-

ESP(栈指针寄存器):存储当前栈的"栈顶地址",栈的push(压入数据)、pop(弹出数据)操作都会修改ESP的值------比如push一个数据时,ESP递减4(32位数据);pop时,ESP递增4。

(2)x86-64架构64位通用寄存器(16个)

x86-64架构在32位的基础上,将通用寄存器扩展到16个,名称在原有基础上增加"R"前缀(比如EAX扩展为RAX),同时新增了R8-R15共8个寄存器。核心优势是"减少寄存器与内存的数据交换"------更多的寄存器可以存储更多临时数据,不用频繁从内存读取,大幅提升程序效率。

通用寄存器的核心特点与用途总结

-

灵活度高,可存储数据/地址;

-

是编译器优化的核心对象------编译器会自动将频繁使用的变量(比如循环变量、累加器)分配到通用寄存器,减少内存访问;

-

编程时可通过汇编指令直接操作(比如C语言内嵌汇编),但高级语言中通常由编译器自动管理。

2. 专用寄存器:CPU的"专用功能组件",有固定用途

专用寄存器是为特定功能设计的,有固定的用途和操作规则,程序员通常不能直接修改(部分可通过特定指令访问)。核心作用是"支撑CPU的核心工作流程",比如指令执行、状态记录、地址转换等。

-

程序计数器(PC/IP) :

核心用途:存储"下一条要执行的指令在内存中的地址";

-

工作逻辑:CPU执行完一条指令后,PC会自动递增(指向当前指令的下一条);遇到分支指令(if-else、函数调用)时,CPU会修改PC的值(指向分支目标地址);

-

组成:由T触发器组成(支持翻转/递增),是CPU"按顺序执行指令"的核心保障。

指令寄存器(IR) :

核心用途:存储"当前正在解码/执行的指令";

工作逻辑:CPU从内存读取指令后,先存入IR,再由指令解码器解读指令的操作码和操作数;

特点:只读寄存器(只能由CPU写入指令,不能由程序员修改),是"取指→解码→执行"流水线的关键节点。

状态标志寄存器(FLAGS/EFLAGS/RFLAGS) :

核心用途:存储"指令执行后的状态信息"(比如是否进位、是否溢出、是否为零);

组成:由多个1位触发器组成,每个触发器对应一个状态标志位(比如CF进位标志、ZF零标志、OF溢出标志);

工作逻辑:每次算术运算(比如加法、减法)后,CPU会自动更新FLAGS的标志位;后续指令(比如条件跳转)会根据这些标志位判断是否执行------比如jmp if ZF=1(如果ZF=1,说明上一次运算结果为零,执行跳转)。

控制寄存器(CR0-CR4) :

核心用途:存储"CPU的控制信息",控制CPU的工作模式、内存管理、缓存开关等;

举例:CR0中的PE位(保护模式启用位),PE=1时CPU进入保护模式(支持多任务、内存分页),PE=0时进入实模式(早期DOS系统使用);

特点:只有操作系统内核才能修改,用户程序没有权限------这是保障系统安全和稳定的核心。

段寄存器(CS/DS/ES/FS/GS/SS) :

核心用途:存储"内存段的基地址",配合偏移地址实现"分段内存管理";

举例:CS(代码段寄存器)存储程序代码所在内存段的基地址,PC存储偏移地址,CPU通过"CS:PC"的组合得到指令的物理地址;SS(栈段寄存器)存储栈所在内存段的基地址,配合ESP得到栈顶物理地址;

演变:x86-64架构中,分段管理逐渐被分页管理替代,段寄存器的作用弱化,但仍保留用于兼容旧程序。

调试寄存器(DR0-DR7) :

核心用途:支持程序调试,存储"断点地址""调试状态"等信息;

举例:DR0可存储一个内存地址,当CPU执行到该地址的指令时,会触发调试中断(断点),让程序暂停------这是调试器(比如GDB)实现"断点调试"的底层原理。

三、寄存器如何组成更复杂的电路?从寄存器组到流水线寄存器

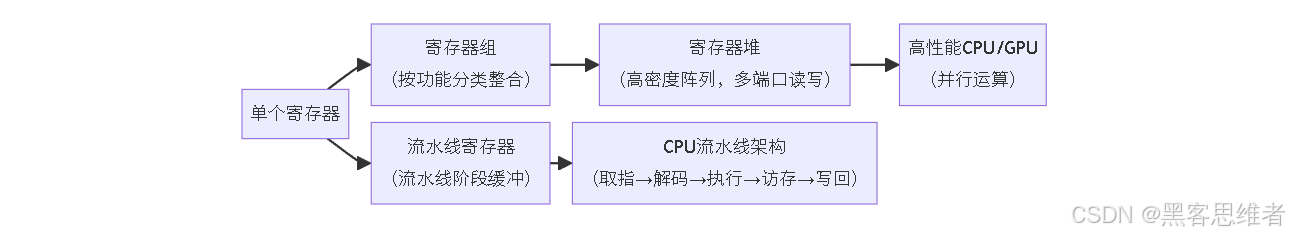

单个寄存器只能存储一组多位数据,而CPU需要同时处理"指令、数据、状态、地址"等多种信息,这就需要把多个不同类型的寄存器"组合起来",构建出寄存器组、流水线寄存器、寄存器堆等复杂电路,支撑CPU的完整工作流程。

1. 寄存器组:CPU的"寄存器集群",按功能分类整合

寄存器组是最基础的复杂电路,核心是"将不同功能的寄存器按类别整合",由控制单元统一调度,实现数据的协同传输。比如x86架构的寄存器组,按功能分为三大类:

-

通用寄存器组:整合EAX、EBX、ECX等8个通用寄存器,用于存储数据和地址;

-

指令相关寄存器组:整合PC、IR、FLAGS等寄存器,支撑"取指→解码→执行→写回"的指令执行流程;

-

内存管理寄存器组:整合CR0-CR4、段寄存器等,负责内存地址转换和内存保护。

控制单元通过"寄存器选择信号",决定在某一时刻哪个寄存器与ALU、内存进行数据交换------比如执行加法指令时,控制单元选择EAX和EBX作为输入,将它们的数据传输到ALU的全加器,运算结果再写回EAX。

2. 流水线寄存器:支撑CPU流水线技术的核心组件

现代CPU都采用"流水线技术"(比如5级流水线:取指→解码→执行→访存→写回),让多条指令能并行执行(比如指令1在执行时,指令2在解码,指令3在取指),大幅提升CPU吞吐量。而流水线寄存器就是"流水线各阶段之间的缓冲器",核心作用是"存储前一阶段的处理结果,供下一阶段使用",避免不同阶段的指令相互干扰。

-

组成逻辑:在流水线的每个阶段之间插入一组寄存器(比如取指→解码之间插入"取指-解码寄存器"),每个寄存器存储对应阶段的关键信息(比如指令内容、操作数地址、状态标志);

-

工作逻辑:每个时钟周期,流水线寄存器会将前一阶段的结果"同步传输"到下一阶段,同时接收当前阶段的新结果------比如取指阶段读取指令后,存入"取指-解码寄存器";时钟周期结束时,该寄存器将指令传输到解码阶段,同时取指阶段读取下一条指令存入该寄存器;

-

核心价值:让流水线各阶段能独立工作,不受其他阶段的延迟影响------比如执行阶段的加法运算耗时较长,不会阻塞取指和解码阶段的工作,提升整体效率。

3. 寄存器堆:高密度通用寄存器阵列,提升并行处理能力

在高性能CPU(比如CPU、GPU)中,需要大量通用寄存器来支撑多任务、多数据的并行处理,这就需要"寄存器堆"------由大量通用寄存器组成的高密度阵列,采用"多端口读写"设计,支持同时读取多个寄存器的数据,供多个运算单元(比如多个全加器)并行使用。

-

组成逻辑:由几百个甚至几千个64位通用寄存器组成,每个寄存器有唯一的地址;配备多个读写端口(比如8个读端口、4个写端口);

-

工作逻辑:控制单元通过"寄存器地址"选择要读写的寄存器,多个端口可同时操作不同的寄存器------比如GPU的寄存器堆,可同时为8个像素着色器提供数据,让8个运算单元并行运算;

-

适用场景:CPU、GPU、DSP等需要高强度并行运算的芯片。

四、寄存器在计算机系统中的核心应用:连接运算与存储的"桥梁"

寄存器的核心价值是"解决运算单元与内存的速度鸿沟",它的应用贯穿了CPU执行程序的全过程,是连接运算(ALU)、存储(内存)、控制(CU)的核心枢纽。我们列举几个关键应用场景,帮你理解它的不可替代性:

1. 支撑指令执行的全流程:从取指到写回的"数据载体"

CPU执行一条指令(比如int c = a + b),每个阶段都离不开寄存器:

-

取指阶段:PC存储指令地址,CPU根据PC读取指令,存入IR;

-

解码阶段:解码器解读IR中的指令,确定需要读取a和b的值,控制单元选择对应的通用寄存器(比如EAX存储a,EBX存储b);

-

执行阶段:ALU的全加器从EAX和EBX读取数据,完成加法运算,结果存入EAX;

-

写回阶段:控制单元将EAX中的结果写入内存(c的地址),同时更新FLAGS寄存器的标志位(比如判断是否溢出);

-

后续指令:PC自动递增,指向 next 指令,重复上述流程。

可以说,没有寄存器,指令的执行流程就无法推进------运算单元没有数据可算,内存数据无法高效传输,CPU根本无法工作。

2. 提升运算效率:减少内存访问,降低延迟

这是寄存器最核心的应用价值。我们用一组数据直观感受:假设全加器运算一次需要1纳秒,内存读写一次需要50纳秒;如果计算c = (a + b) + (d + e):

-

无寄存器场景:需要4次内存读取(a、b、d、e)、2次运算、1次内存写入(c),总耗时=4×50 + 2×1 + 1×50 = 252纳秒;

-

有寄存器场景:先将a、b、d、e读入寄存器(4×50=200纳秒),然后在寄存器之间完成2次运算(2×1=2纳秒),最后写入内存(50纳秒);但如果后续还有基于c的运算,c可留在寄存器中,无需再次读取------总耗时大幅降低,且后续运算效率更高。

现代编译器的"寄存器分配优化",就是尽量让数据在寄存器中流转,减少内存访问------这是提升程序运行速度的核心优化手段之一。

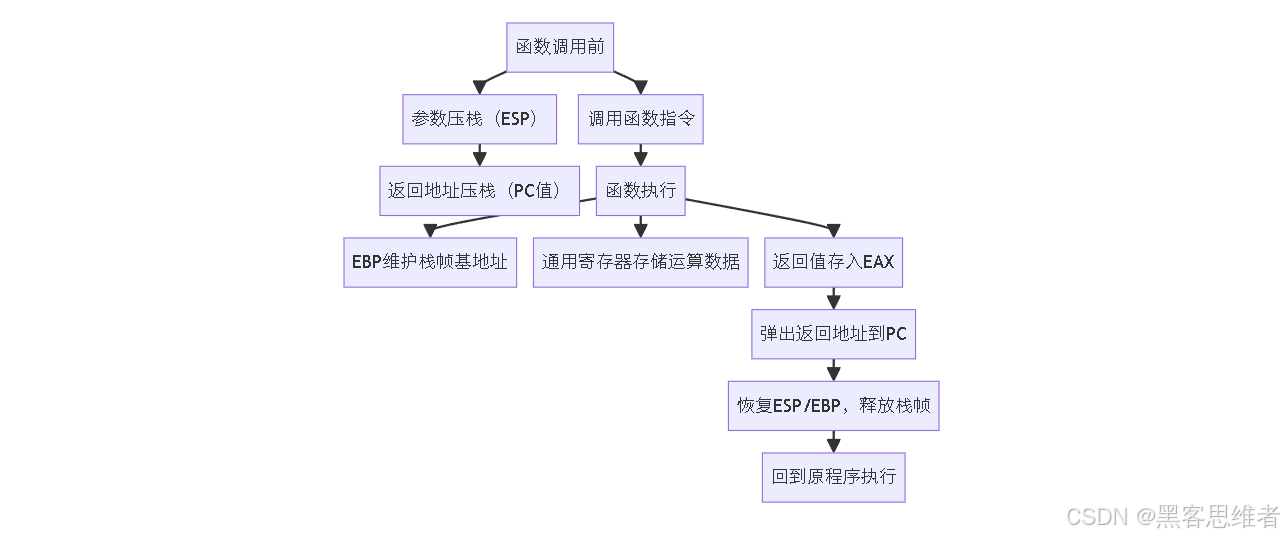

3. 实现函数调用与栈管理:保障程序的模块化执行

我们写代码时的函数调用(比如func(a, b)),背后全靠寄存器和栈配合实现:

-

函数调用前:将函数参数(a、b)压入栈(ESP控制栈顶地址),同时将"函数返回地址"(当前PC的值,即函数调用后要执行的下一条指令地址)压入栈;

-

函数执行时:EBP作为栈帧基地址,通过EBP+偏移量访问函数的参数和局部变量(局部变量存储在栈中);通用寄存器存储函数内部的运算数据;

-

函数返回时:将函数返回值存入EAX,弹出栈中的返回地址到PC(CPU跳回原程序继续执行),调整ESP和EBP的值,释放函数栈帧。

可以说,寄存器是函数调用的"核心调度者",没有它,程序的模块化执行(函数调用、多函数协作)就无法实现。

4. 支持调试与系统安全:保障程序开发与系统稳定

寄存器在程序调试和系统安全中也扮演着关键角色:

-

调试场景:调试寄存器(DR0-DR7)存储断点地址,当CPU执行到断点指令时,触发调试中断,程序暂停;调试器(比如GDB)可读取此时所有寄存器的值(比如EAX、EBX、PC),帮程序员定位问题(比如查看运算结果是否正确、程序跳转到了哪里);

-

系统安全场景:控制寄存器(CR0-CR4)控制CPU的工作模式和内存保护机制,比如开启内存分页后,不同程序的内存地址相互隔离,一个程序无法访问另一个程序的内存------这是多任务操作系统安全稳定运行的核心保障。

五、寄存器与编程:理解底层,才能写出更"高效、安全"的代码

很多程序员觉得"寄存器是编译器和操作系统的事,和我无关",但实际上,寄存器的底层逻辑直接影响代码的运行效率、安全性和调试难度。理解寄存器,能帮你避开很多编程中的"坑",写出更贴合硬件的高效代码。

1. 为什么"频繁使用的变量要定义为局部变量"?------寄存器分配优化

局部变量默认存储在栈内存,但编译器会优先将"频繁使用的局部变量"分配到通用寄存器(比如循环变量、累加器);而全局变量存储在堆内存,编译器通常不会将其分配到寄存器(因为全局变量可能被其他函数修改,寄存器中的值无法实时同步)。

临时运算 局部变量 动态数据 是 否 CPU执行指令 寄存器加载运算数据 数据类型? 寄存器直接运算 栈分配内存 堆分配内存 寄存器引用栈地址 栈存储堆指针 寄存器引用栈中指针 运算完成 函数返回 栈自动释放 堆数据使用完毕? 手动释放堆内存 寄存器继续操作 程序继续执行 程序结束

编程启示:循环内、高频运算的变量,尽量定义为局部变量------让编译器能将其分配到寄存器,减少内存访问,提升效率。比如:

c

// 低效:全局变量,难以被分配到寄存器

int g_sum = 0;

void add() {

for (int i = 0; i < 1000000; i++) {

g_sum += i; // 每次都要访问内存

}

}

// 高效:局部变量,易被分配到寄存器

int add() {

int sum = 0; // 大概率被分配到EAX

for (int i = 0; i < 1000000; i++) {

sum += i; // 寄存器内运算,速度极快

}

return sum;

}2. 为什么"函数参数不宜过多"?------寄存器传参的限制

函数调用时,参数的传递优先使用寄存器(速度快),只有当参数数量超过寄存器数量时,才会使用栈传参(速度慢)。比如x86-64架构中,前6个函数参数会通过RDI、RSI、RDX、RCX、R8、R9这6个寄存器传递,第7个及以后的参数才会压入栈。

编程启示:函数参数尽量控制在6个以内------减少栈传参的次数,提升函数调用效率。如果参数过多,可将参数封装为结构体(通过指针传递,指针占1个寄存器)。

3. 为什么"多线程共享变量需要加锁"?------寄存器缓存的问题

多线程共享变量时,每个线程的CPU核心会将变量从内存读取到自己的寄存器缓存(寄存器组的临时缓存);当一个线程修改了变量的值(写入寄存器缓存),还没来得及同步回内存时,另一个线程读取的还是旧的内存值(或自己缓存的旧值),导致"数据不一致"。

编程启示:多线程共享变量必须加锁(比如mutex)或使用原子类型(atomic)------加锁会强制线程修改后同步回内存,其他线程读取时从内存重新加载;原子类型则通过硬件指令保证寄存器与内存的同步,避免数据不一致。

4. 调试时如何通过寄存器定位问题?------理解寄存器的调试价值

调试程序时,查看寄存器的值能帮你快速定位问题:

-

查看PC寄存器:知道程序当前执行到了哪个地址的指令,判断是否出现"死循环""错误跳转";

-

查看EAX寄存器:如果函数返回值异常,查看EAX(函数返回值存储位置),判断是运算错误还是返回值传递错误;

-

查看FLAGS寄存器:如果条件跳转异常(比如if判断失效),查看ZF(零标志)、CF(进位标志),判断上一次运算的状态是否符合预期。

六、寄存器是"CPU效率的核心瓶颈之一"

以前写代码时,我只知道"局部变量快、参数少更快",但不知道背后是寄存器在起作用。现在明白:寄存器的数量和使用效率,直接决定了CPU的运算效率------这也是为什么x86-64架构要扩展寄存器数量(从8个到16个),为什么编译器的"寄存器分配算法"是核心优化点之一。

寄存器的核心价值,在于"作为运算与存储之间的高速缓冲"------它弥补了ALU运算速度与内存读写速度的鸿沟,让CPU的运算能力充分发挥。从1个触发器到1个寄存器,再到寄存器组、流水线寄存器,本质都是"通过硬件结构优化,减少数据传输延迟,提升整体效率"------这也是计算机体系结构设计的核心思想:平衡各组件的速度,让整体效率最大化。

理解寄存器,不是为了设计CPU,而是为了"更精准地把握代码的运行规律":知道如何通过变量定义、函数设计提升代码效率,知道如何通过调试寄存器定位底层问题,知道多线程数据不一致的根源------这些底层认知,是从"会写代码"到"写好代码"的关键。