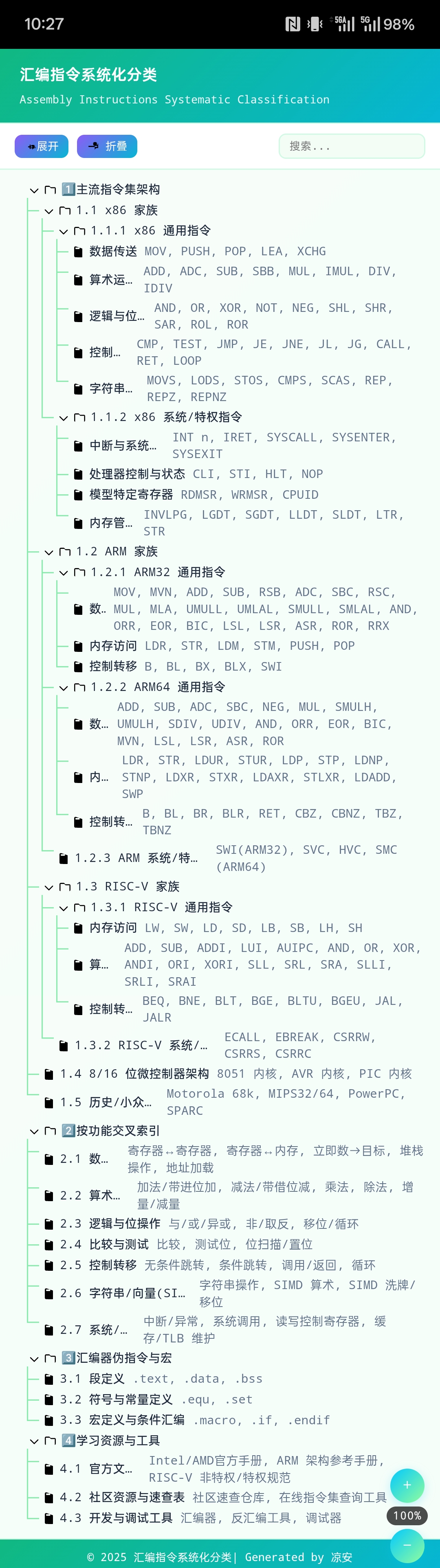

汇编指令系统化分类

一、 主流指令集架构

1. x86 家族

1.1 x86 通用指令

1.1.1 数据传送

- MOV, PUSH, POP, LEA, XCHG

1.1.2 算术运算

- ADD, ADC, SUB, SBB, MUL, IMUL, DIV, IDIV

1.1.3 逻辑与位操作

- AND, OR, XOR, NOT, NEG, SHL, SHR, SAR, ROL, ROR

1.1.4 控制转移

- CMP, TEST, JMP, JE, JNE, JL, JG, CALL, RET, LOOP

1.1.5 字符串操作

- MOVS, LODS, STOS, CMPS, SCAS, REP, REPZ, REPNZ

1.2 x86 系统/特权指令

1.2.1 中断与系统调用

- INT n, IRET, SYSCALL, SYSENTER, SYSEXIT

1.2.2 处理器控制与状态

- CLI, STI, HLT, NOP

1.2.3 模型特定寄存器

- RDMSR, WRMSR, CPUID

1.2.4 内存管理

- INVLPG, LGDT, SGDT, LLDT, SLDT, LTR, STR

2. ARM 家族

2.1 ARM32 (AArch32) 通用指令

2.1.1 数据处理

-

MOV, MVN, ADD, SUB, RSB, ADC, SBC, RSC

-

MUL, MLA, UMULL, UMLAL, SMULL, SMLAL

-

AND, ORR, EOR, BIC, LSL, LSR, ASR, ROR, RRX

2.1.2 内存访问

- LDR, STR, LDM, STM, PUSH, POP

2.1.3 控制转移

- B, BL, BX, BLX, SWI

2.2 ARM64 (AArch64) 通用指令

2.2.1 数据处理

-

ADD, SUB, ADC, SBC, NEG

-

MUL, SMULH, UMULH, SDIV, UDIV

-

AND, ORR, EOR, BIC, MVN, LSL, LSR, ASR, ROR

2.2.2 内存访问

-

LDR, STR, LDUR, STUR, LDP, STP, LDNP, STNP

-

LDXR, STXR, LDAXR, STLXR, LDADD, SWP

2.2.3 控制转移

- B, BL, BR, BLR, RET, CBZ, CBNZ, TBZ, TBNZ

2.3 ARM 系统/特权指令

- SWI (ARM32), SVC, HVC, SMC (ARM64)

3. RISC-V 家族

3.1 RISC-V 通用指令 (RV32I/RV64I 基础扩展)

3.1.1 内存访问 (Load/Store)

- LW, SW, LD, SD, LB, SB, LH, SH

3.1.2 算术与逻辑

-

ADD, SUB, ADDI, LUI, AUIPC

-

AND, OR, XOR, ANDI, ORI, XORI

-

SLL, SRL, SRA, SLLI, SRLI, SRAI

3.1.3 控制转移

-

BEQ, BNE, BLT, BGE, BLTU, BGEU

-

JAL, JALR

3.2 RISC-V 系统/特权指令

- ECALL, EBREAK, CSRRW, CSRRS, CSRRC

4. 8/16 位微控制器架构

-

8051 内核

-

AVR 内核

-

PIC 内核

5. 历史/小众架构

-

Motorola 68k

-

MIPS32/64

-

PowerPC

-

SPARC

二、 按功能交叉索引

2.1 数据传送

-

**寄存器↔寄存器**: MOV (x86), MOV (ARM)

-

**寄存器↔内存**: MOV (x86), LDR/STR (ARM), LW/SW (RISC-V)

-

**立即数→目标**: MOV (x86), LDR (ARM), ADDI (RISC-V)

-

**堆栈操作**: PUSH/POP (x86/ARM32), PUSH/POP (ARM64伪指令)

-

**地址加载**: LEA (x86), LDR (ARM,伪指令), LUI/AUIPC (RISC-V)

2.2 算术运算

-

**加法/带进位加**: ADD/ADC (x86/ARM/RISC-V)

-

**减法/带借位减**: SUB/SBB (x86), SUB/SBC (ARM), SUB (RISC-V)

-

**乘法**: MUL/IMUL (x86), MUL/UMULL/SMULL (ARM), MUL (RISC-V)

-

**除法**: DIV/IDIV (x86), SDIV/UDIV (ARM), (RISC-V M扩展)

-

**增量/减量**: INC/DEC (x86), (ARM/RISC-V 通常用 ADD/SUB #1 实现)

2.3 逻辑与位操作

-

**与/或/异或**: AND/OR/XOR (x86/ARM/RISC-V)

-

**非/取反**: NOT/NEG (x86), MVN (ARM), (RISC-V 通常用 XOR -1 实现)

-

**移位/循环**: SHL/SHR/SAR/ROL/ROR (x86), LSL/LSR/ASR/ROR (ARM), SLL/SRL/SRA (RISC-V)

2.4 比较与测试

-

**比较**: CMP (x86/ARM), (RISC-V 通常用 SUB/SLT 实现)

-

**测试位**: TEST (x86), (ARM/RISC-V 通常用 ANDS 实现)

-

**位扫描/置位**: BSF/BSR/BTS (x86)

2.5 控制转移

-

**无条件跳转**: JMP (x86), B/BR (ARM), JAL/JALR (RISC-V)

-

**条件跳转**: Jcc (x86), Bcc (ARM), Bcc (RISC-V)

-

**调用/返回**: CALL/RET (x86), BL/RET (ARM), JAL/JALR/RET (RISC-V)

-

**循环**: LOOP (x86), (ARM/RISC-V 通常用组合指令实现)

2.6 字符串/向量 (SIMD)

-

**字符串操作**: MOVS/CMPS/SCAS (x86)

-

**SIMD 算术**: ADDPS/PMULLD (x86 SSE/AVX)

-

**SIMD 洗牌/移位**: SHUFPS/PSLLDQ (x86 SSE/AVX)

2.7 系统/特权

-

**中断/异常**: INT/IRET (x86), SWI/SVC (ARM), ECALL/EBREAK (RISC-V)

-

**系统调用**: SYSCALL/SYSENTER (x86), SVC (ARM), ECALL (RISC-V)

-

**读写控制寄存器**: MOV CRx/MSR (x86), CSRRW/CSRRS/CSRRC (RISC-V)

-

**缓存/TLB 维护**: INVLPG (x86), IC IALLU (ARM)

三、 汇编器伪指令与宏

3.1 段定义

- .text, .data, .bss

3.2 符号与常量定义

- .equ, .set

3.3 宏定义与条件汇编

- .macro, .if, .endif

四、 学习资源与工具

4.1 官方文档与手册

-

Intel/AMD 官方手册

-

ARM 架构参考手册

-

RISC-V 非特权/特权规范

4.2 社区资源与速查表

-

社区速查仓库

-

在线指令集查询工具

4.3 开发与调试工具

-

汇编器

-

反汇编工具

-

调试器