上篇是 :CRG- clock

目录

[1、CDC 检查使用spyglass 工具。](#1、CDC 检查使用spyglass 工具。)

[3、spyglass CDC 检查实现的功能:](#3、spyglass CDC 检查实现的功能:)

[4、spyglass 的CDC 检查流程](#4、spyglass 的CDC 检查流程)

[4.1、design setup](#4.1、design setup)

[4.2、goal setup](#4.2、goal setup)

[4.3、analyze results](#4.3、analyze results)

[5、batch mode](#5、batch mode)

1、CDC 检查使用spyglass 工具。

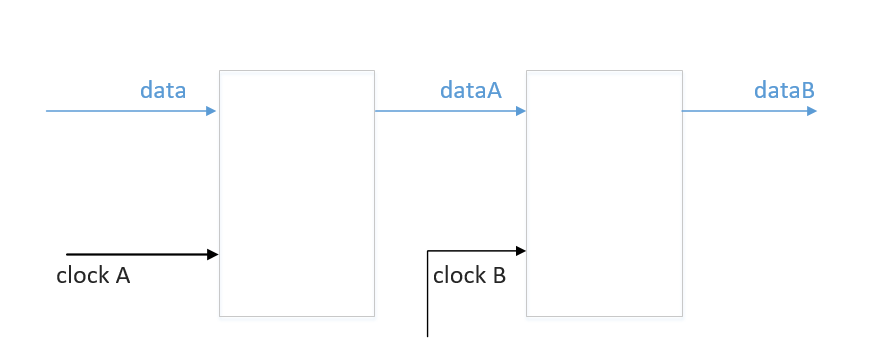

CDC 指 clock domains cross, 针对于异步时钟。

2、spyglass工具

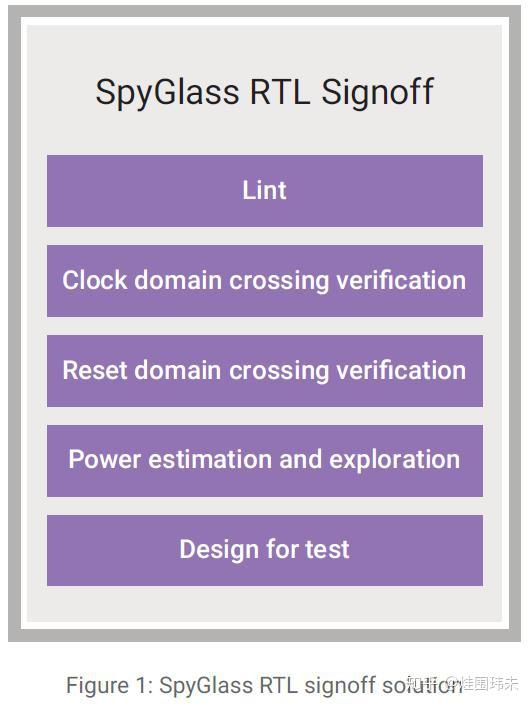

spyglass 是业界可靠的 RTL sign-off 解决方案,支持5个大模块

lint 、CDC、低功耗、约束、DFT

3、spyglass CDC 检查实现的功能:

完整性检查

确保时钟和复位信号的完整性,检查时钟门控是否采用无毛刺结构,避免时钟和复位信号在跨时钟域传递时出现竞争冒险问题。

同步检查

验证跨时钟域的控制信号和数据信号是否被正确同步。

检查未同步的跨时钟域问题,复位同步问题,以及快时钟域到慢时钟域时的数据保持时间是否足够。

重汇聚检查

检查多个信号从不同路径同步后在目的时钟域重新汇聚的问题,避免出现非预期的信号组合,确保多比特信号在跨时钟域传递时的数据一致性。

毛刺检查

检查组合逻辑跨时钟域时可能产生的毛刺问题,防止亚稳态传播到下游逻辑,造成系统功能错误。

协议验证

验证握手协议、FIFO等同步机制的完整性,确保跨时钟域通信的可靠性和正确性。

4、spyglass 的CDC 检查流程

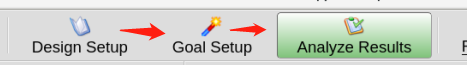

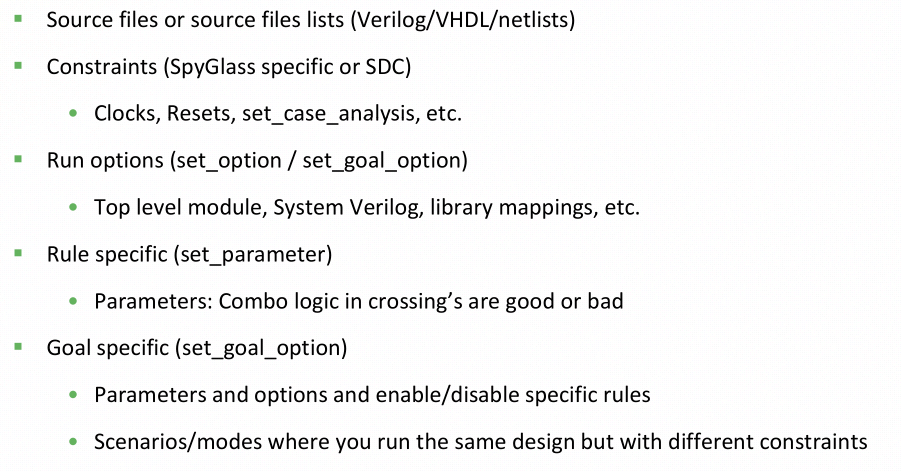

4.1、design setup

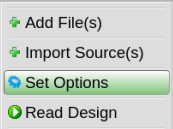

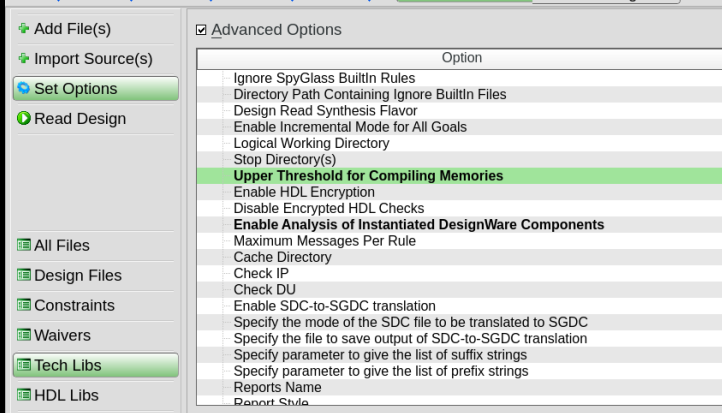

step1 添加设计文件、SGDC文件、预编译文件和技术文件。

在 Set Option中,指定影响SpyGlass运行的各种设计读取选项。例如,你可以在设计中 指定顶层模块、更改语言、指定宏等等。。

step2 运行read design 流程来执行第一级的HDL分析。在进入下一阶段之前,必须解决此阶段报告的致命错误(FATAL)。

source files: HDL文件 这些文件包括Verilog(.v、verilog和.sv)文件、VHDL(.vhdl和.vhd)文件、设计交换格式(.def)文件以及库交换格式(.lef)文件。

注意:如果指定了一个未知类型的文件,它将以红色显示,否则无法进入下一步。

tech libs:包含结构化网表所需的Synopsys.lib、.sglib、.plib和.gateslib文件,这些库单元用于 构建结构化网络列表。

waivers:

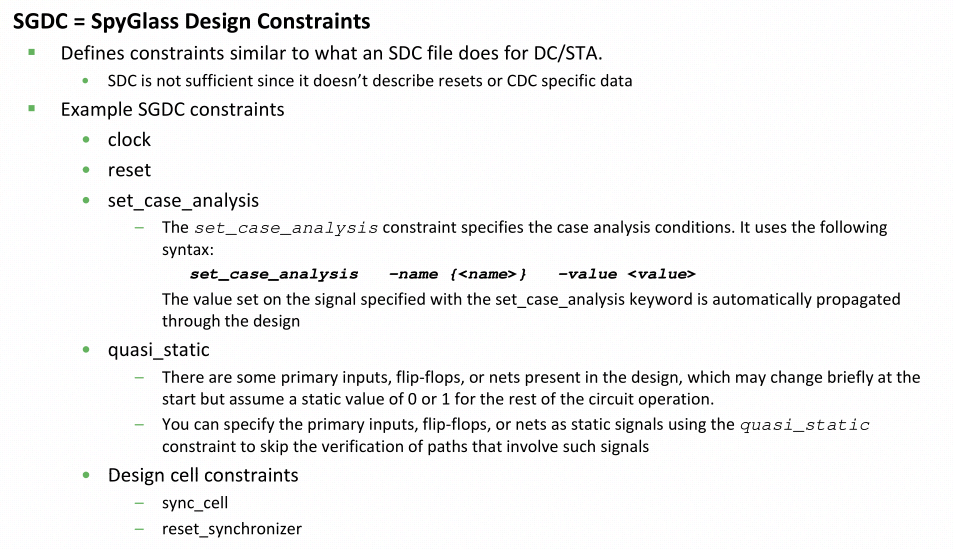

Constraints: SGDC文件 这些文件是包含SpyGlass设计约束的.sgdc文件。这些设计约束用于提供在RTL中无法显而易见的设计信息: clock、reset、

quasi_static 是SGDC(SpyGlass Design Constraints)约束文件中的一个重要属性,用于声明时钟或复位信号在仿真期间保持静态不变,从而简化CDC(跨时钟域)验证的复杂度。

主要作用

1. 减少误报:当某个时钟或复位信号在仿真期间始终保持不变时,SpyGlass会将其视为静态信号,避免产生不必要的CDC违例报告。

2. 提高验证效率:通过明确声明静态信号,SpyGlass可以跳过对这些信号的动态分析,加快验证速度。

3. 支持多模式验证:在需要验证不同时钟配置(如时钟门控、时钟切换)的场景下,quasi_static允许在特定模式下将某些时钟声明为静态。

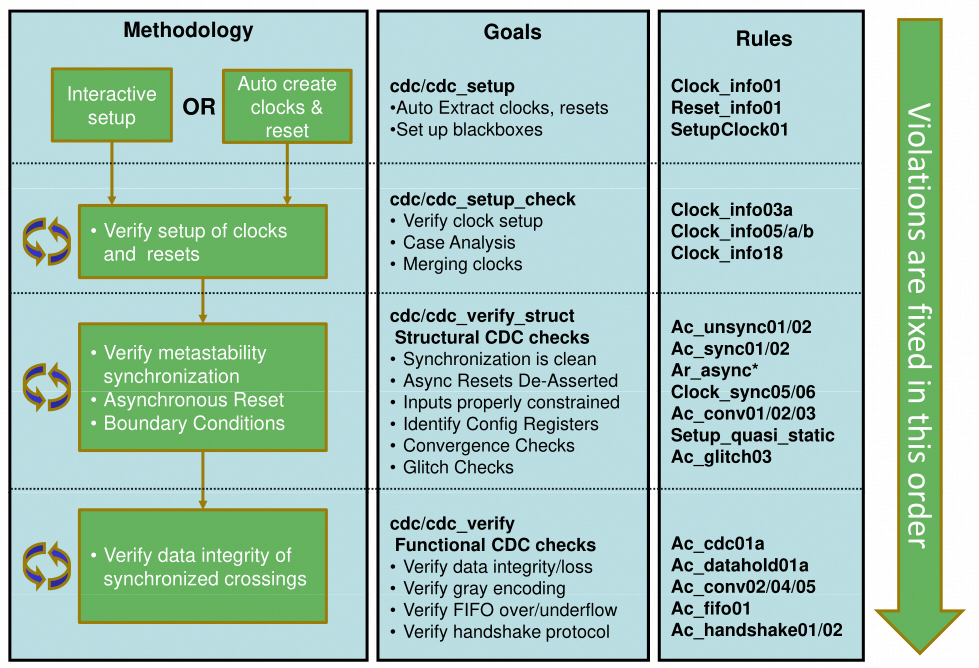

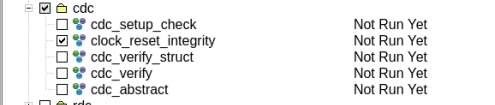

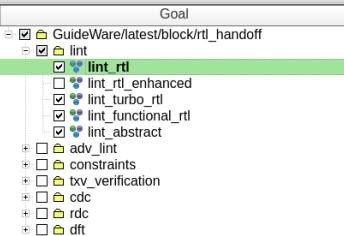

4.2、goal setup

目标是一些规则的集合,这个阶段设置目标,然后运行。

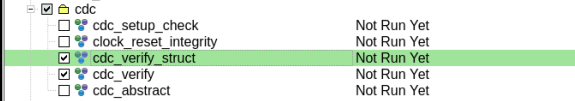

SpyGlass CDC 的目标和规则如下图所示:

extract: 提取。

cdc setup: extract 是 SpyGlass CDC 验证流程中的一个关键步骤,用于从设计文件中提取时钟、复位和跨时钟域路径信息,为后续的 CDC 检查做准备。

-

自动识别时钟和复位:extract 阶段会扫描整个 RTL 设计,自动推断出所有的时钟信号、复位信号及其属性(如周期、有效沿、同步/异步类型)。输出时钟域报告:列出所有时钟域及其属性

-

建立时钟域关系:分析时钟之间的频率比、相位关系,识别出所有跨时钟域CDC路径。

-

生成约束文件:自动创建

autoclock.sgdc和autoreset.sgdc文件,包含提取到的时钟和复位约束信息。 -

检查设计完整性:验证时钟和复位网络的完整性,检查是否存在时钟门控、时钟多路复用器等结构

4.2.1、指定设计信息:

在运行CDC验证之前指定设计信息,例如clock 、reset和停止模块。这些信息决定了SpyGlass CDC分析的质量。分为3部分:

- 将时钟生成模块指定为black box

- 为设计指定时钟和复位(为设计生成时钟和复位)

- 使用设置管理器

blackboxes: 将时钟生成模块(比如PLL) 标记为黑盒子,因为对它的内部执行SpyGlass CDC分析非常复杂,而且对整体SpyGlass CDC分析几乎没有价值。

一旦你设置这些模块为black boxes:

- 将时钟约束定义在这些模块的输出pin上

- 将输出时钟和输入定义为同一个时钟域,除非两者之间没有相位关系

为设计指定时钟和复位: 执行以下步骤来指定他们:

在SGDC中定义CLOCK和RESET的约束

clock -name "clk_sys"

reset -name "rst_n" --value 0

如果不知道设计中的时钟和复位,可以执行以下步骤来生成:

- 运行cdc_setup goal ------没找到

这个步骤产生了autoclocks.sgdc和autoresets.sgdc两个SGDC文件,包含了推断的时钟和复位。

- 检查和修改生成的SGDC文件

这些文件可能包括一些除了真正的时钟和复位的控制信号。因此,你必须检查,并删除不是真正的时钟和复位信号。

建议查看Setup_clock01和Reset_info01规则信息,以查看这样的推断信号。

- 在SpyGlass中指定修改过的autoclocks.sgdc 和 autoresets.sgdc文件,并通过运行相应的Goal来分析你的设计。

修复时钟和复位完整性问题:

运行clock_reset_integrity goal来修复时钟和复位的完整性。

4.3、analyze results

运行Goals,例如cdc_verify和cdc_verify_struct,以检测大量的CDC问题。

包括:

1、未同步的跨时钟域问题 、

2、聚合问题(Convergence Issues)、

3、复位同步问题、毛刺问题(glitch)、

4、跨时钟信号宽度错误(从快时钟穿到慢时钟)、

5、数据跨时钟的保持时间问题

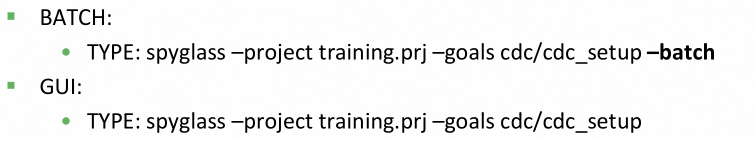

5、batch mode

如果spyglass 使用 batch mode,则会有一个project。

project 内容:filelist、 约束文件SDC、run option、 规则、目标

6、调试

搞不定了,下次再说吧