本教程主要针对,使用Supra新建Quartus工程并进行持续开发,而非只是工程转换教程,不需要使用EP4开发完再转换,直接使用AG10K上手开发。

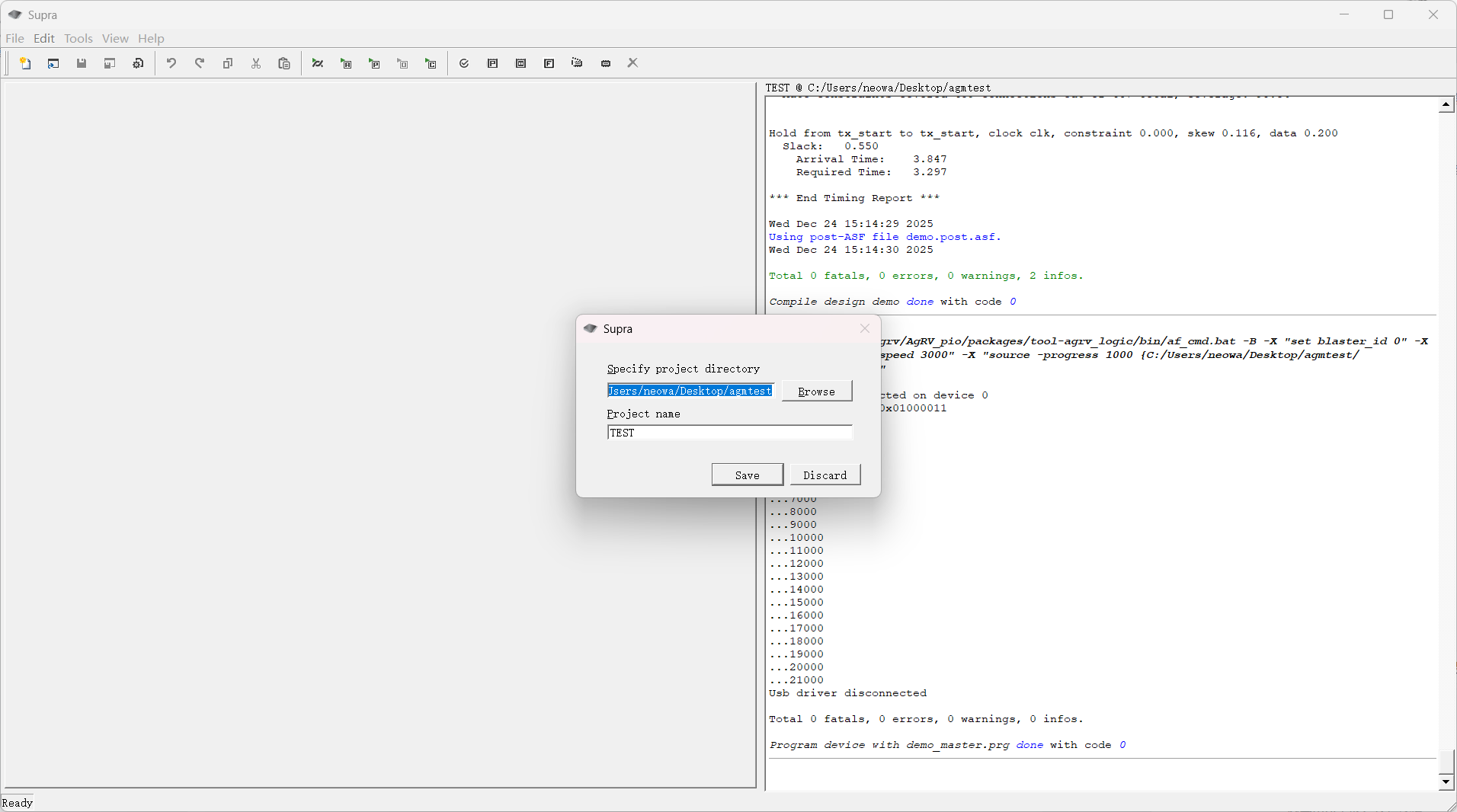

第一步,新建工程 File-> new project 选择路径并输入工程名称

第二步,进入Tools -> Migrate 界面。

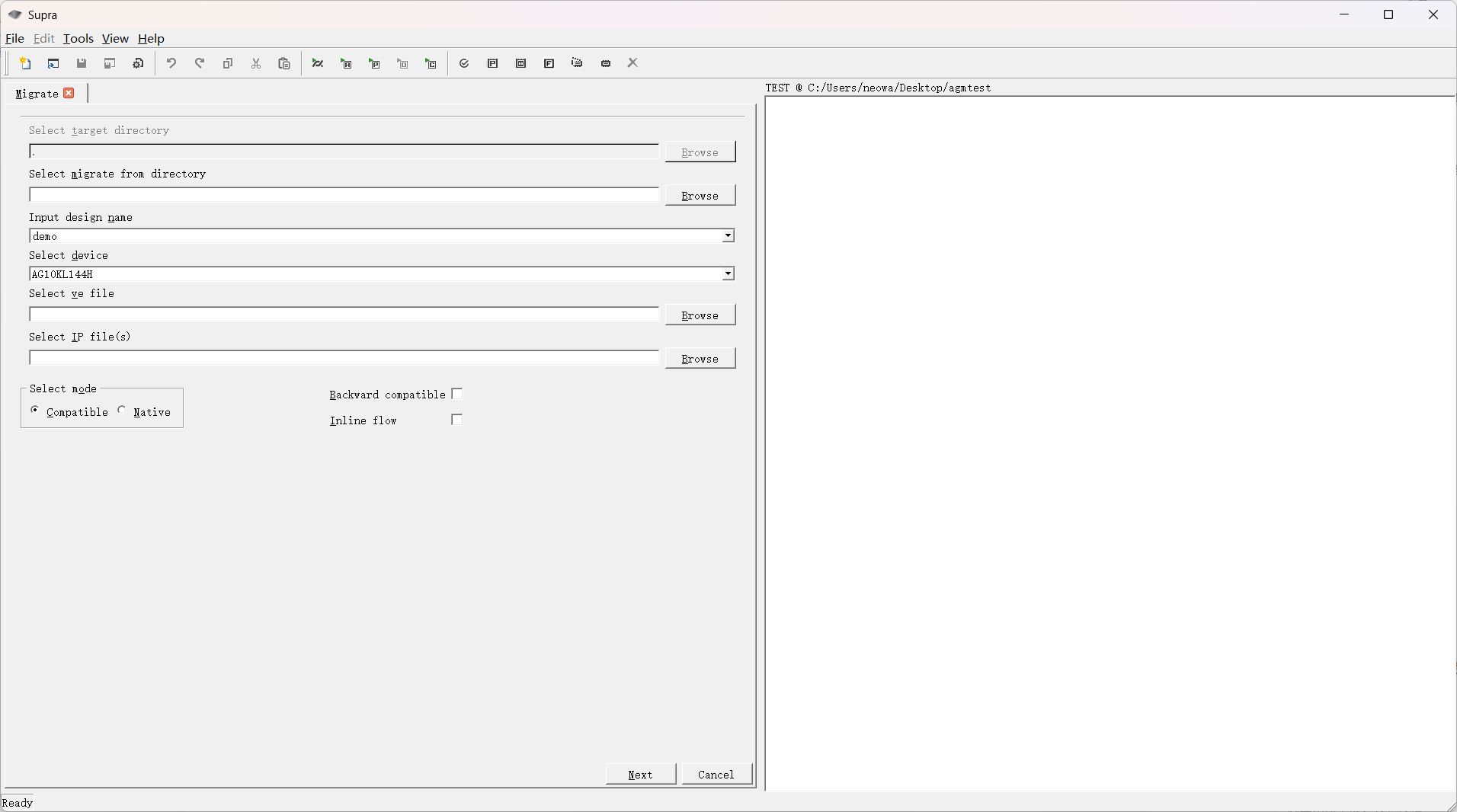

Select migrate from directory:不是工程转换,所以留空;

In put design name:直接从键盘输入名称,也就是你的quartus工程名称。

Select ve file:留空,这样子在Quartus工程里面绑定引脚即可,绑定后在Quartus编译(Start Compilation)后生效,不需要重新Migrate。

备注(ve不留空时需要注意的):除非你用的是非直接替换型号才需要指定VE,一旦指定VE,当VE文件修改后,则需要重新Migrate。每次migrate都会自动导入文件夹下全部v文件,包括生成的xxx_route.v这个文件会导致quartus编译失败,需要在quartus内移除这个文件。

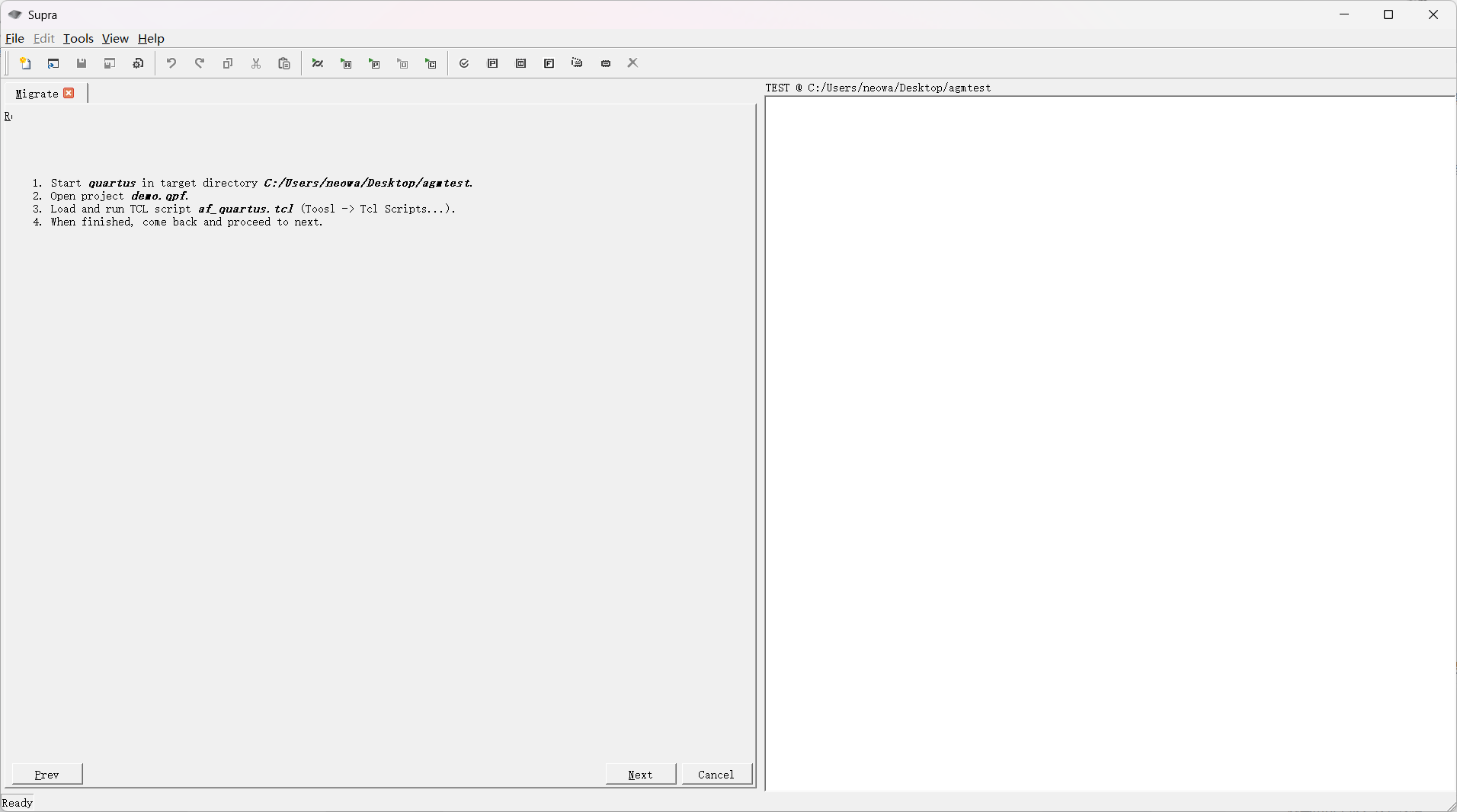

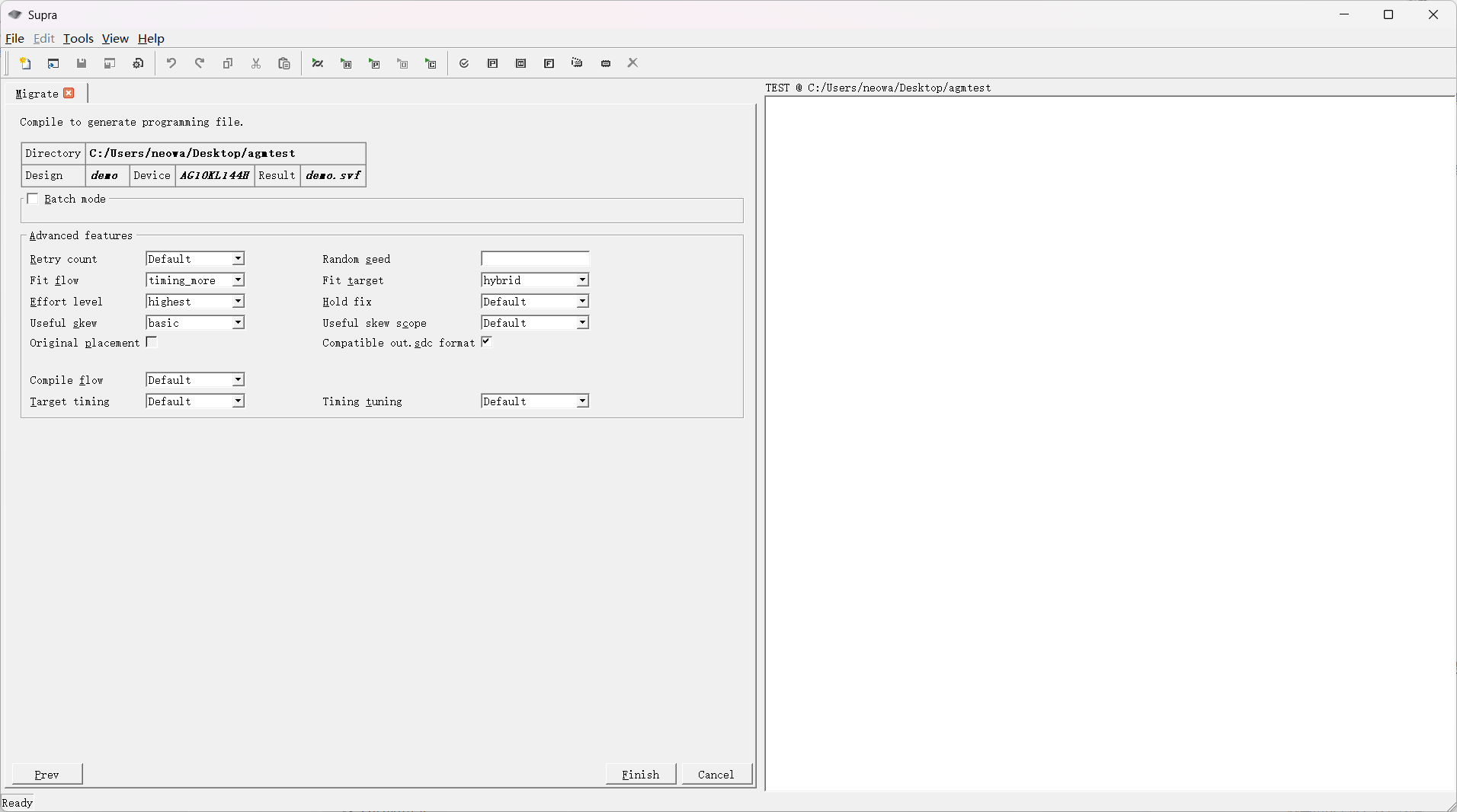

点击Next后,如下图:

第三步,出现上图界面时,打开工程目录找到生成的Quartus工程,点击启动Quartus,然后先简单编写一个v代码,和使用Pin Planner绑定引脚。

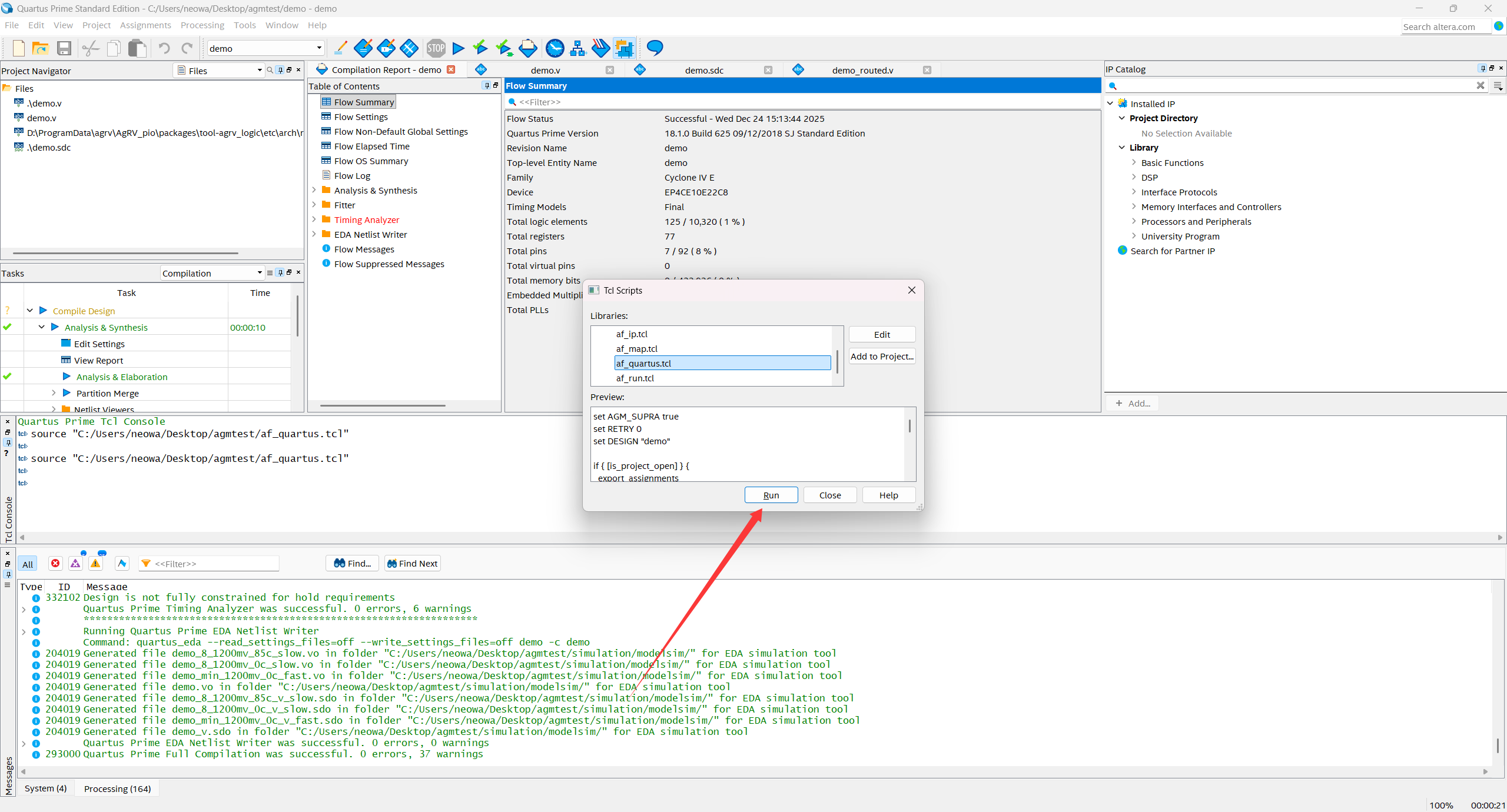

然后在Quartus内找到Tools-> Tcl Script... 然后选择 af_quartus.tcl然后点击run,运行结束后,返回Supra,再一次点击Next.

第四步:点击Finish即可对Quartus编译出来的vo文件进行布线。布线完成后会生成FPGA的烧录文件。

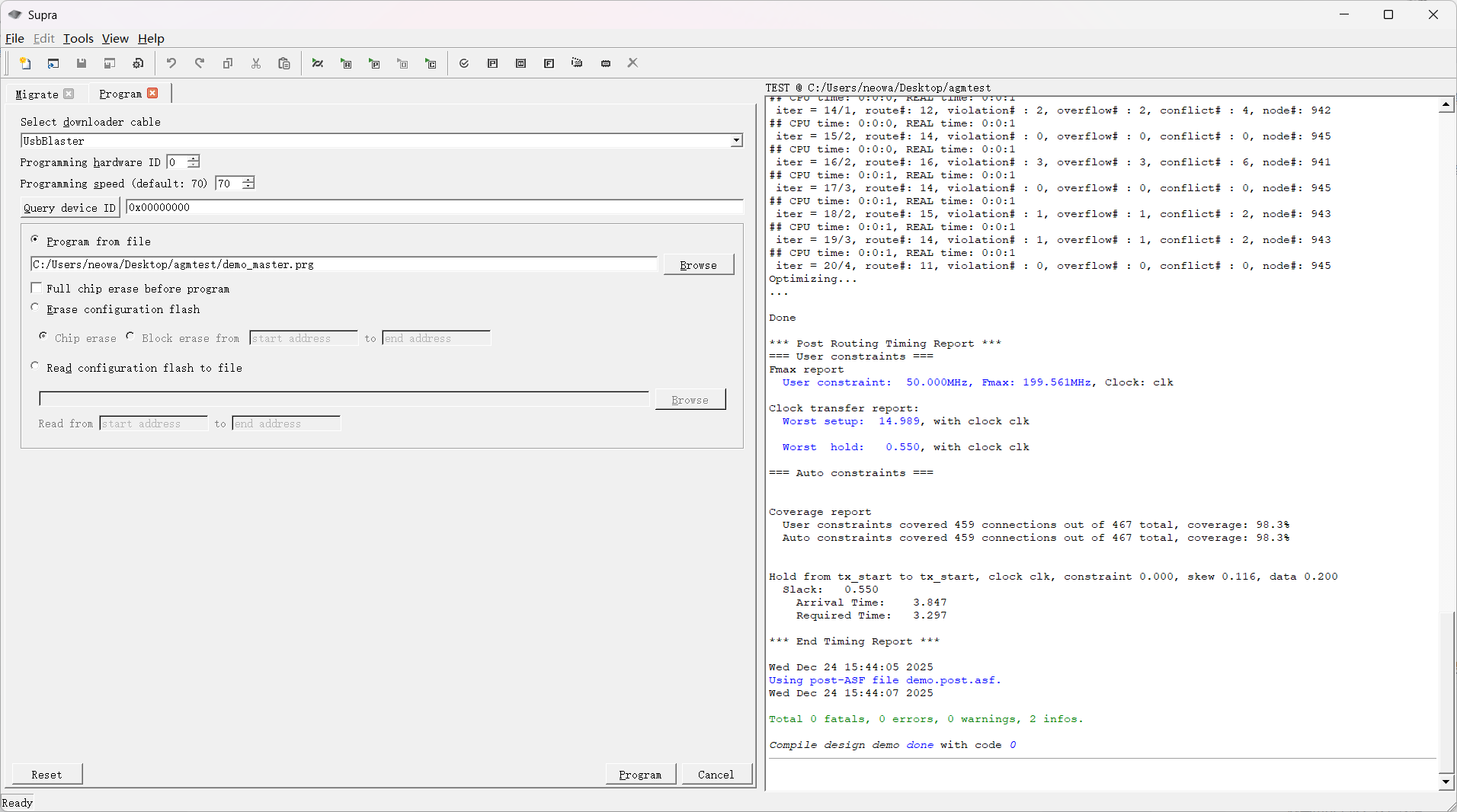

此后。引脚变动,只需要在Quartus的Pin Planner内绑定,然后重新编译。代码变动也是重新在Quartus编译,然后只在Supra内点击Tools - > Compile 然后点击Run即可生成最新的烧录文件。

第五步:烧录。点击Supra的 Tools -> Program,链接USB Blaster,选择布线出来的prg文件,然后点击Program即可。

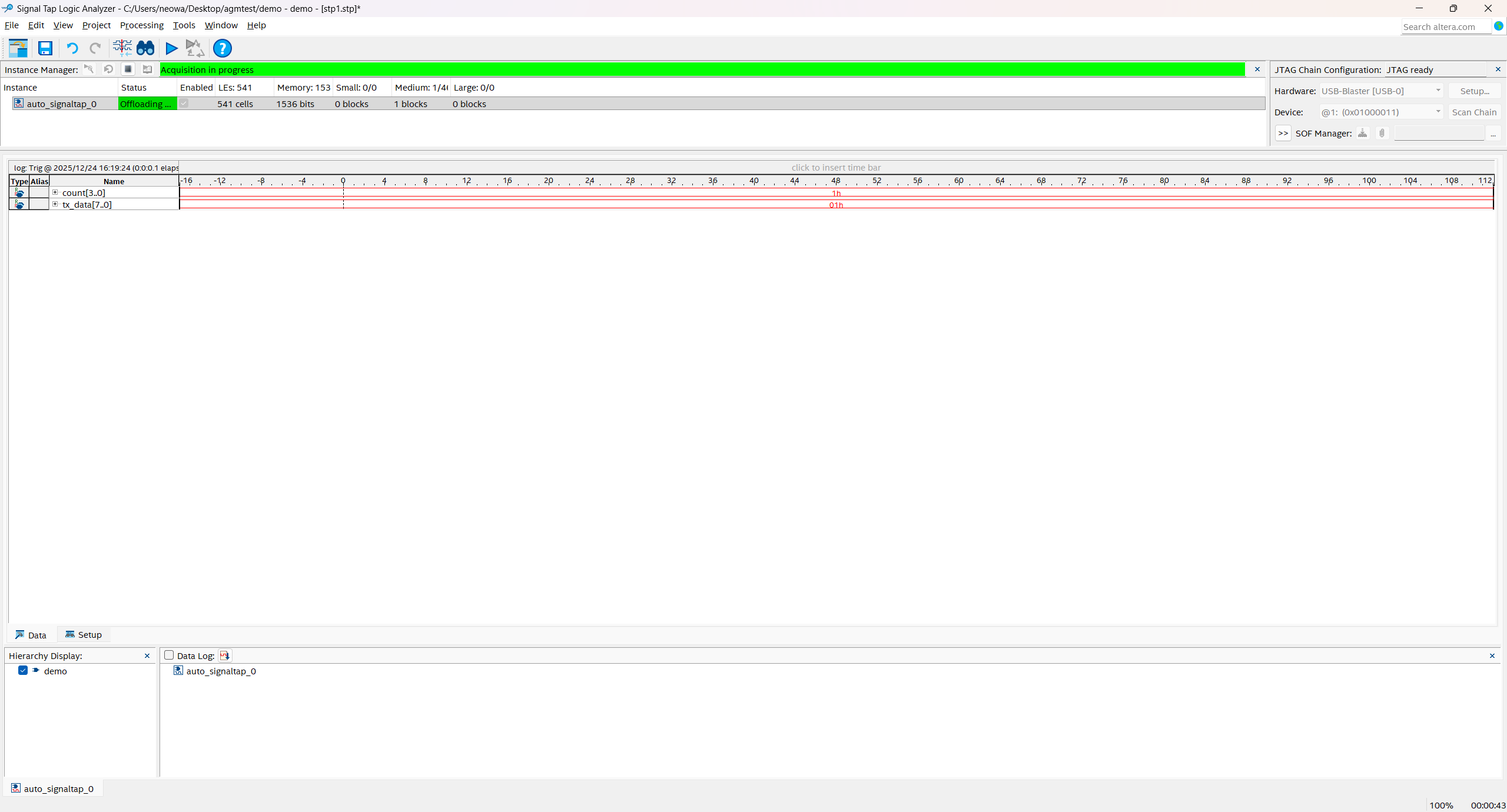

此外,Signal Top Logic均可正常使用