前言

长时间没有更新了,说明一下缘由:5月更新了上一篇博客之后,转头就去准备TI杯去了,之后8月底比完TI杯,就转头开始了考研路。昨天考完最后一门后,就马上把之前攒了两三个月的素材拿出来分享了。

锁相环(PLL)指的是利用鉴相器、环路滤波器、压控振荡器为核心组成的,控制内部信号与外部时钟源的相位和频率相同。基于此,大部分的电子设备或多或少都需要利用锁相环来保证内部的工作频率与外部时钟同频或是更加严格的同相,锁相环的利用也算是比较的广泛了。因此,Intel公司在quartus上专门集成了锁相环的模块,不需要我们具体去一一写鉴相器等模块了。(Vivado上应该也有对应的PLL模块)

一、目的

熟练配置和应用锁相环模块,并在之后的实例中使用。

二、配置步骤

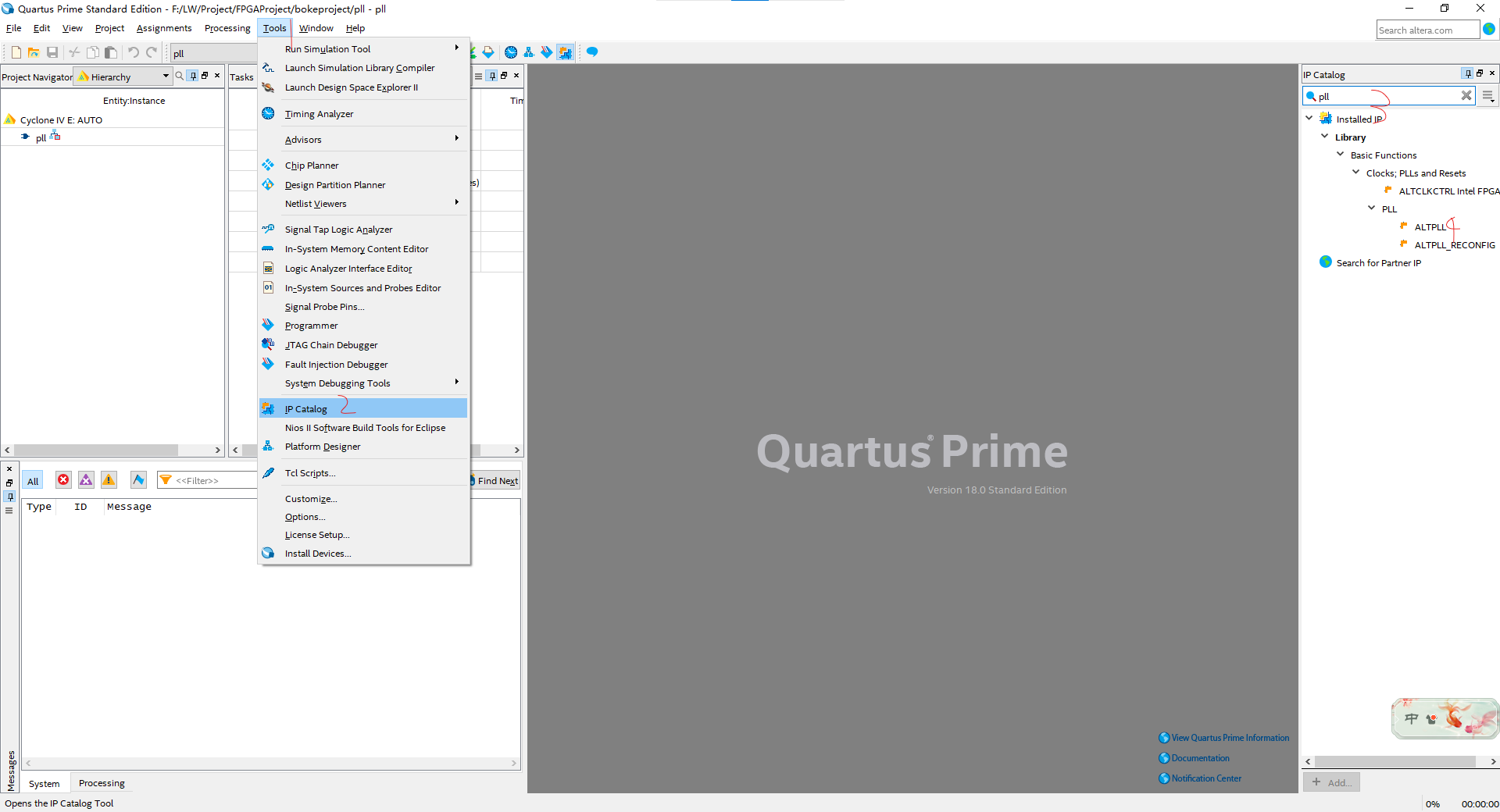

首先,要在菜单栏的工具(Tools)中找到IP Catalog(Alt+7),右侧会跳出IP Catalog窗口,在搜索栏里输入"pll",找到其中的"ALTPLL",如图。

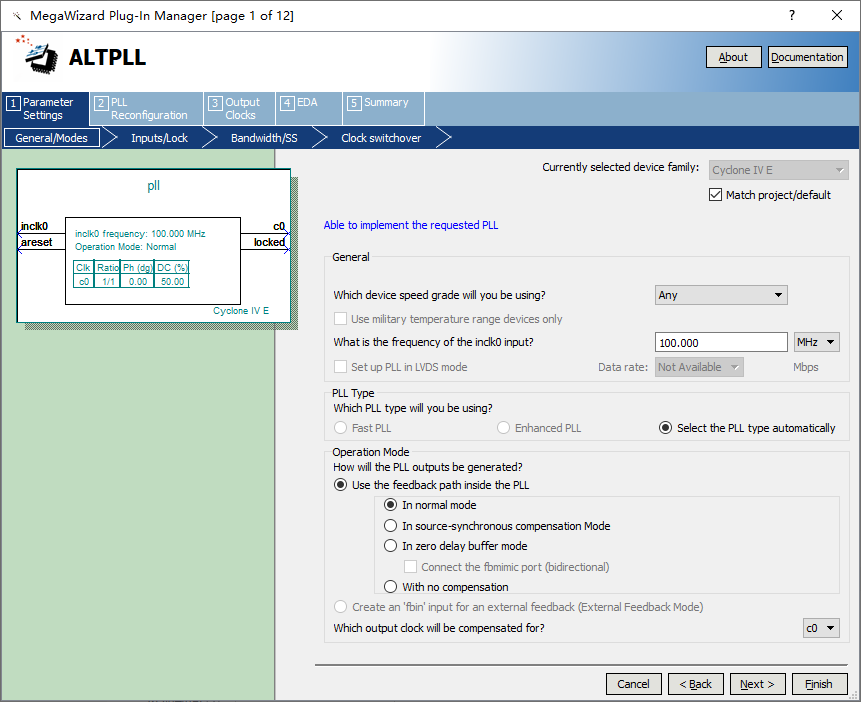

双击"ALTPLL",并(尽量)在工程项目目录下保存*.v的文件,之后会跳出窗口如下:

在这个窗口中,就有需要手动修改的地方。

1.Which device speed grade will you be using?这个与FPGA的芯片的最高可承受时钟速率相关,可以不动选择any,也可以下拉菜单栏选择自己FPGA芯片的速率型号。

2.What is the frequency of the inclk0 input?这个可以理解成外部的时钟晶振频率,即需要内部信号的频率相位基准,输入对应频率即可。

3.这页剩下的基本就可以不用管了,具体什么特殊作用还没尝试过,欢迎补充。

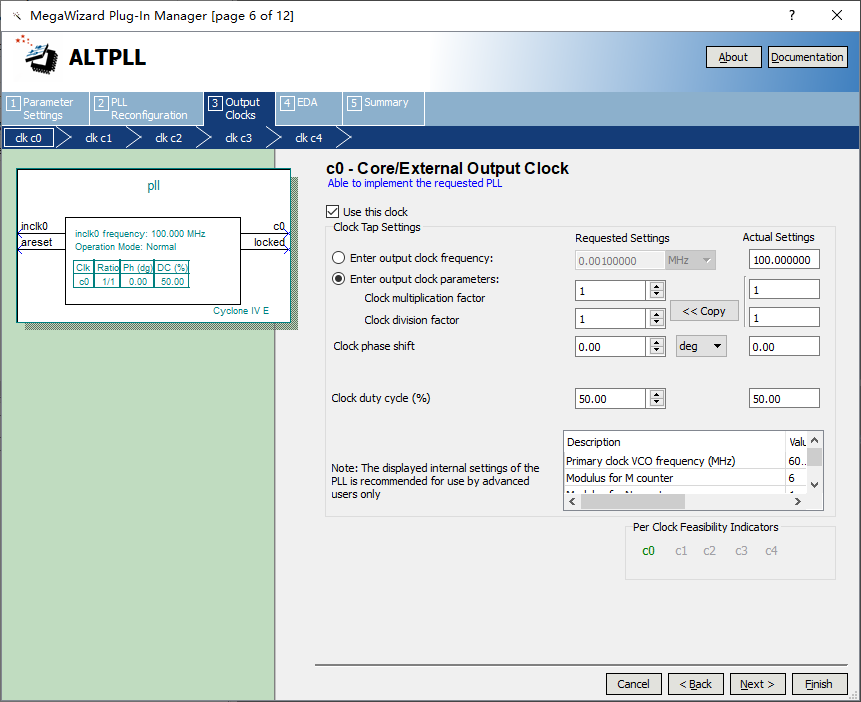

之后点击下一页(Next),一直点击,中间的具体特殊作用也没有尝试,欢迎补充。直到"Output Clocks"界面,如图。

这里就到了比较关键的输出对应需要精准控制的内部信号的环节了。Quartus的每个PLL有5中不同情况的信号可供配置,即可以看到在"Output Clocks"下一行的"clk c0""clk c1""clk c2""clk c3""clk c4"。

1.Use this clock这个是是否选用这个时钟信号,用就勾上,不用就把√去掉。

2.Enter output clock frequency和Enter output clock parameters是二选一的。选前者只需要在Requested Settings下输入想要的内部信号频率,经系统的计算,就能在Actual Settings下得到基于当前芯片的实际的能输出的频率;选择后者就需要自己手动在分频与倍频,Clock multiplication factor是倍频数,Clock division factor是分频数,二者可以同时作用,同样是在Requested Settings下输入,在Actual Settings下得到实际输出频率。

3.Clock phase shift是相位的偏移量,Requested Settings下输入需要的相移大小,在Actual Settings下得到实际的相位。

4.Clock duty cycle是占空比,Requested Settings下输入需要的占空比,在Actual Settings下得到实际的占空比。

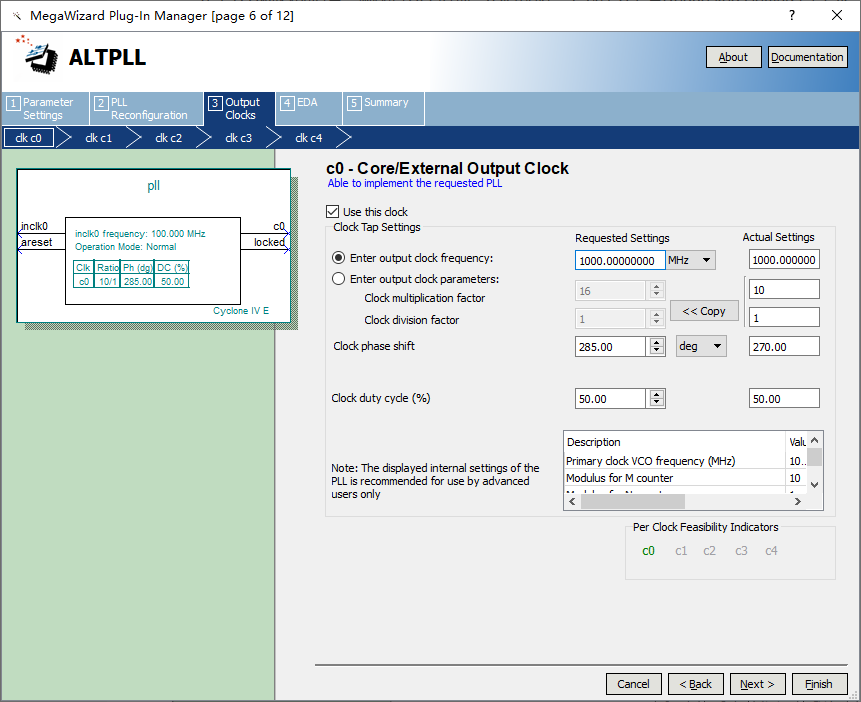

5.需要几种内部信号,就配置几个时钟。然后说明一下为什么会有Requested Settings(需求设置)和Actual Settings(实际设置)。分频、倍频、移相、占空比的操作都与计数器的计数脱不开关系。如果计数器的最大计数位数和计数频率足够高的话,频率精度、相位精度和占空比精度可以达到任何想要的值,但是受限于芯片自身的速率情况和内存大小,计数器的计数位数和计数频率不可能足够大,需要的相移和占空比的精度越高,计数器的精度就不足以支撑这几个参数的精度,具体情况如下图。

在100MHz输入频率下,配置1GHz频率的相位精读是不足5%的,占空比更是达到了只有50%的情况。由于频率上可以通过多次分频和倍频来操作,因此精度相对会高一点。配置完,点击Finish就可以了。

三、实例化

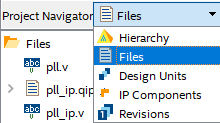

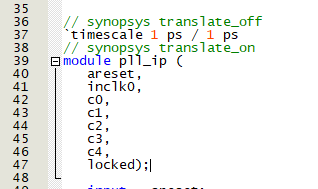

在实例化前,需要知道这个PLL的各个引脚的作用和功能。首先需要在菜单栏的view中的Utility Windows中找到Project Navigator(Alt+0),下拉Hierarchy换成Files,下拉*.qip,找到*.v并双击(*.qip和*.v是之前自己命名的PLL的文件,我的名字是pll_ip)。打开文件后就能看到系统生成的pll了,如图。

这里面的areset是复位引脚,inclk0是外部时钟输入引脚,c0-c4是内部锁相信号的输出引脚(配置了几个就会出现几个),locked是是否锁定,也就是是否能使用。将头上的这一段复制下来放到工程中,就能获得锁相信号了。

module pll(

input wire clk,

input wire rst,

output wire [4:0] d

);

wire clk0, clk1, clk2, clk3, clk4;

pll_ip my_pll(

.areset(rst),

.inclk0(clk),

.c0(clk0),

.c1(clk1),

.c2(clk2),

.c3(clk3),

.c4(clk4),

.locked()

);

assign d[4] = clk4;

assign d[3] = clk3;

assign d[2] = clk2;

assign d[1] = clk1;

assign d[0] = clk0;

endmodule 总结

锁相环在电子信息领域是一类相当常见的模块,影响着电子设备的正常稳定运行。FPGA中的锁相环也有不少我没有提及的强大功能,欢迎大家补充。