2.6 SCAN DESIGN RULES(scan设计规则)

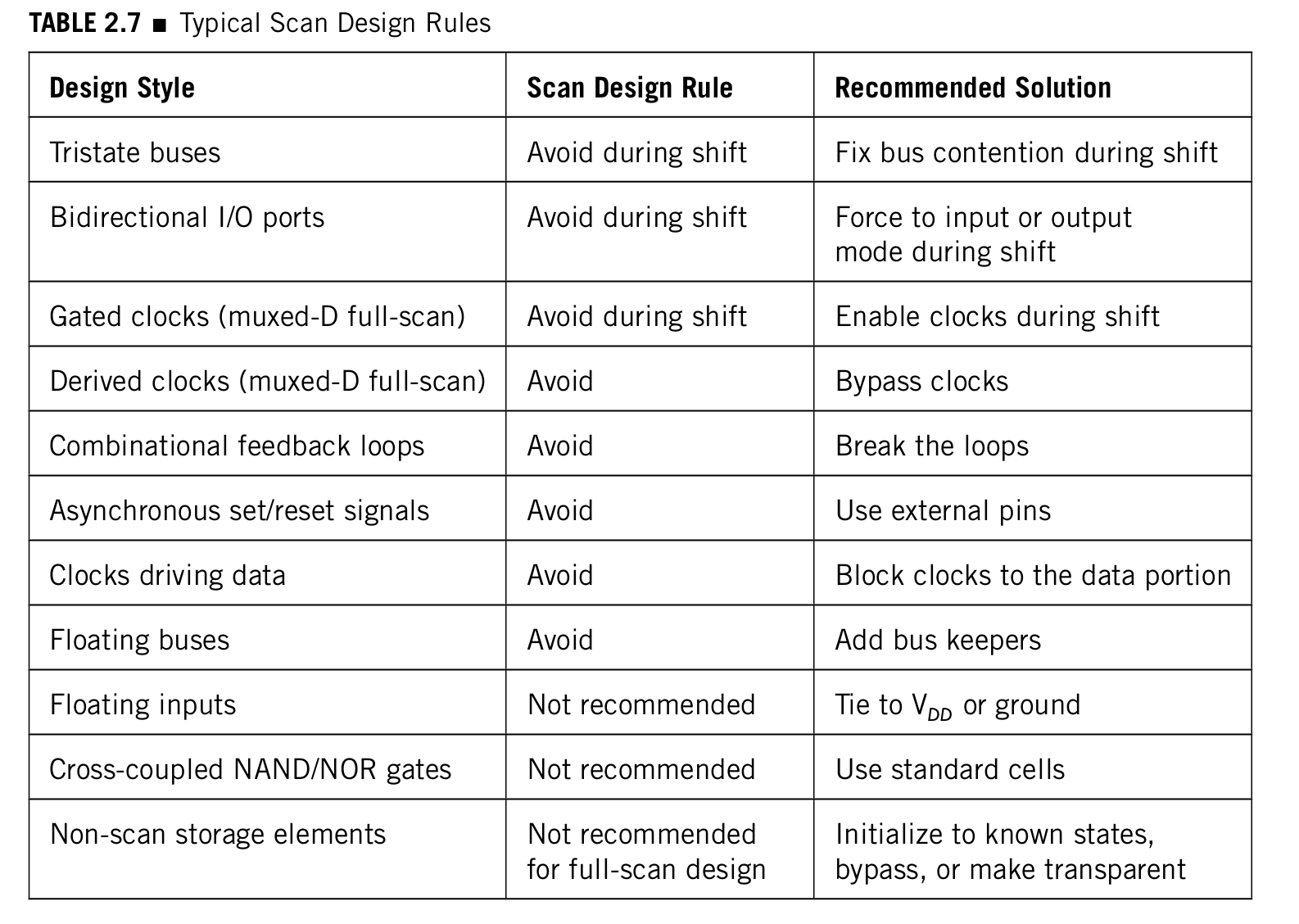

一些典型的scan设计规则如下表:

*标记"avoid"表示在shift和capture整个操作过程中都要避免

*标记"avoid during shift"表示在只在shift操作过程中避免

一些重要的规则在下面小分节细讲。

2.6.1 Tristate Buses

Bus contention:总线争用的定义,两个总线驱动不同的逻辑值进入tristate bus,这会损坏芯片。

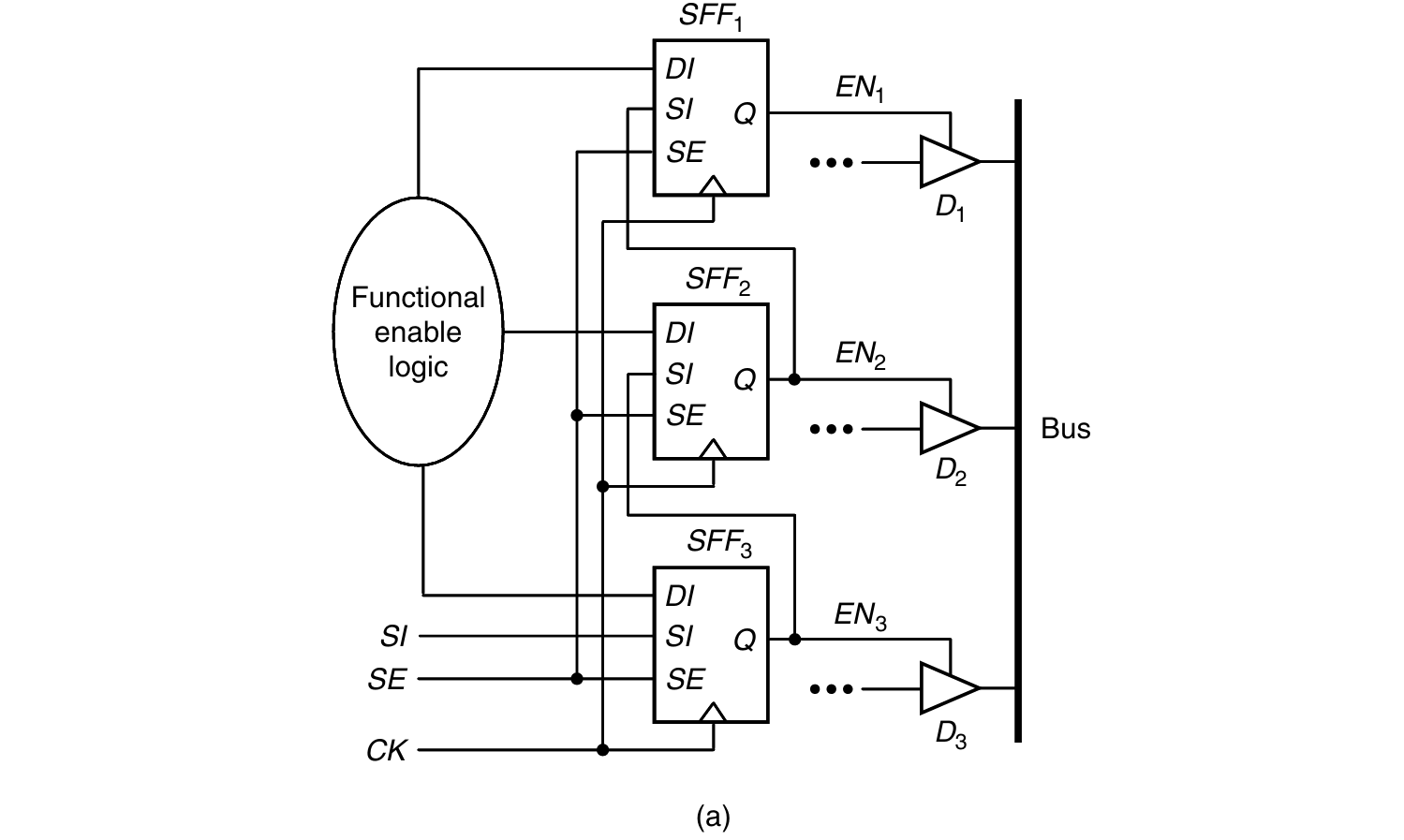

目前测试生成时可以在normal operation和capture operation情况避免总线争用,但是在shift operation时没办法保证,所以为了避免这个情况,要对tristate bus做一些修正保证只有一个驱动控制总线,举例子如下图,a图所示有3个总线驱动D1、D2、D3(可能会争用):

修正后的电路如下图b,SE = 1为shift mode时,EN1 = 1(使能D1),EN2和EN3 = 0(禁止D2和D3)(一次只允许一个驱动):

还有一个注意点,总线不能是floating的状态,因为这样它的状态是不确定的,在检测故障的时候就会带来困难,所以总线要设置上拉或下拉或者加上bus keeper(如图b),这样bus就不会floating。

2.6.2 Bidirectional I/O Ports

Bidirectional I/O ports:双向的I/O端口用来提升数据传输带宽。

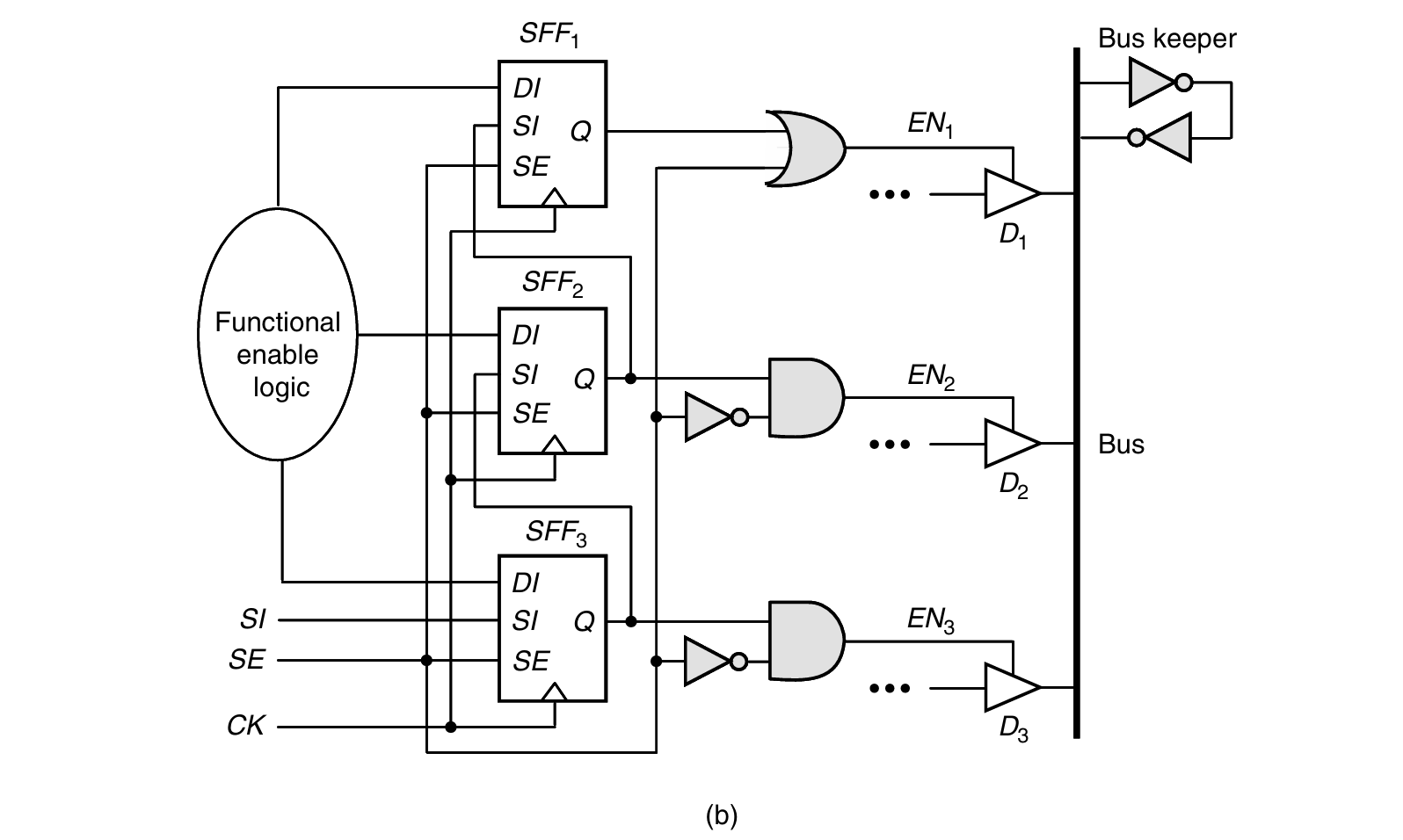

在capture operation时,双向I/O会被指定成输入或者输出,不会有冲突;但是在shift operation时,会发生冲突,例子见下图:

图a,scan cell控制I/O的方向,shift operation时scan cell的值会变,所以图中的三态buffer可能处于active状态,这时候如果BO和I/O(测试机控制值)不一致,就会发生冲突。

图b经过修正,SE = 1时,为shift operation,BO为inactive,测试机驱动I/O(测试向量从测试机通过I/O传到芯片内部),这样就不会发生冲突。

在capture operation时,SE = 0,三态buffer像图a一样,都由scan cell控制,所以I/O可能是输入也可能是输出,可以灵活控制测试机。

2.6.3 Gated Clocks

Clock gating:时钟门控,通过去掉存储单元没必要的开关行为降低功耗,设计中被广泛使用。

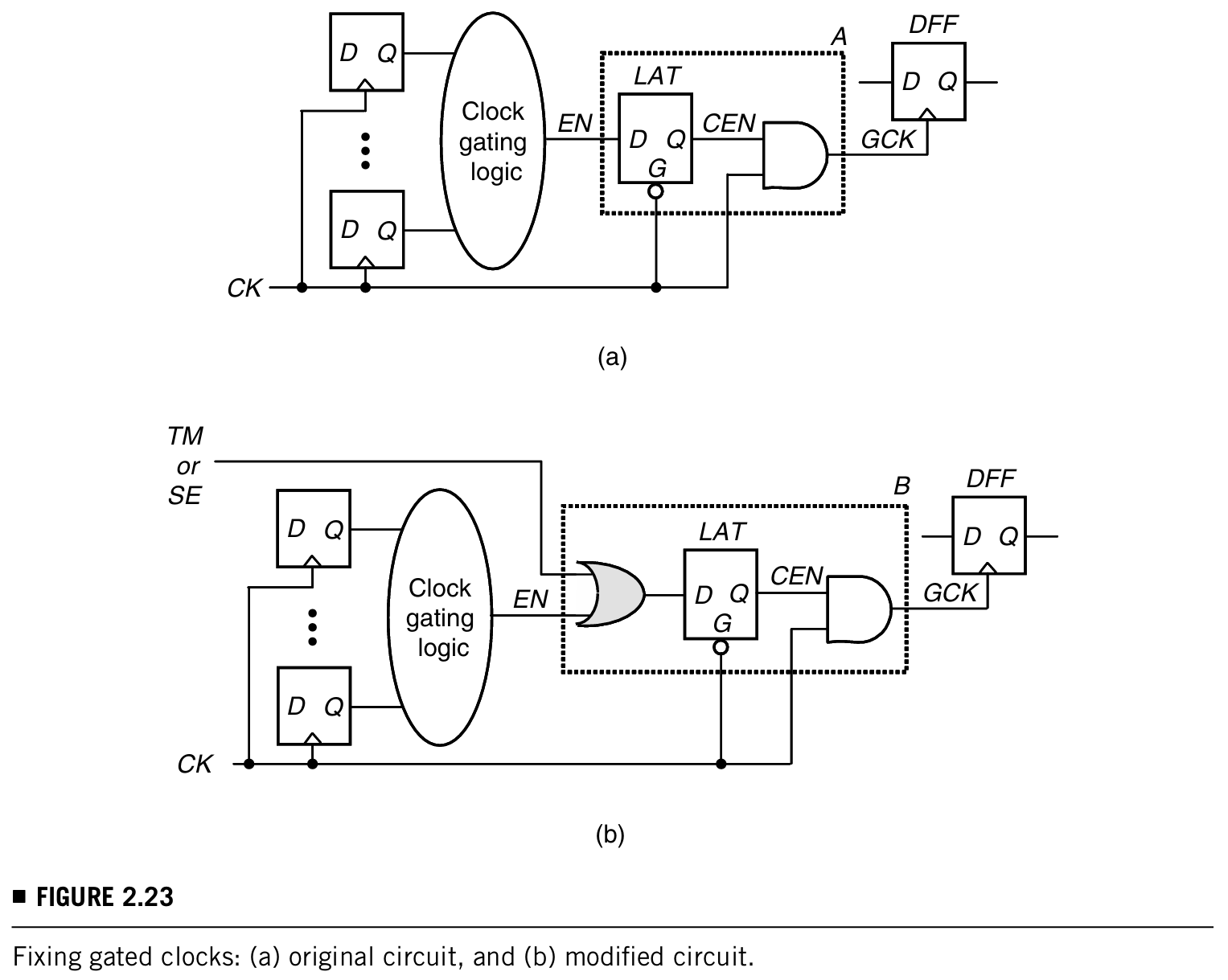

例子如下图:

图a中,时钟要先控制EN,然后变成CEN,然后才变成GCK去控制DFF(存储单元的时钟不能直接受控于primary inputs),但是我们想让shift mode下时钟能直接控制到存储单元。

所以有了修正后的b图,在shift operation时门控时钟不作用。是用了一个或门,然后借助TM或者SE迫使CEN是1,然后控制到DFF:

- 如果用TM,那么TM = 1,那么就是整个scan测试过程开启过程中CEN都是1,缺点是门控时钟电路中的故障无法被检测到,造成故障覆盖率损失

- 如果用SE,那么SE =1,那么就是shift operation过程中CEN是1,门控时钟能被测试,故障覆盖率更高,缺点是测试生成可能更复杂

2.6.4 Derived Clocks(派生时钟)

派生时钟指的就是内部的存储单元或者时钟生成器产生的内部时钟信号。典型的有锁相环phase-locked loop (PLL)、分频器frequency divider、脉冲发生器pulse generator。

因为派生时钟不是直接受控于primary inputs,所以为了测试派生时钟控制的逻辑的话,这些时钟信号在测试时需要被bypass。

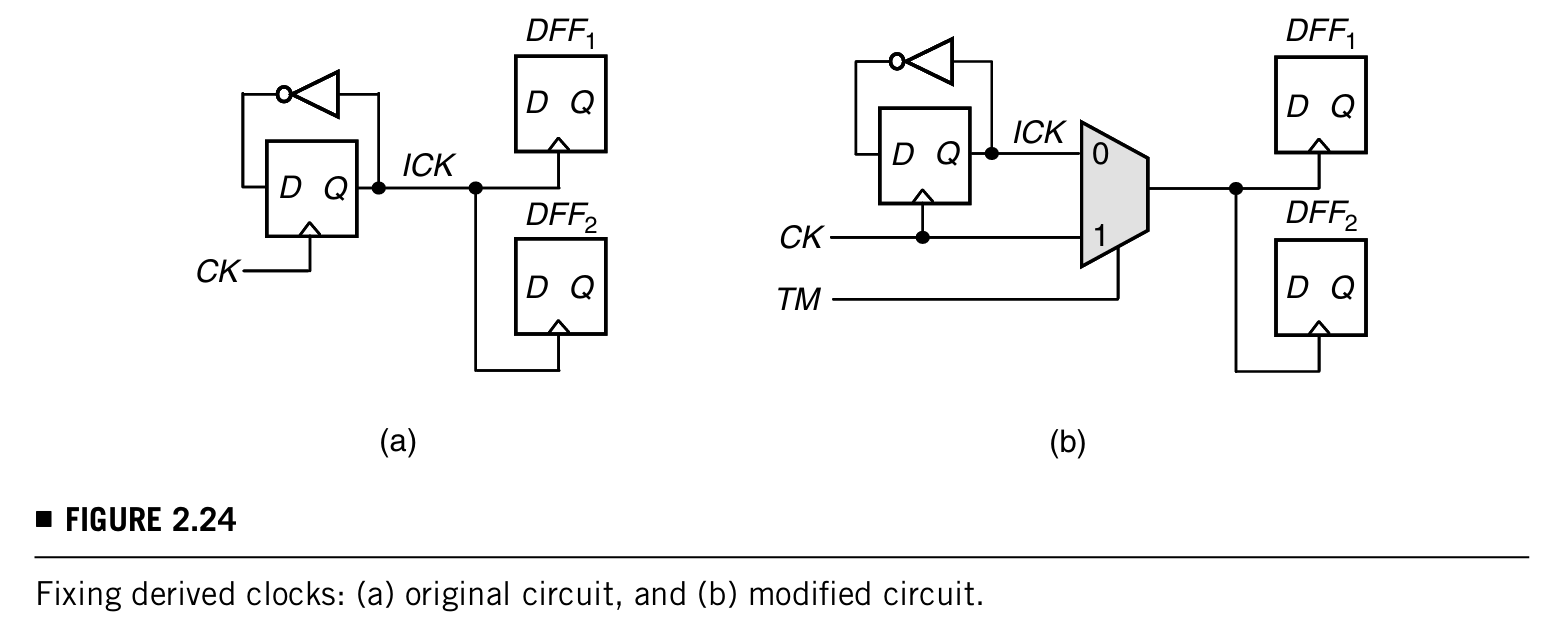

例子如下图:

图a派生时钟ICK控制DFF1和DFF2。图b,CK是直接受控于primary inputs,测试时TM = 1,此时CK控制DFF1和DFF2。

2.6.5 Combinational Feedback Loops(组合逻辑反馈环)

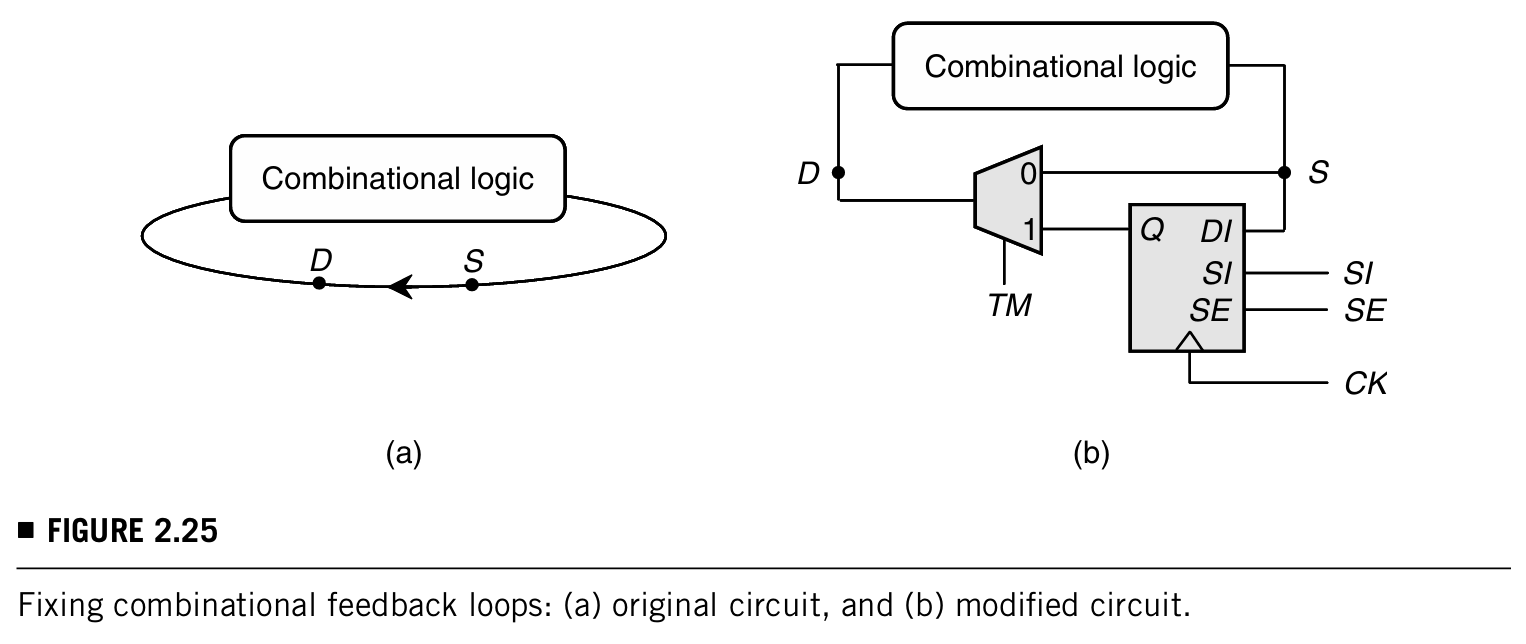

组合逻辑的feedback loop中反相器是奇数还是偶数决定了是否会引入时序行为或者震荡。测试时没办法控制和决定环内的数据,所以引起测试生成变复杂或者故障覆盖率下降(这种组合逻辑环其实在设计的时候就是不建议的,彻底改掉它就要改RTL代码),但是例如已经不能改了,那么下图a的例子就可以修正:

当TM = 1时,图b的修改就可以打断这个环。