Renesas RH850-U2A Inter-Processor Interrupt

- [1 Inter-Processor Interrupt Overview](#1 Inter-Processor Interrupt Overview)

- [2 Inter-Processor Interrupts Registers](#2 Inter-Processor Interrupts Registers)

-

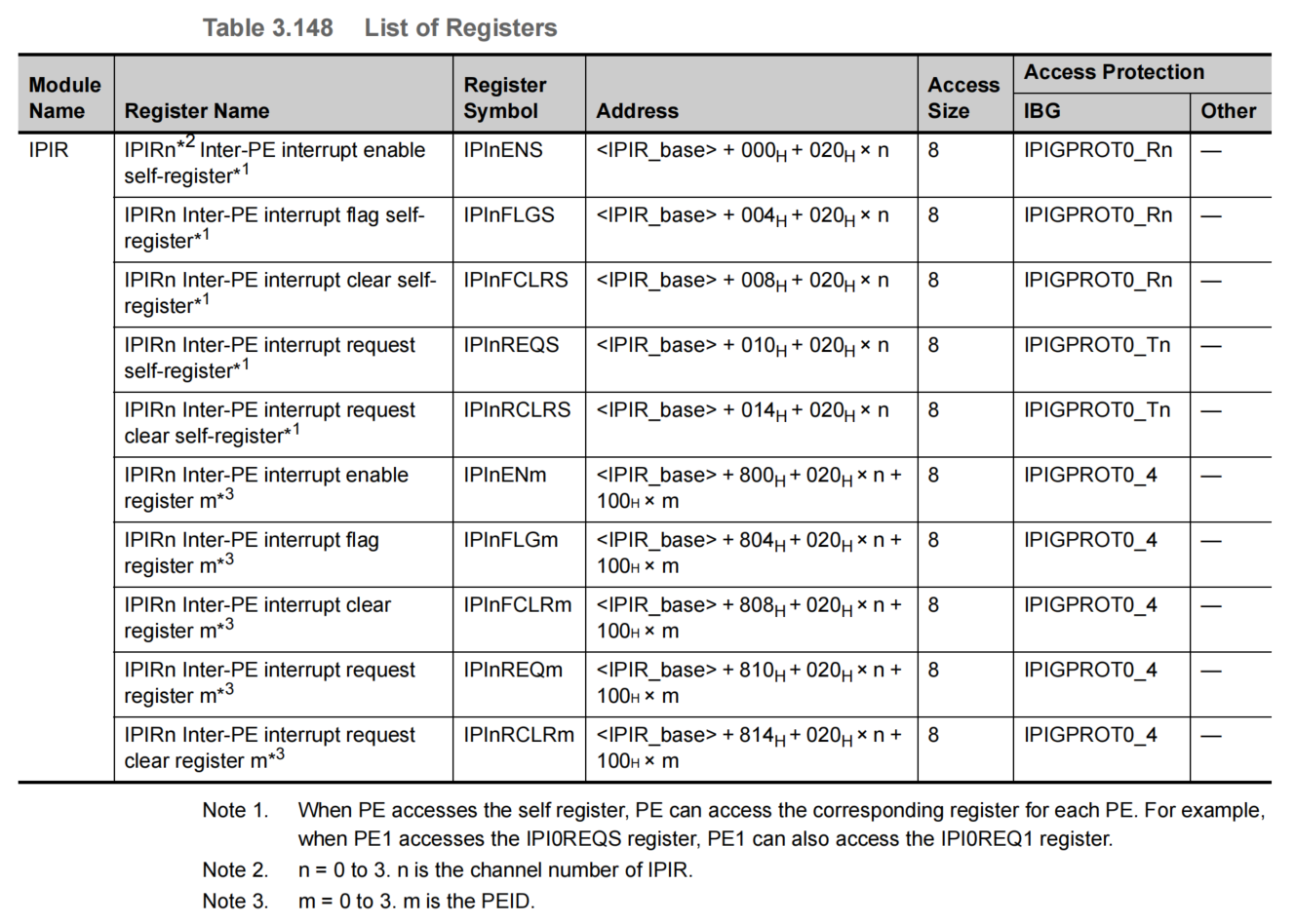

- [2.1 List of Registers](#2.1 List of Registers)

- [2.2 Self Region](#2.2 Self Region)

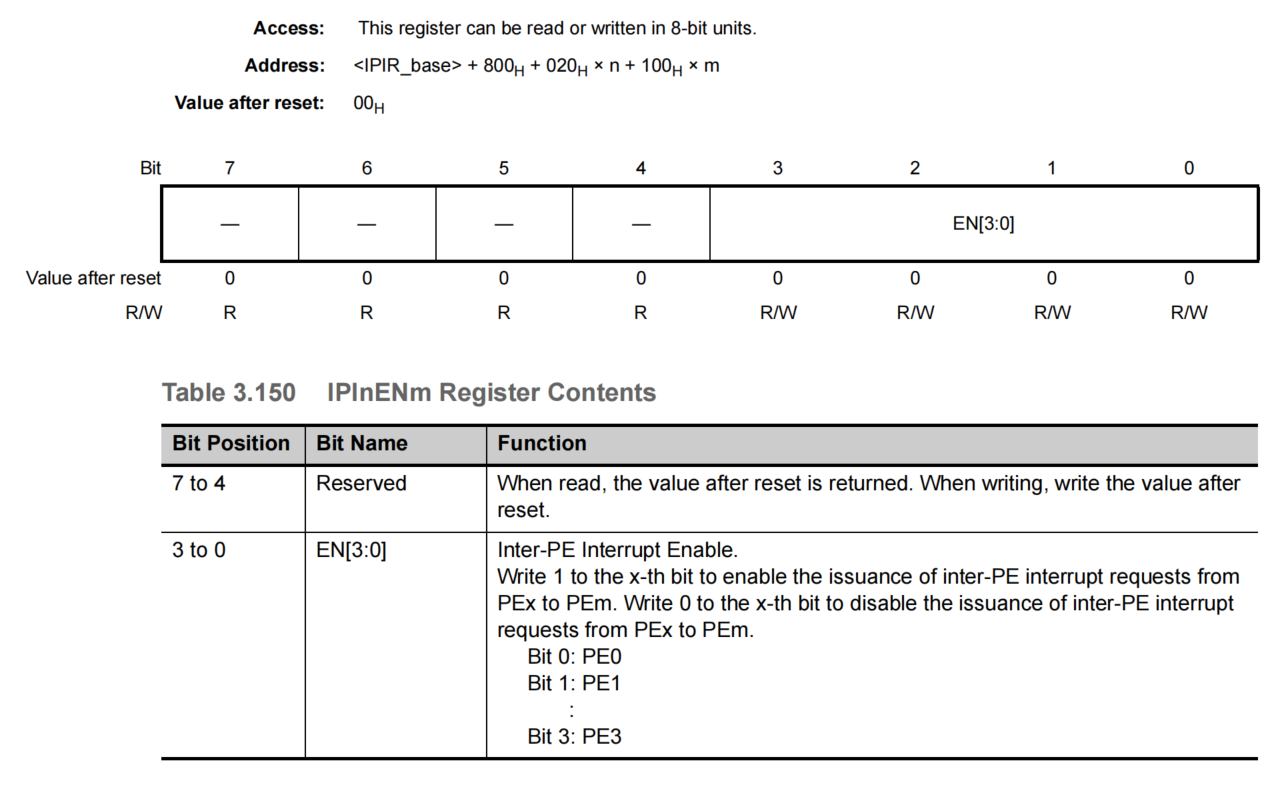

- [2.3 IPInENm --- IPIRn Inter-PE Interrupt Enable Register m](#2.3 IPInENm — IPIRn Inter-PE Interrupt Enable Register m)

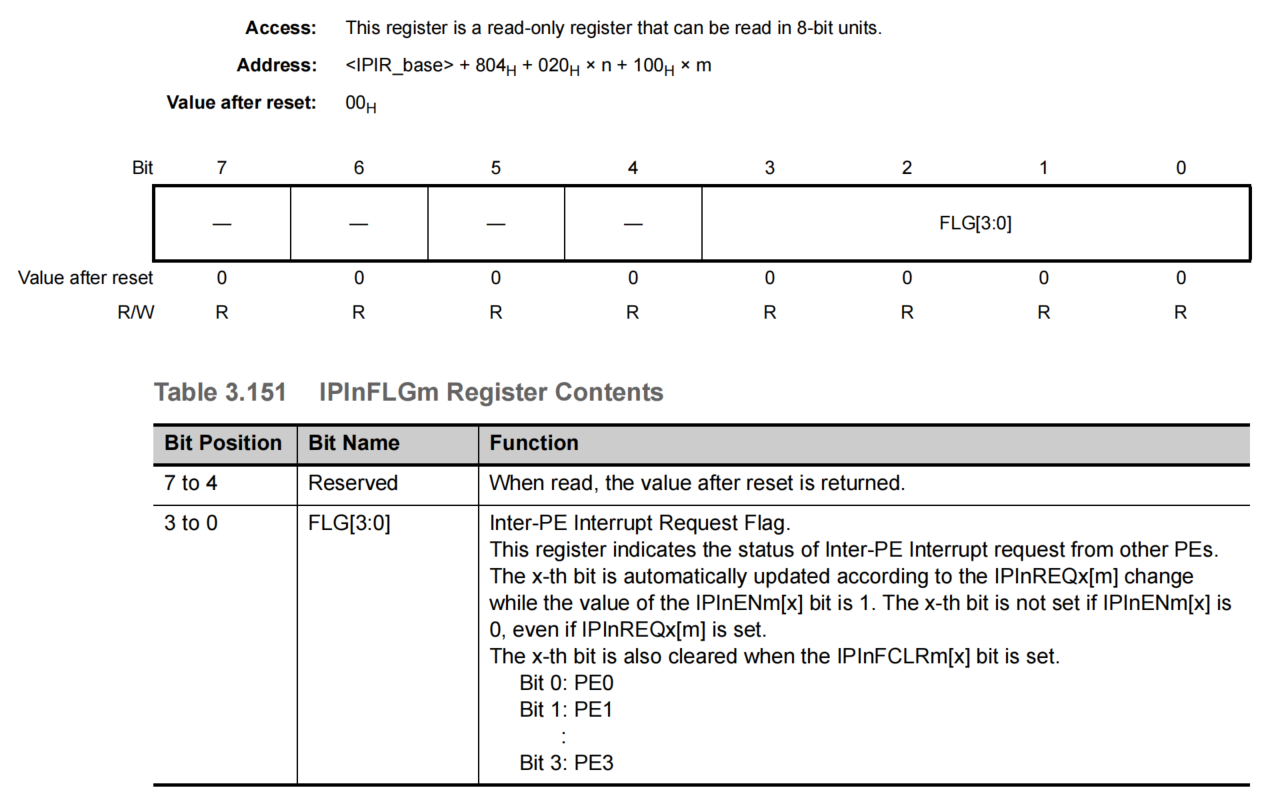

- [2.4 IPInFLGm --- IPIRn Inter-PE Interrupt Flag Register](#2.4 IPInFLGm — IPIRn Inter-PE Interrupt Flag Register)

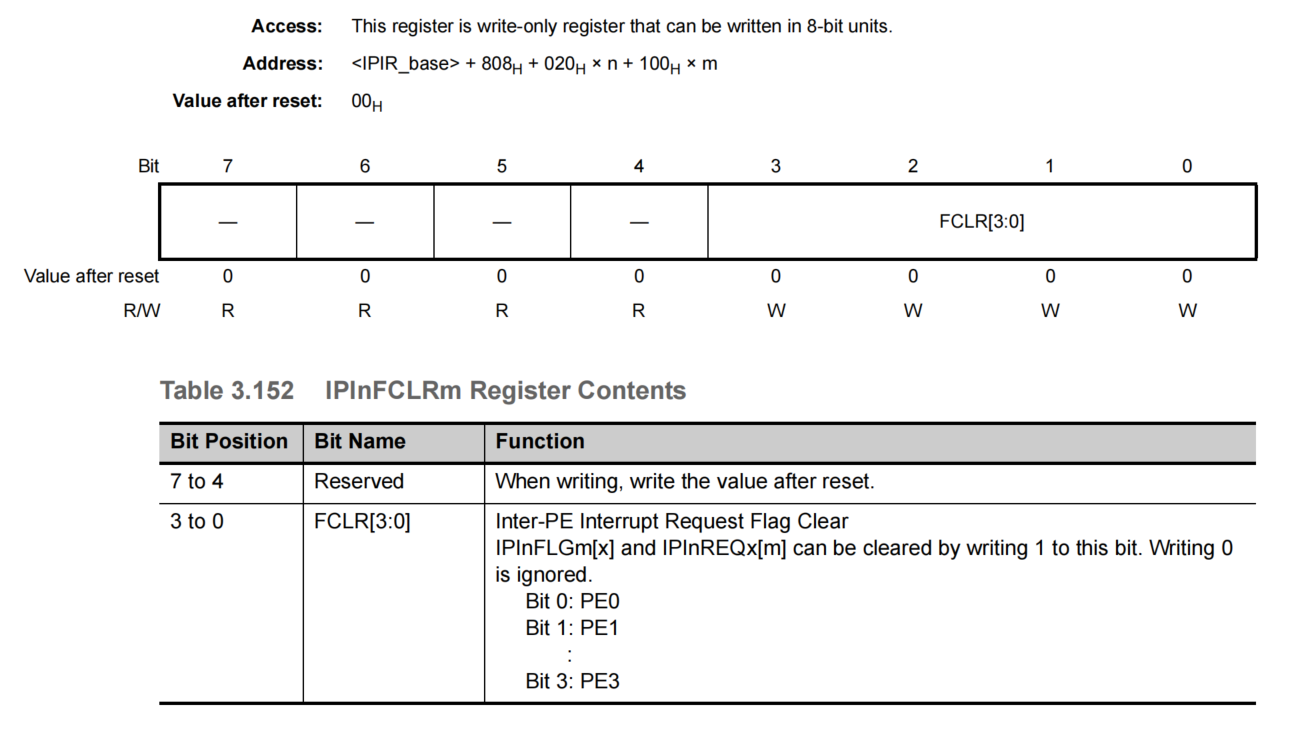

- [2.5 IPInFCLRm --- IPIRn Inter-PE Interrupt Clear Register m](#2.5 IPInFCLRm — IPIRn Inter-PE Interrupt Clear Register m)

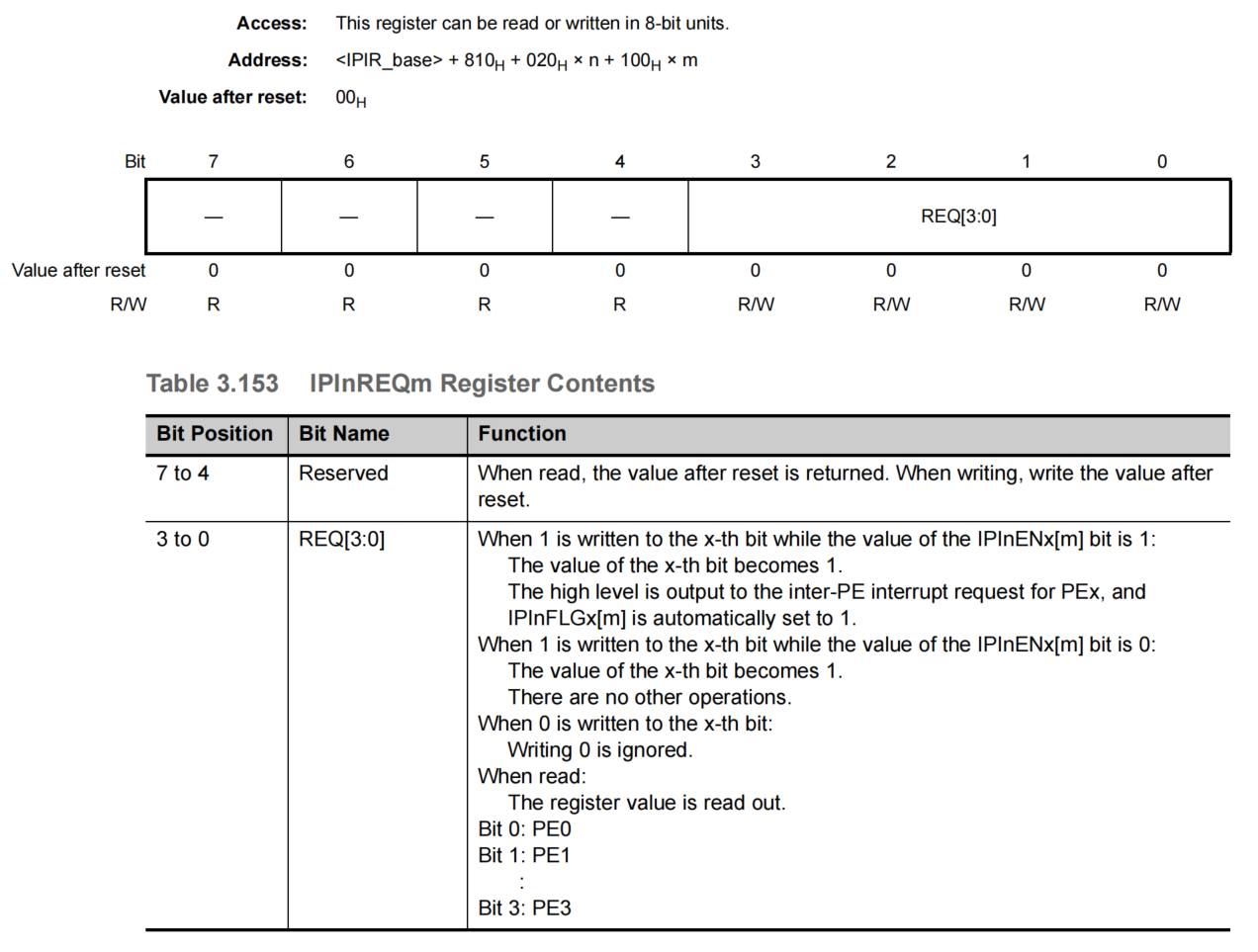

- [2.6 IPInREQm --- IPIRn Inter-PE Interrupt Request Register m](#2.6 IPInREQm — IPIRn Inter-PE Interrupt Request Register m)

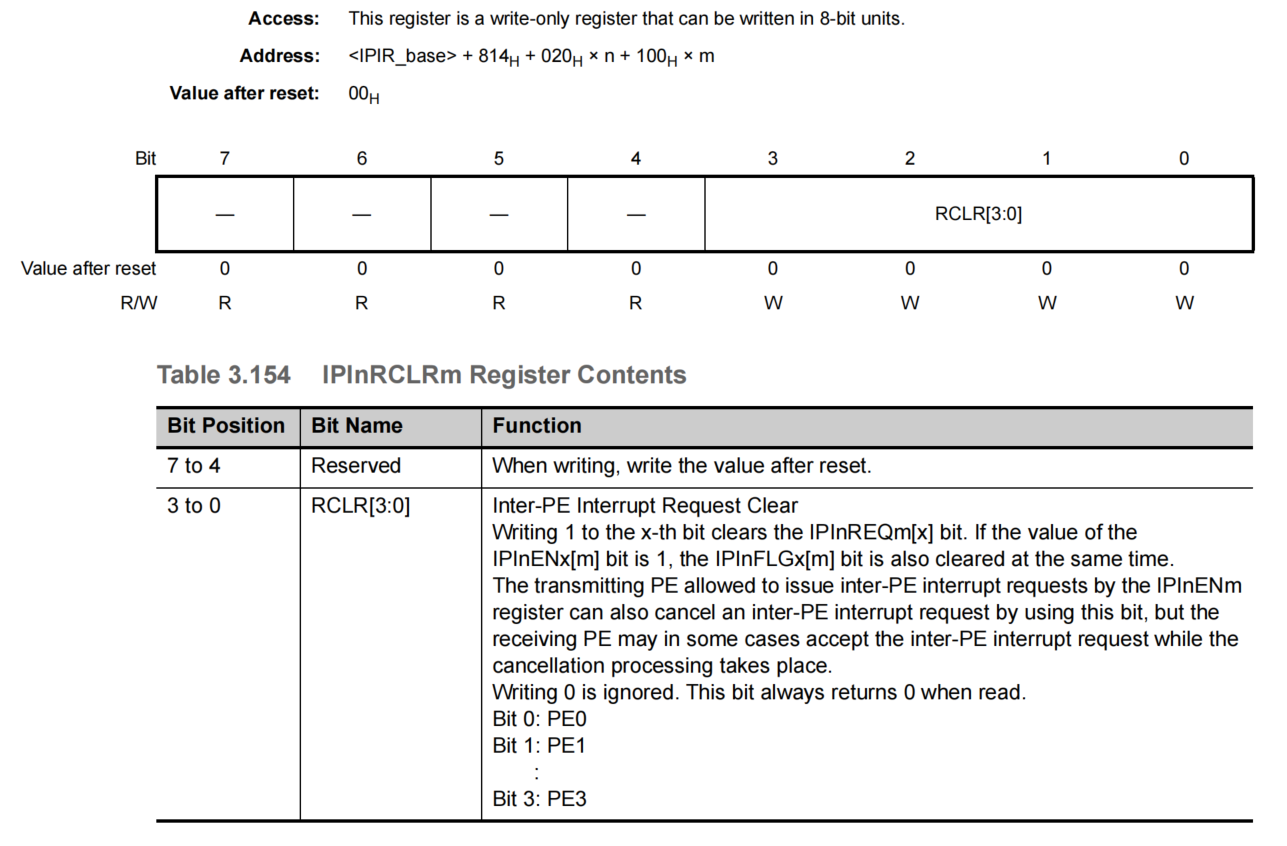

- [2.7 IPInRCLRm --- IPIRn Inter-PE Interrupt Request Clear Register m](#2.7 IPInRCLRm — IPIRn Inter-PE Interrupt Request Clear Register m)

1 Inter-Processor Interrupt Overview

Inter Processor Interrupt Register (IPIR) is a function that controls fast interrupt requests between PEs. Use of IPIR achieves faster processing of inter-PE interrupts than setting a request flag for the INTC2 interrupt channel by using software.

IPIR has the following features.

Support of inter-PE interrupt function of 4 channels

Level detection of interrupts. Edge detection is not supported.

Accessible from all clusters and all PEs

Identification of interrupt request source PE is possible.

Unintended inter-PE interrupts can be prevented by masking interrupt requests.

SET1, CLR1, and NOT1 can be executed as atomic operation instructions to IPIR.

Support of address EDC function

Support of data ECC function

Support of guard function to prevent unauthorized access.

-- Read-modify-write operations using the LD instruction and the ST instruction are also possible, but not as atomic operations.

2 Inter-Processor Interrupts Registers

2.1 List of Registers

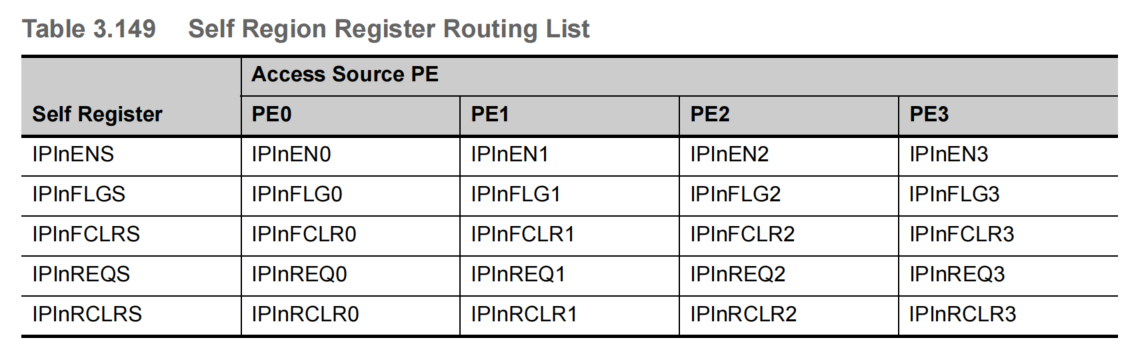

2.2 Self Region

The self region contains the following five types of registers.

IPInENS ---IPIRn Inter-PE interrupt enable self-register

IPInFLGS ---IPIRn Inter-PE interrupt flag self-register

IPInFCLRS ---IPIRn Inter-PE interrupt clear self-register

IPInREQS --- IPIRn Inter-PE interrupt request self-register

IPInRCLRS ---IPIRn Inter-PE interrupt request clear self-register

The self-registers are virtual registers that do not physically exist. Access from each PE to self-registers is routed to the actual register corresponding to the access source PE. Table 3.149 lists the access source PEs and routing destination registers. For the functions of each register bit, refer to the specifications of the routing destination register. When masters except PEx access the self registers, the register returns 0, write access is ignored and error response will be notified.

It is basically assumed that the IPIR registers are accessed from PEs via self region when PEs use the IPIR function. This allows PEs to use the same code because it is not necessary to specify different register addresses for each PE.

It is also possible to directly access registers by specifying the address of the actual register without using the self-registers. In this case, the purpose is assumed to be to check the status of registers for another PE, or to reference the individual registers by a debugging tool.

2.3 IPInENm --- IPIRn Inter-PE Interrupt Enable Register m

This register sets the transmitting PE allowed to issue inter-PE interrupt requests to PEm.

This register is used to enable inter-PE interrupt requests of PE (PEx) by the receiving PE (PEm) itself.

2.4 IPInFLGm --- IPIRn Inter-PE Interrupt Flag Register

This register indicates the transmitting PE that issued an inter-PE interrupt request to PEm.

This register is used to distinguish the requesting PE by PEm when PEm has received an inter-PE interrupt request.

2.5 IPInFCLRm --- IPIRn Inter-PE Interrupt Clear Register m

This register clears inter-PE interrupt requests to PEm.

This register is used to clear the request flag (IPInFLGm) and the request (IPInREQx) after receiving the Inter-PE interrupt request from another PE.

2.6 IPInREQm --- IPIRn Inter-PE Interrupt Request Register m

This register controls Inter-PE interrupt request from PEm to other PEs.

2.7 IPInRCLRm --- IPIRn Inter-PE Interrupt Request Clear Register m

This register clears inter-PE interrupt requests for other PEs by PEm.

This register is assumed to be used to clear inter-PE interrupt requests by the transmitting PE.