一、芯片核心定位

EG2181D 是一款在 SOP8 封装内集成了欠压保护功能 的单通道半桥栅极驱动专用芯片

其核心价值在于保持 600V 高端耐压与 2.5A 驱动能力 的同时,增加了 VCC 与 VB 双路欠压锁定(UVLO) ,且采用与 EG2181 引脚兼容的封装

专为需要更高电源可靠性、紧凑布局且成本敏感的无刷电机控制器、高压开关电源 等应用设计,是 EG2181 的功能增强版

二、关键电气参数详解

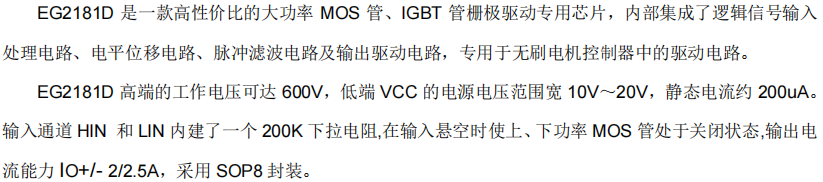

电源与耐压特性

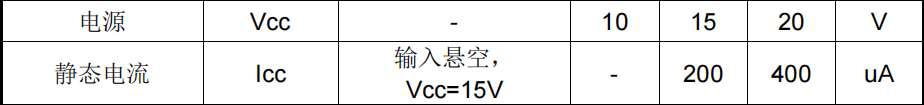

- 低端电源电压(VCC)范围 10V 至 20V(推荐工作值),开启阈值典型 8.8V,关断阈值典型 8.2V(欠压保护)

- 高端悬浮电源(VB)耐压 600V(极限值),开启阈值典型 8.6V,关断阈值典型 8.1V(欠压保护)

- 静态电流(ICC)典型 200μA(VCC=15V,输入悬空),功耗显著高于 EG2181(<5μA)

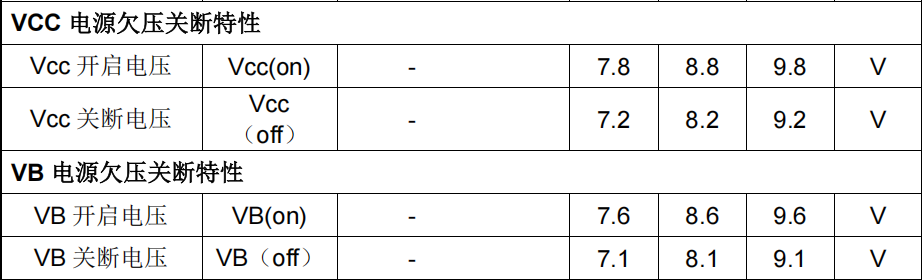

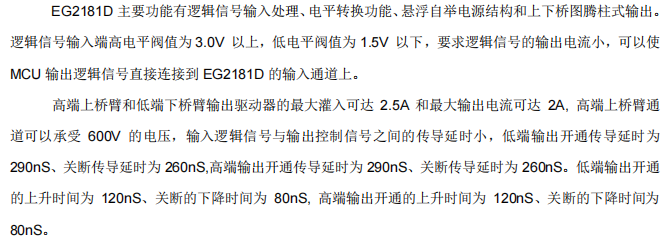

逻辑输入特性

- 输入高电平阈值(VIN(H))最小 3.0V,需注意与3.3V逻辑系统的兼容性(需确保逻辑高电平 > 3.0V)

- 输入低电平阈值(VIN(L))最大 1.5V

- 输入电流典型值 高电平时 ≤20μA(VIN=5V),低电平时 ≥-20μA(VIN=0V)

- 内置200kΩ下拉电阻,输入悬空时默认关闭上下管

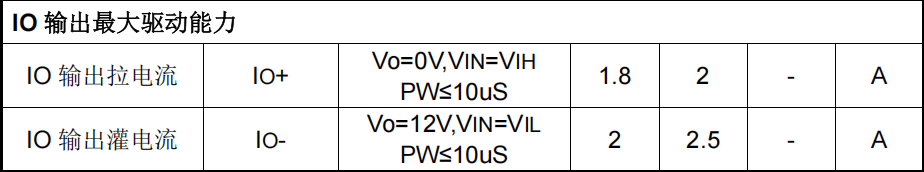

输出驱动能力

- 峰值拉电流(IO+)典型 2A,最小 1.8A(VO=0V,脉宽≤10μs)

- 峰值灌电流(IO-)典型 2.5A,最小 2A(VO=12V,脉宽≤10μs),驱动能力与 EG2181 相当

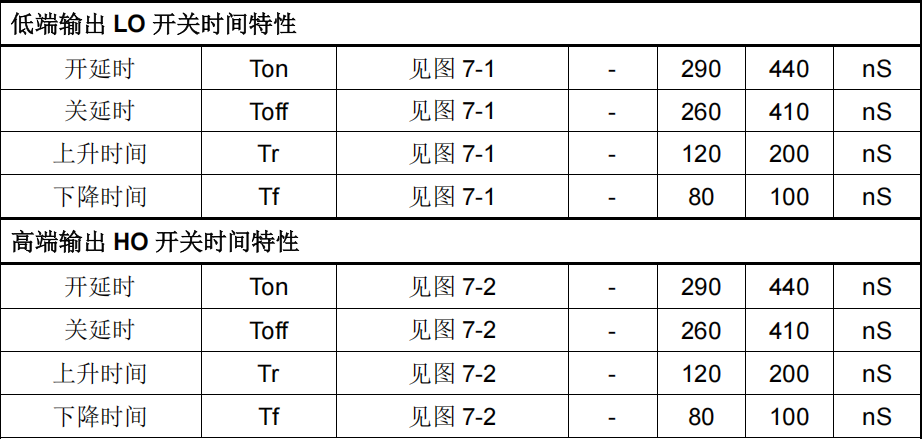

开关时间特性(测试条件:VCC=15V,CL=10nF)

- 低端输出LO 开通延时(Ton)典型 290ns,最大 440ns;关断延时(Toff)典型 260ns,最大 410ns

- 高端输出HO 开通延时(Ton)典型 290ns,最大 440ns;关断延时(Toff)典型 260ns,最大 410ns

- 上升时间(Tr)与下降时间(Tf)典型均为 120ns/80ns,开关速度与EG2181/EG21814系列保持一致

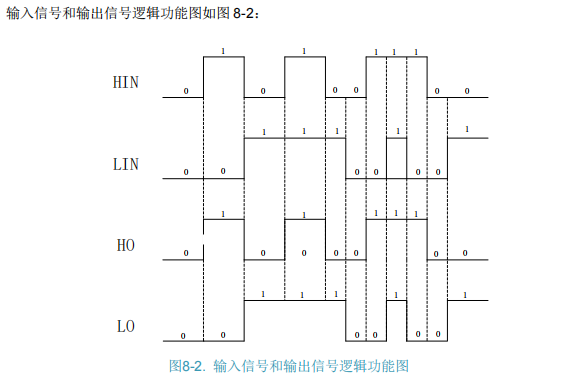

- 关键差异 芯片内部无死区时间控制电路,也无输入信号闭锁功能

三、芯片架构与特性优势

紧凑封装集成欠压保护

- 在保持与EG2181引脚兼容的SOP8封装基础上,集成了VCC和VB两路欠压保护(UVLO),提升了系统在电源波动或上电/掉电过程中的可靠性

无闭锁与无死区设计

- 与EG2181的最大区别在于:输入信号不相互闭锁,且内部无死区时间控制。HIN和LIN输入直接控制HO和LO输出,当两者同时为高时将导致上下管直通,防直通责任完全在外围控制器

功能定位介于EG2181与EG21814之间

- 相比EG2181:增加了UVLO,但取消了内部死区和闭锁,静态电流增大

- 相比EG21814:驱动电流略小(2.5A vs 3A),封装更紧凑(SOP8 vs SOP14),无独立功率地引脚

四、应用设计要点

VCC电源电压选择

- 推荐工作电压为 10V ~ 15V(典型15V),必须确保在工作温度范围内,VCC电压不低于欠压关断阈值(典型8.2V)

- 需在VCC引脚就近放置一个0.1μF以上的高频去耦陶瓷电容

外部死区时间控制(绝对必要)

- 由于芯片内部无死区与闭锁功能,必须由前级控制器(MCU、CPLD、专用PWM IC)在HIN和LIN信号中插入足够的、不重叠的死区时间

- 建议死区时间设置为300ns以上,并需通过示波器实测验证,确保在任何工况下无直通风险

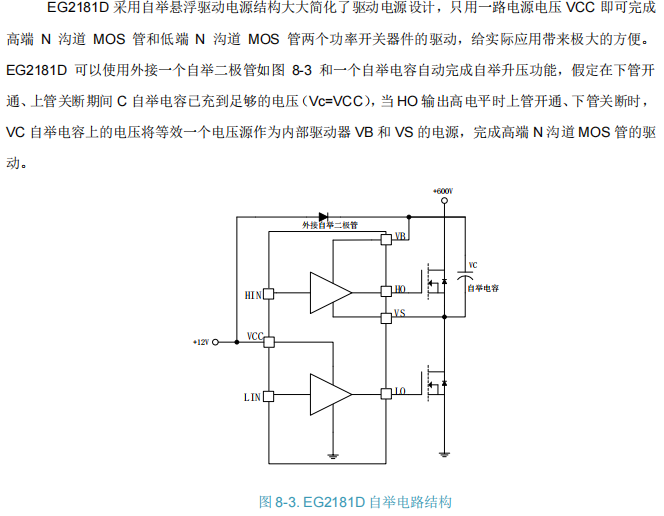

自举电路设计

- 自举二极管D 应选用快速恢复二极管(如FR107),其反向恢复时间应远小于开关周期

- 自举电容C_BOOT容值推荐0.1μF~10μF(低ESR陶瓷电容),耐压需高于VCC电压。容值选择需考虑开关频率和最大占空比,确保在高占空比下VB电压不会跌至欠压保护点(典型8.1V)以下

PCB布局准则

- 驱动回路最小化 HO/LO

输出至MOSFET栅极的路径应尽可能短,返回路径(下管源极至GND)同样需短而宽,以最小化寄生电感,抑制栅极振铃 - 单点接地 芯片GND引脚应作为驱动部分的接地参考点,与功率地和大电流回路地采用星型或单点连接,减少地噪声干扰

- 输入信号保护 HIN/LIN信号线若较长,建议串联小电阻(如100Ω)并增加对地小电容(如100pF)以滤除噪声

五、典型应用场景

紧凑型无刷直流电机(BLDC)驱动器

- 在电动自行车控制器、小型变频水泵中,驱动高压MOSFET,其SOP8封装节省空间

高压DC-DC开关电源

- 用于半桥、全桥拓扑中驱动高压侧开关,其欠压保护功能有助于实现可靠的软启动和故障保护

低成本Class-D音频功放

- 驱动输出级高压MOSFET,支持最高500kHz开关频率

通用半桥驱动模块

- 作为需要欠压保护且空间受限的半桥驱动方案的通用芯片

六、调试与常见问题

桥臂直通(最严重风险)

- 死区时间不足 首要检查外部控制器生成的PWM死区时间是否足够且稳定,这是使用该芯片的首要前提

- 输入信号干扰 检查HIN/LIN信号是否受到噪声干扰而产生毛刺,建议使用示波器近距离测量芯片引脚处的信号

欠压保护误触发

- VCC/VB电压跌落 检查电源去耦电容是否足够,布局是否合理。在高频开关时,电源网络的阻抗可能导致瞬间电压跌落触发UVLO

- 自举电容不足在高占空比(如>95%)工作时,自举电容可能没有足够的充电时间,导致VB电压逐渐下降最终触发欠压保护,需增大电容或确保最小下管导通时间

芯片发热

- 静态电流 注意其典型静态电流为200μA,远高于EG2181,在电池供电且常开的应用中需评估待机功耗

- 驱动负载过重 检查所驱动MOSFET的栅极电荷(Qg),确保在开关频率下芯片的平均功耗在安全范围内

逻辑电平不兼容

- 3.3V系统兼容性 由于输入高电平阈值最小为3.0V,部分3.3V逻辑器件在输出高电平时可能电压裕量不足,建议验证或使用电平转换电路

七、总结

EG2181D 在 EG2181 的引脚兼容基础上,通过 增加双路欠压保护(UVLO) 提升了系统的电源可靠性,但同时 移除了内部死区与闭锁功能,并将静态电流提升至200μA

这种设计使其成为一款需要用户具备较强外部时序控制能力、但又能从集成UVLO中受益的紧凑型半桥驱动器

成功应用的两大支柱是:1. 由外部控制器提供的、经过充分验证的可靠死区时间;2. 精心设计的自举电路以确保高压侧驱动电源稳定

在对空间、成本及电源可靠性有要求,且系统设计者能够严格掌控PWM时序的高压半桥驱动场合,EG2181D是一款具有实用价值的升级选择

文档出处

本文基于屹晶微电子(EGmicro)EG2181D 芯片数据手册 V1.0 整理编写,结合半桥驱动电路设计实践

具体设计与应用请以官方最新数据手册为准,在实际应用中务必首要验证外部死区时间的有效性,并关注自举电路在高占空比下的工作状态