在芯片设计领域,一个微小错误可能导致数亿美元的损失------某个处理器漏洞曾让公司付出几亿美元的代价,阿丽亚娜5号火箭因软件错误发射后爆炸。这些惨痛教训让行业意识到:传统验证方法已不足以应对日益复杂的芯片设计。

形式验证(Formal Verification)作为一种数学上的严格验证方法,正成为确保芯片可靠性的关键利器。

一、什么是形式验证?

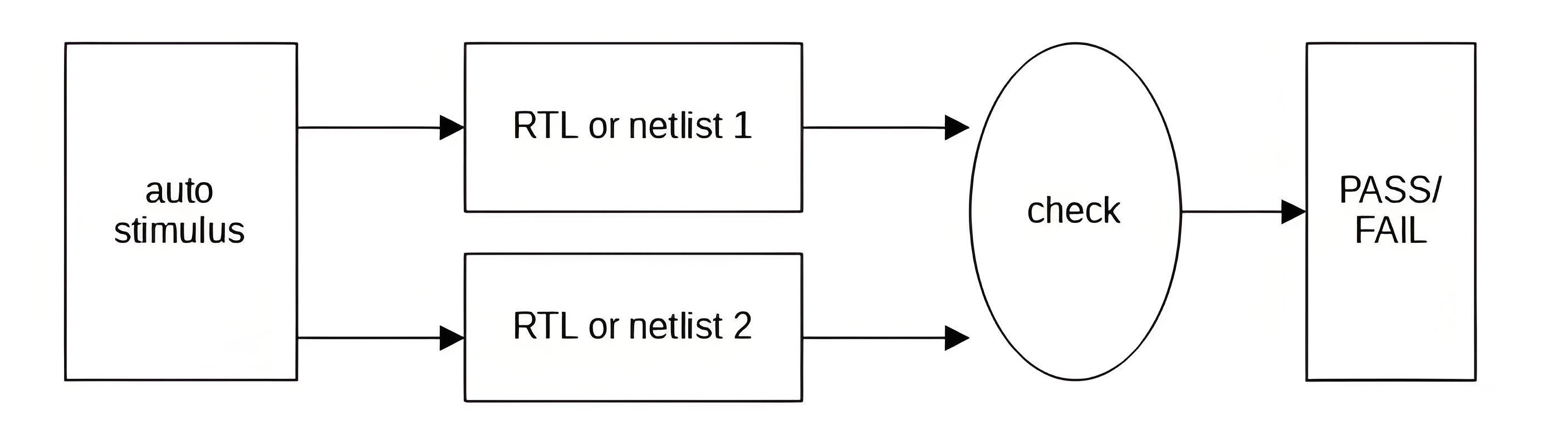

形式验证本质上是利用数学方法证明电路设计是否满足特定属性要求。与通过大量测试用例进行仿真的传统方法不同,形式验证通过数学建模和逻辑推理,穷举所有可能的状态来验证设计的正确性。

简单来说,传统仿真像是实验检测,通过大量样本推断整体质量;而形式验证则是数学证明,从逻辑上确保万无一失。

形式验证主要包括两大应用:

等价性检查:验证综合或布局布线后的网表与原始RTL设计是否功能等价

属性检查:通过断言(Assertion)验证设计是否满足特定功能要求

二、为什么需要形式验证?

随着芯片复杂度呈指数级增长,传统验证方法面临巨大挑战:

一个简单加法器设计,如果要通过仿真覆盖所有64位输入组合,需要运行184亿亿次测试------这是传统仿真无法完成的任务。而形式验证可以在短时间内从数学上穷举所有可能情况,包括那些罕见的边界条件。

形式验证的核心优势:

早期验证:RTL代码完成后即可开始,无需等待测试平台开发

完备性:覆盖所有可能输入场景,不留死角

高效性:对控制逻辑、状态机等设计验证速度极快

确定性:数学证明提供100%确信,而非"概率性"保证

三、形式验证 vs. 仿真 vs. 硬件加速

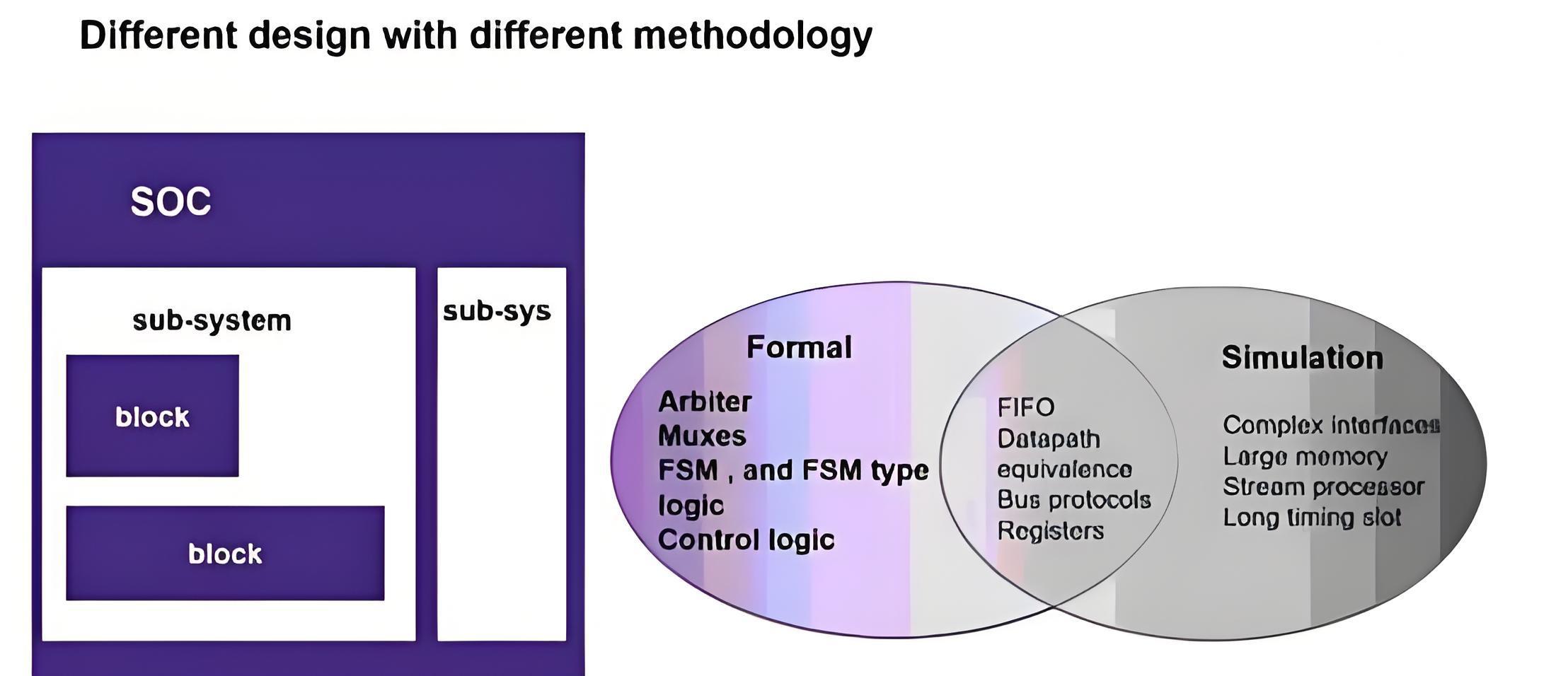

芯片验证通常采用多种方法结合的策略:

1.动态仿真(Simulation)

方法:搭建测试平台(Testbench),输入激励信号,观察输出结果

优势:适合系统级验证,可处理复杂数据路径和算法

劣势:难以覆盖所有场景,验证周期长,效率随复杂度增加而降低

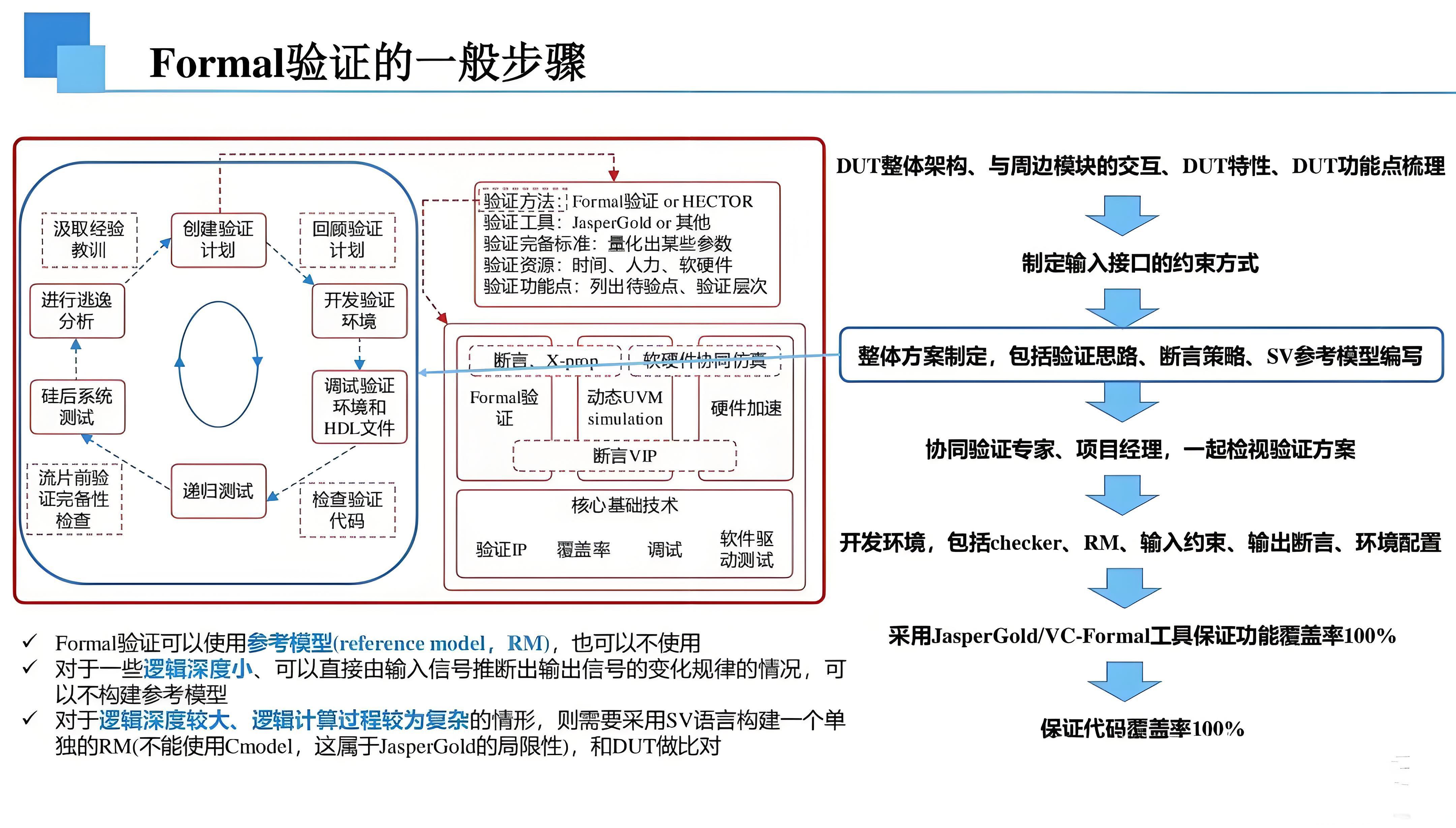

2.形式验证(Formal)

方法:数学建模,属性证明,无需测试向量

优势:穷举性验证,快速收敛,早期缺陷检测

劣势:受状态空间爆炸问题限制,适合模块级而非全芯片验证

3.硬件加速/FPGA原型验证

方法:将设计映射到实际硬件上运行真实软件

优势:运行速度快,接近真实场景

劣势:调试困难,搭建成本高

这三种方法并非相互替代,而是相辅相成的关系。智能的验证策略是在不同阶段采用最适合的方法:形式验证用于模块级关键属性验证,仿真用于系统级集成验证,硬件加速用于软件协同验证。

四、形式验证的典型应用场景

形式验证在某些场景下表现尤为出色:

控制逻辑验证:仲裁器、状态机、总线控制等

连接性检查:确保芯片内部各个模块正确连接

低功耗验证:时钟门控、电源管理电路的功能验证

死锁检测:发现系统中可能的死锁条件

安全关键属性:确保安全机制在任何情况下都不会被绕过

五、形式验证的局限性

尽管形式验证优势明显,但它并非万能钥匙:

状态空间爆炸问题是最大挑战。每个触发器都会使状态空间翻倍,设计规模稍大就会导致验证时间急剧增加甚至无法完成。

形式验证不适合数据路径密集型设计,如复杂的算术运算模块。对于这类设计,仿真的效率通常更高。

形式验证难以处理深时序逻辑和复杂的多模块协同工作场景。当前工具仍主要适用于模块级而非全芯片级验证。

六、未来展望

随着AI、汽车电子、航空航天等领域对芯片可靠性要求越来越高,形式验证的重要性日益凸显。它不仅是发现错误的工具,更是建立信任的手段------如何证明你的自动驾驶芯片是安全的?形式验证提供了可能的答案。

未来验证方法学将是形式验证与仿真验证的深度融合:形式验证解决"最后一公里"的边界条件,仿真验证保证系统级功能正确性。这种混合验证方法已成为业界领先公司的标准实践。

结语

在芯片复杂度不断挑战物理极限的今天,形式验证代表了验证方法学的重要进化:从"基于测试"到"基于证明"的转变。它虽不能完全取代传统仿真,但已成为现代芯片验证流程中不可或缺的一环。

对于追求零缺陷的芯片设计,形式验证不再是可选的高级功能,而是必要的质量保证手段。正如一位验证专家所说:"仿真告诉你设计在大多数情况下是工作的,而形式验证告诉你设计在所有情况下都不会失败。"这种确定性,在关键应用场景中是无价的。