在集成电路制造中,纳米尺度的物理缺陷不可避免。为了确保芯片功能可靠性,故障模型作为测试理论基础和工程实践指南,成为芯片质量保障体系的核心环节。本文将深度解析各类故障模型的原理、检测方法及实际应用。

一、故障模型基础概念与重要性

1. 故障模型的本质作用

故障模型是在晶体管级或门级对物理缺陷的抽象建模,它将千奇百怪的物理缺陷转化为可量化、可检测的逻辑行为。通过故障模型,测试工程师能够:

量化测试质量,评估测试覆盖率

实现测试自动化(ATPG、故障仿真、自动诊断)

降低测试成本,提高测试效率

2. 基本术语辨析

在深入探讨前,需明确关键术语的区别:

缺陷:制造过程中的物理异常,如金属线短路、氧化层击穿

故障:缺陷在电路功能层面的表现,如信号线恒为高电平

失效:故障导致系统输出偏离预期值的结果

漏洞:设计阶段的逻辑错误,属于功能性设计缺陷

故障建模主要关注制造缺陷引发的功能偏离,而非设计错误。

二、数字逻辑故障模型详解

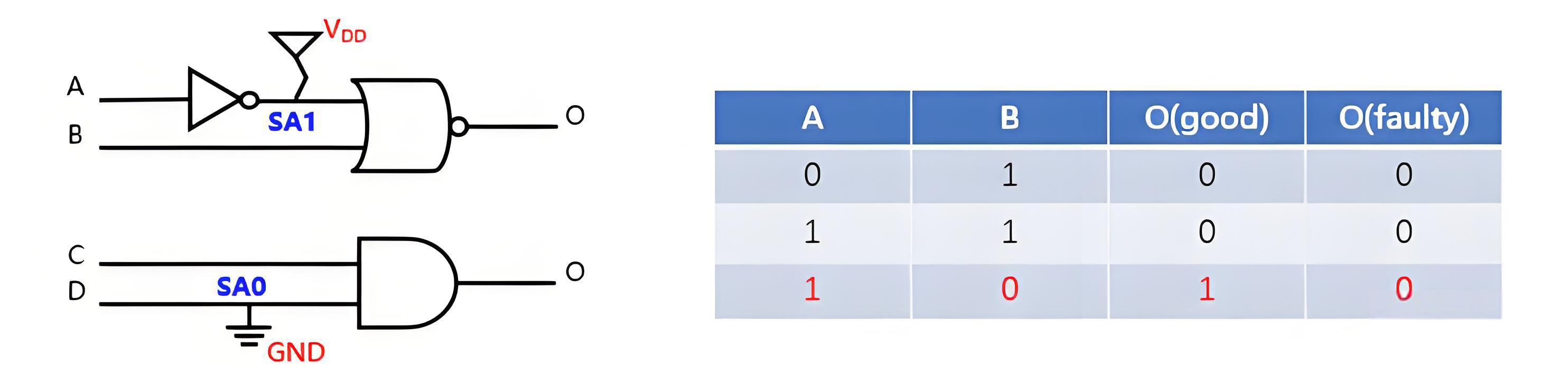

1. 固定型故障模型

最基础且应用最广泛的故障模型,假设电路节点永久固定于逻辑0或1状态。

特点:

模拟短路/粘连现象

故障数量与芯片规模呈线性关系

通过SA0/SA1测试向量检测

测试原理:施加特定输入组合激活故障,在输出端观测异常响应。

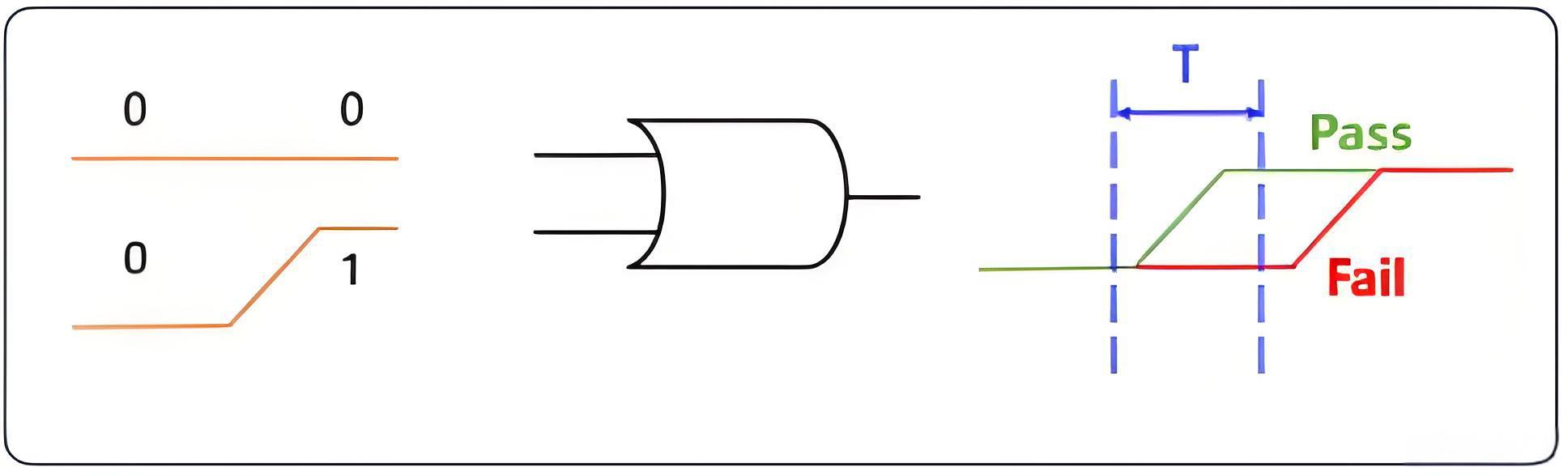

2. 延迟故障模型

针对高速芯片的时序完整性测试,主要包括:

跳变延迟故障:

STR:0→1转换缓慢

STF:1→0转换缓慢

需要launch-capture时序测试模式

路径延迟故障:

关注关键路径上的累积延迟

测试更贴近实际工作条件

生成难度较高,需要时序分析支持

3. 桥接故障模型

随着芯片集成度提高,线间距减小,桥接故障日益重要:

类型分类:

AND型桥接:两节点逻辑"与"关系

OR型桥接:两节点逻辑"或"关系

反馈型桥接:形成寄生振荡或锁存效应

检测方法:需结合双向驱动能力分析与多向量测试策略。

4. 晶体管级故障模型

在CMOS工艺下,晶体管级故障直接影响电路性能:

固定开路故障:晶体管栅极失效导致无法导通,需要两个测试向量检测。

固定短路故障:源漏极之间形成低阻通路,可通过IDDQ测试识别。

三、存储器专用故障模型

存储器具有高度规则化结构,需要专用故障模型:

1. 单元固定故障

存储单元无法可靠写入0或1,通过March算法进行读写交替测试。

2. 耦合故障

当一个单元写操作影响邻近单元内容时发生:

CFin:目标单元写1导致相邻单元翻转

CFid:仅当特定数据写入时才触发

CFst:受周围单元数据模式影响

3. 临近图形敏感故障

强调空间邻近单元的数据组合对中心单元稳定性的影响,在高密度存储器中尤为突出。

4. 地址译码故障

包括地址无对应单元、多个地址映射冲突等问题,需通过地址空间遍历测试。

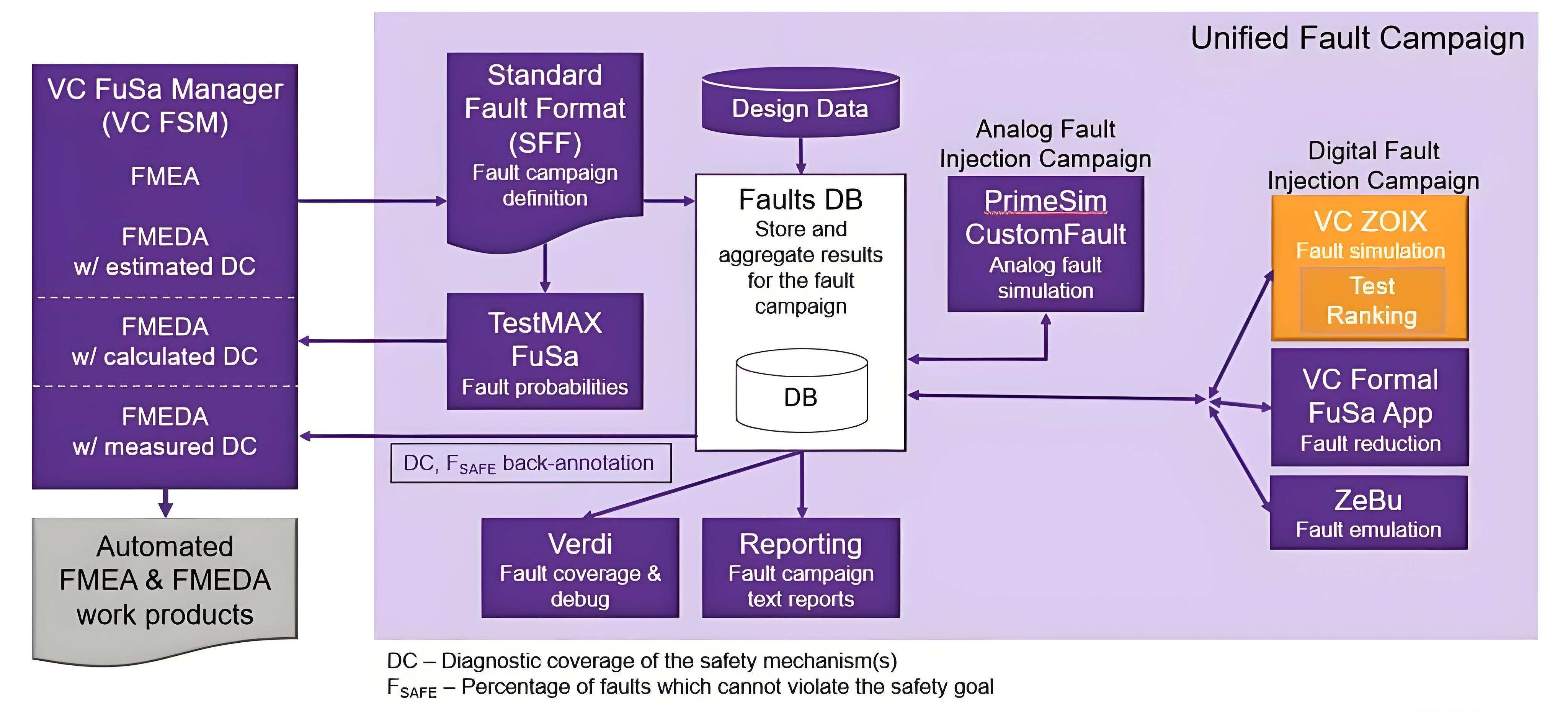

四、故障模型在测试流程中的应用

1. ATPG自动测试向量生成

基于故障模型的ATPG流程:

选择目标故障:从故障列表中选取待检测故障

激活故障:使故障节点呈现异常值

传播故障:将故障值传递至可观测点

生成测试向量:确定满足条件的输入组合

2. 故障仿真与覆盖率分析

通过故障仿真评估测试质量,计算故障覆盖率:

故障覆盖率 = 被检测到的故障数 / 总故障数

工业界要求组合逻辑达到98%以上,安全关键应用要求99%以上。

五、故障模型与产品质量指标的关系

1. DPPM控制策略

通过故障模型指导的测试策略,能够有效控制DPPM:

随机缺陷筛选:通过老化测试加速早期失效暴露

统计过程监控:建立失效分析数据库,监控异常趋势

持续改进机制:根据失效数据分析结果优化工艺

2. 测试覆盖率的工程意义

高故障覆盖率直接关系到产品质量水平,体现了测试完备性。通过故障模型建立的测试方案,能够在设计阶段预测和改善产品的可测试性。

六、行业发展趋势与挑战

1. 先进工艺带来的新挑战

随着工艺节点持续微缩,新型故障机制不断出现:

3D IC结构的故障建模

FinFET器件的特有故障模式

2. 先进封装下的互连故障模型

3. 机器学习在故障模型中的应用

AI技术正在改变传统故障建模方式:

智能故障预测与分类

自适应测试模式生成

基于数据的故障模型优化

七、结语

故障模型作为芯片测试的理论基础,连接了物理缺陷与测试实践。从简单的固定型故障到复杂的时序相关故障,故障模型的演进反映了半导体技术的进步。

在未来,随着芯片复杂度不断提升,故障模型将继续发挥核心作用,推动测试技术向更高效、更精准的方向发展。掌握故障模型的理论与实践,对于提升芯片产品质量和竞争力具有至关重要的意义。