1.BM501简介

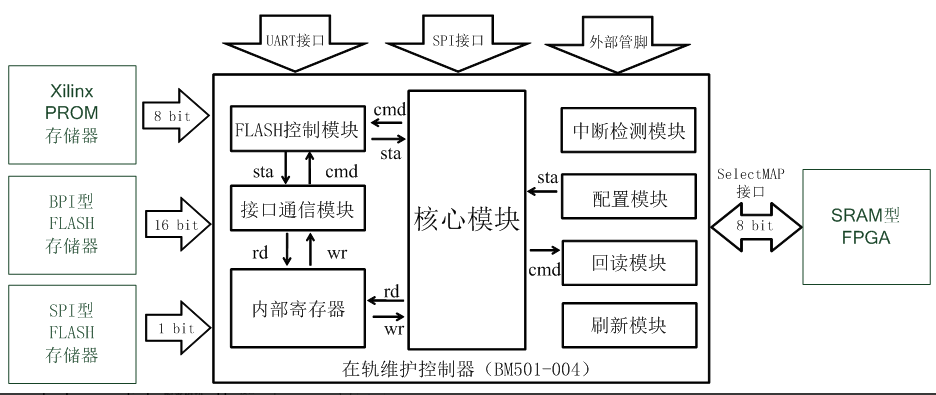

BM501-004RBB是宇航级产品,可以为FPGA空间应用提供上电配置、实时刷新、在轨重构、单粒子功能中断监测的应用解决方案,保证FPGA在轨使用的可靠 性和安全性,大幅度降低刷新系统设计的难度和复杂度。其架构如下图所示:

该控制器具有通过 UART 口和 SPI 口遥测遥控能力,可以实现在轨的码流重构,对指定型号 BPI FLASH 和 SPI FLASH 进行擦除、编程、校验。

2. 核心概念:什么是重刷?

"重刷" (Scrubbing) 是 SRAM 型 FPGA 在航天应用中最重要的抗辐照手段之一。

-

形象比喻: 这是一个"动态治疗"的过程。

-

医生 (Controller): 也就是 BM501-004,负责通过 SelectMAP 接口给 FPGA 做检查。

-

病人 (FPGA): 也就是 BQ7K325T,容易受辐射影响而"生病"。

-

健康档案 (Flash): 存储着正确的"基因数据"(Golden Copy)。

-

-

功能目标: 一旦检测到 FPGA 内部发生"基因突变"(比特翻转),立刻参照 Flash 中的标准数据将其修复,实现系统的自愈。

3. 为什么需要重刷?

-

器件弱点: 选用的 FPGA(BQ7K325T,对标 Xilinx K7)基于 SRAM 工艺。SRAM 的物理特性决定了它在掉电后数据会丢失,且对空间辐射极度敏感。

-

威胁来源: 太空中的高能粒子(质子、重离子等)。

-

失效机理 - SEU (单粒子翻转):

-

当高能粒子撞击 FPGA 的配置存储单元(Configuration Memory)时,可能导致存储位的逻辑翻转(0 变 1,或 1 变 0)。

-

后果: 这种翻转不仅仅是数据错误,而是电路结构的改变。例如:内部连线断开、LUT 表逻辑改变(与门变或门),直接导致卫星载荷功能瘫痪。

-

4. 硬件架构"三巨头"

基于 BM501-004 内部框图与系统架构图,重刷系统由以下三个关键部分组成:

| 角色 | 硬件实体 | 职责描述 |

|---|---|---|

| 被保护对象 | SRAM FPGA (BQ7K325T) | 负责主要的业务逻辑处理。它是受辐射影响的"重灾区",通过 SelectMAP 接口接受管理。 |

| 监控者 | 在轨维护控制器 (BM501-004) | 系统核心。通常为抗辐照加固的 ASIC 或反熔丝 FPGA(自身免疫辐射)。负责执行回读、校验、刷新指令。 |

| 标准源 | 非易失存储器 (BPI/SPI Flash) | 存储 FPGA 的正确配置比特流(Golden Copy)。Flash 抗辐照能力强,被视为不可篡改的"标准答案"。 |

5. 重刷工作模式原理

BM501-004 控制器通常通过以下两种模式形成闭环保护:

模式 A:盲刷 (Blind Scrubbing) ------ "简单粗暴"

-

原理: 不检测 FPGA 是否出错,利用内部定时器(如"刷新模块"),周期性地从 Flash 读取数据并强制写入 FPGA 配置区。

-

流程:

-

特点: 电路简单,无需回读逻辑。只要刷新频率 > 粒子撞击出错频率,即可保证系统大概率正常。

模式 B:回读校验 (Readback & Verify) ------ "精准治疗"

-

原理: 利用"回读模块"和"中断检测模块"进行实时体检,发现问题再修复。

-

流程:

-

回读 (Readback): 通过 SelectMAP 将 FPGA 内部现有的配置帧读回 BM501。

-

比对 (Compare): 计算回读数据的 CRC 校验码,或直接与 Flash 数据逐位比对。

-

纠错 (Correct):

-

若一致:无操作,继续下一帧检查。

-

若不一致(检测到 SEU):触发刷新逻辑,从 Flash 调取对应帧覆盖写入出错地址。

-

-

6. 关键接口技术:SelectMAP

-

接口定义: 一种并行配置接口(8-bit, 16-bit, 32-bit)。架构图中显示为 8-bit 连接。

-

为什么不用 JTAG?

-

JTAG 是串行接口,速度太慢。

-

在 SEU 发生后,FPGA 处于"带病工作"状态,必须在毫秒级时间内完成修复,否则可能导致错误扩散。

-

-

SelectMAP 优势: 高带宽、低延迟,是实现快速动态重构和实时修复的唯一选择。

7. 总结

"重刷"技术本质上是利用外部可靠的硬件(BM501 + Flash),构建了一个不知疲倦的"看门狗"。 它通过高速并行的 SelectMAP 接口,确保存储在易失性 SRAM FPGA 中的电路结构始终与设计初衷保持一致,从而在充满辐射的太空中维持系统的长期可靠运行。

以上就是本次的笔记内容。