8bit逐次逼近型SAR ADC电路设计成品 入门时期的第三款sarADC,适合新手学习等。 包括电路文件和详细设计文档。 smic0.18工艺,单端结构,3.3V供电。 整体采样率500k,可实现基本的模数转换,未做动态仿真,文档内还有各模块单独仿真结果。

引言

逐次逼近型模数转换器(Successive Approximation Register ADC,简称SAR ADC)因其结构简洁、功耗低、中等转换速率与高能效比,广泛应用于嵌入式系统、传感器接口与便携式设备中。本文基于一份8位SAR ADC的设计与仿真报告,从系统级视角出发,深入剖析其核心模块组成、协同工作机制与关键技术实现,旨在为硬件系统工程师与混合信号IC设计人员提供清晰、准确的功能级理解,而不涉及具体电路实现细节或敏感代码内容。

系统总体架构

该8位SAR ADC采用经典的四模块架构,包括:

- 采样保持电路(Sample-and-Hold, SH)

- 电容型数模转换器(Capacitive DAC, CDAC)

- 高速比较器(Comparator)

- 逐次逼近逻辑控制单元(SAR Logic)

这四个模块在统一时序控制下协同工作,完成从模拟输入到8位数字输出的完整转换流程。整个系统工作于5 MHz主时钟下,实现500 kSPS(千次采样每秒)的有效采样率,支持0~3.3 V全电压范围输入。

模块功能详解

1. 采样保持电路:高线性度信号捕获

为确保在动态输入条件下仍能获得高精度采样,系统采用栅压自举(Bootstrap)开关技术构建采样开关。相比传统传输门,该结构显著提升了开关导通电阻的线性度,从而减小了采样非线性误差,尤其适用于高分辨率ADC前端。

- 采样阶段:控制信号(CTL)为高电平,输入信号通过自举开关对采样电容充电。

- 保持阶段:CTL拉低,开关断开,采样电容维持电压值供后续比较使用。

仿真验证表明,该电路在3.8 MHz输入信号下仍能实现稳定、低失真的采样波形,满足8位精度对前端线性度的要求。

2. 电容型DAC:分段式电容阵列优化

DAC是SAR ADC的核心反馈单元,其精度直接决定整体转换性能。本设计采用4+4分段式电容阵列结构,将8位权重分为MSB(高4位)与LSB(低4位)两段,中间通过一个单位电容桥接。

优势分析:

- 面积与功耗大幅降低:传统8位二进制加权电容阵列总电容为255C(C为单位电容),而分段结构仅需31C,面积与功耗降低约8倍。

- 匹配性提升:高位电容不再需要超大尺寸,减小了工艺失配带来的非线性误差。

- 速度优化:总负载电容减小,加快了DAC建立时间,有助于提升转换速率。

DAC工作流程遵循二分搜索逻辑:初始时所有电容下极板接参考电压或地,上极板复位;随后根据SAR逻辑输出的每一位控制信号,切换对应电容下极板状态,使上极板电压逐步逼近输入信号。

3. 高速比较器:亚微伏级灵敏度

比较器负责判断当前DAC输出电压与采样保持电压的大小关系,其速度与精度是SAR ADC性能的关键瓶颈。

8bit逐次逼近型SAR ADC电路设计成品 入门时期的第三款sarADC,适合新手学习等。 包括电路文件和详细设计文档。 smic0.18工艺,单端结构,3.3V供电。 整体采样率500k,可实现基本的模数转换,未做动态仿真,文档内还有各模块单独仿真结果。

本设计采用三级交叉耦合差分结构,具备以下特点:

- 高增益与快速响应:适合在单时钟周期内完成判决。

- 低失调电压:实测在±5 μV输入偏移下即可可靠翻转,远优于1 LSB(≈13 mV)要求。

- 共模抑制能力强:在0.9 V共模电平下仍能准确响应差分输入变化。

该比较器输出直接驱动SAR逻辑,决定下一位的试探方向,是算法收敛正确性的保障。

4. SAR逻辑控制:同步状态机实现二分搜索

SAR逻辑本质上是一个8步状态机,每步对应一位(从MSB到LSB)的试探与锁定。其核心由两排D触发器构成:

- 上排触发器:实现移位功能,控制当前试探位。

- 下排触发器:寄存最终转换结果(B7~B0)。

工作流程:

- 初始化:复位信号(R)清零所有寄存器。

- 启动转换:置位信号(S)上升沿将MSB(B7)置为1,启动首次比较。

- 逐位逼近 :

- 比较器输出(CMP)反映当前DAC电压与输入电压的关系。

- 在每个时钟上升沿,SAR根据CMP决定保留或清除当前位,并将试探权移至下一位。

- 完成输出:8个时钟周期后,B7~B0即为最终8位数字码。

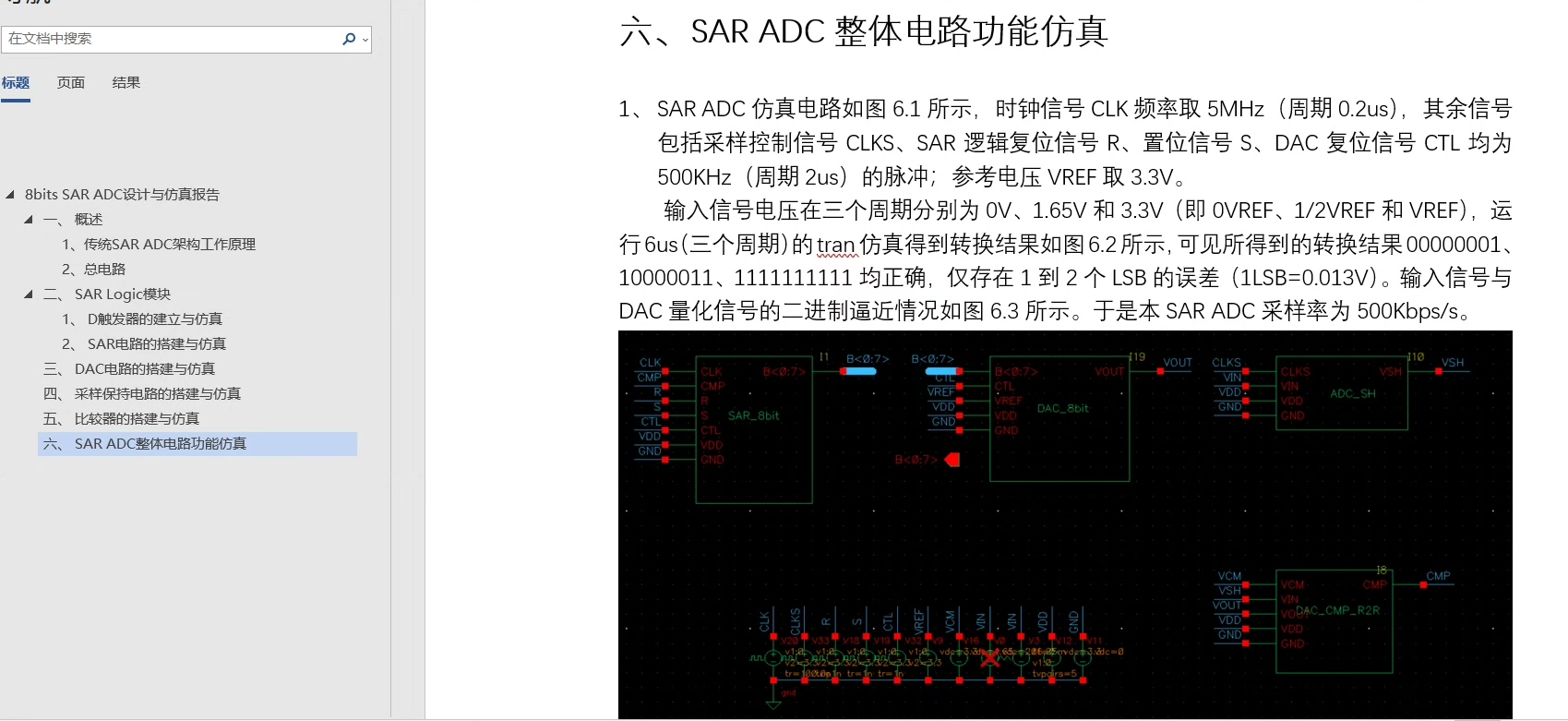

仿真验证显示,该逻辑在不同输入(0 V、1.65 V、3.3 V)下均能正确输出对应码值(如10000011对应1.65 V),误差控制在1~2 LSB以内,符合8位精度预期。

系统级协同与时序控制

整个ADC工作分为两个阶段:

- 采样阶段:由采样时钟(CLKS)控制,此时SAR逻辑时钟被屏蔽,DAC复位,输入信号被采样至保持电容。

- 转换阶段:采样结束后,主时钟(CLK)启用,SAR逻辑开始8步逐次逼近,每步一个时钟周期。

参考电压(VREF = 3.3 V)为全摆幅提供基准,确保0~VREF范围内任意输入均可被量化。系统通过精确的时序隔离与信号同步,避免了采样与转换阶段的相互干扰。

性能总结

| 指标 | 值 |

|---|---|

| 分辨率 | 8 bits |

| 采样率 | 500 kSPS |

| 输入范围 | 0 ~ 3.3 V |

| LSB大小 | ≈12.9 mV |

| 最大误差 | ≤2 LSB |

| 功耗/面积 | 因分段CDAC显著优化 |

结语

该8位SAR ADC设计通过分段电容阵列、栅压自举采样、高速低失调比较器与同步SAR状态机的有机结合,在保证精度的同时实现了面积与功耗的高效优化。其模块化架构清晰、时序逻辑严谨,为中低速高能效ADC应用提供了可靠的技术方案。未来可进一步集成数字校准算法,以补偿工艺偏差,提升有效位数(ENOB)。

注:本文基于功能描述与系统级分析撰写,未披露具体电路图、晶体管尺寸或版图实现细节,符合技术文档的保密与通用性原则。