3 LOGIC AND FAULT SIMULATION

仿真的用途有以下三个方面:

- 设计阶段:logic simulation就是用来看设计是不是符合spec以及设计中有什么错误(还能定位这些错误的位置)。

- 测试开发阶段:仿真故障电路的行为,这里用到的test patterns可以知道pattern的质量以及指导更多的向量生成。

- 电路故障仿真阶段:就是fault simulation,也被用在故障诊断中,定位硬件中的加工缺陷。

这一章分成两个部分:

- 前半部分:logic simulation

- 介绍logic circuit models,逻辑电路模型

- 流行的logic simulation技术

- 描述电路中可能出现的不良,怎么形成的,以及怎么在logic simulation中被检测到

- 后半部分:fault simulation(源于logic simulation,但很多技术衍生出来可以快速仿真故障行为)

- 介绍了一堆方法:serial, parallel, deductive, concurrent......

- 还有一些方法,牺牲准确性,降低执行时间(对大规模设计很有意义)

通过这一章学习可以知道主要的logic and fault simulation技术,在选择仿真方法以满足设计需求的时候,这些背景知识将会非常有价值。

3.1 INTRODUCTION

Simulation就是在物理构建之前预测电路设计的过程。对于数字电路,仿真有两个目的:

- logic simulation:确认设计符合spec(通常指没有故障的仿真)

- fault simulation:被专门用来仿真故障电路

- 给定测试向量集,确定是否能检测感兴趣的故障模型

- 也是ATPG中非常重要的部分

3.1.1 Logic Simulation for Design Verification

logic simulation的主要应用就是design verification,按照设计阶段分成:

- behavioral level or electronic system level (ESL):用ESL描述语言例如C/C++、SystemC、SystemVerilog

- register-transfer level (RTL) design stage:用硬件描述语言hardware description languages (HDLs) 例如Verilog、VHDL,描述一些模块例如:

- registers

- counters

- data processing units

- controllers

- the data/control flow between these blocks。以上2点不涉及到时序分析,所以也被叫做functional verification

- gate-level:其实到这一步就足够了

- switch-level:对于一些高性能的设计会有这一步,介于gate-level和transistor-level之间

- transistor-level:太耗时,通常用来表征一些cell libraries比如SRAMs和DRAMs

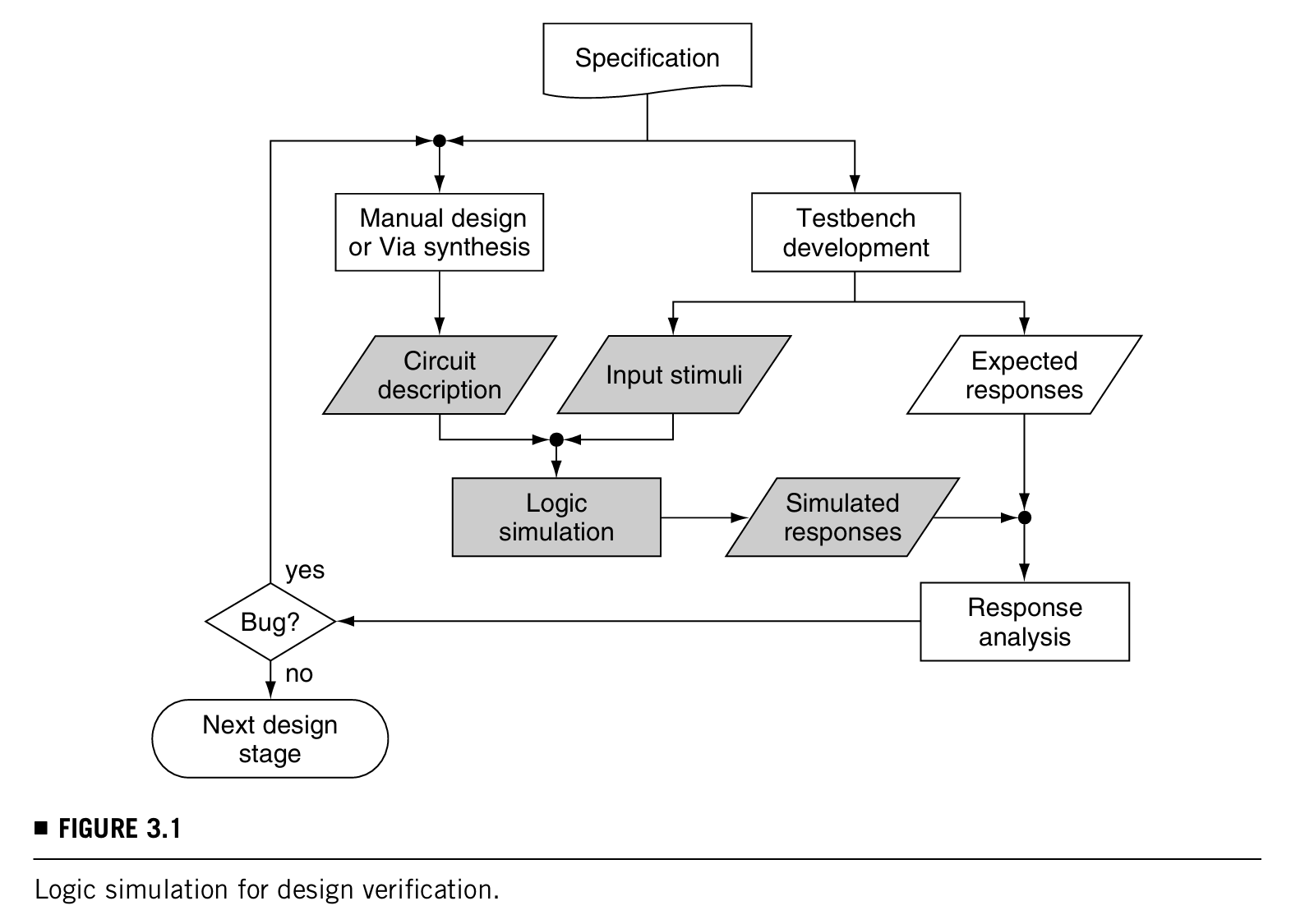

logic simulation流程如下图:

需要的东西:

- functional specification documents:包含了功能和性能方面的设计目标

- 每个设计阶段有对应的电路描述:

- behavioral design:ESL code

- RTL design:HDL code

- gate-level design:netlist

- switch and transistor-level design:SPICE models

- verification testbenches

- input stimuli

- simulated responses

上图是每一个design stage的验证流程。如果某个阶段出现的结果和预期不符,那么就重新设计或者修正,直到没有design bug出现,然后才能往下一个design stage走。

3.1.2 Fault Simulation for Test and Diagnosis

需要好好体会logic simulation和fault simulation的区别。logic simulation发现的错误有可能是designers或者EDA软件导致的。fault simulation是担心有些工艺过程出现的fault,所以先仿真看能不能有效的筛查出来,fault simulation通常假设设计是无误的。

fault simulation的用处主要体现在test 和diagnosis,也分成以下三类:

- 评估一组测试pattern的故障检测有效性,通常叫fault coverage

- 识别检测不到的故障,但又很重要的话,designer或者ATPG需要加额外的pattern提高fault coverage

- 帮助在不牺牲fault coverage的情况下实现压缩。ATPG的第一步就是从fault simulator开始

- 协助做fault diagnosis

3.2 SIMULATION MODELS

仿真模型在门级。

3.2.1 Gate-Level Network

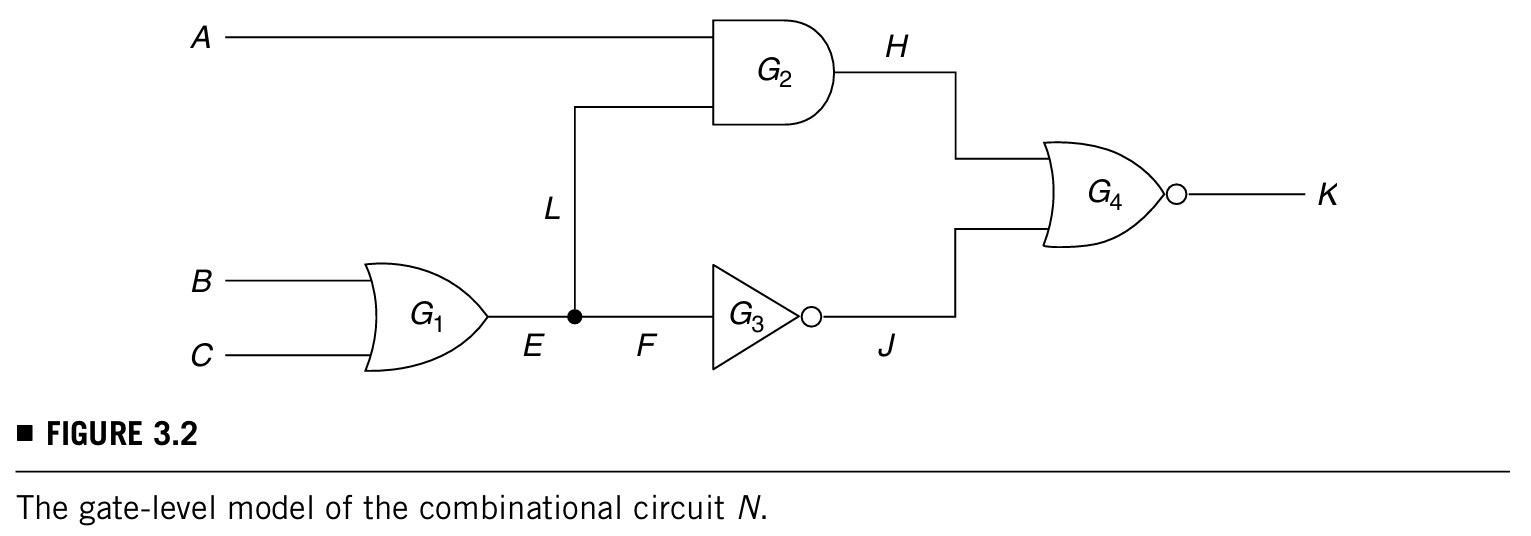

gate-level network就是一些逻辑门互连,例如下图(circuit N在这一章被一直用来举例):

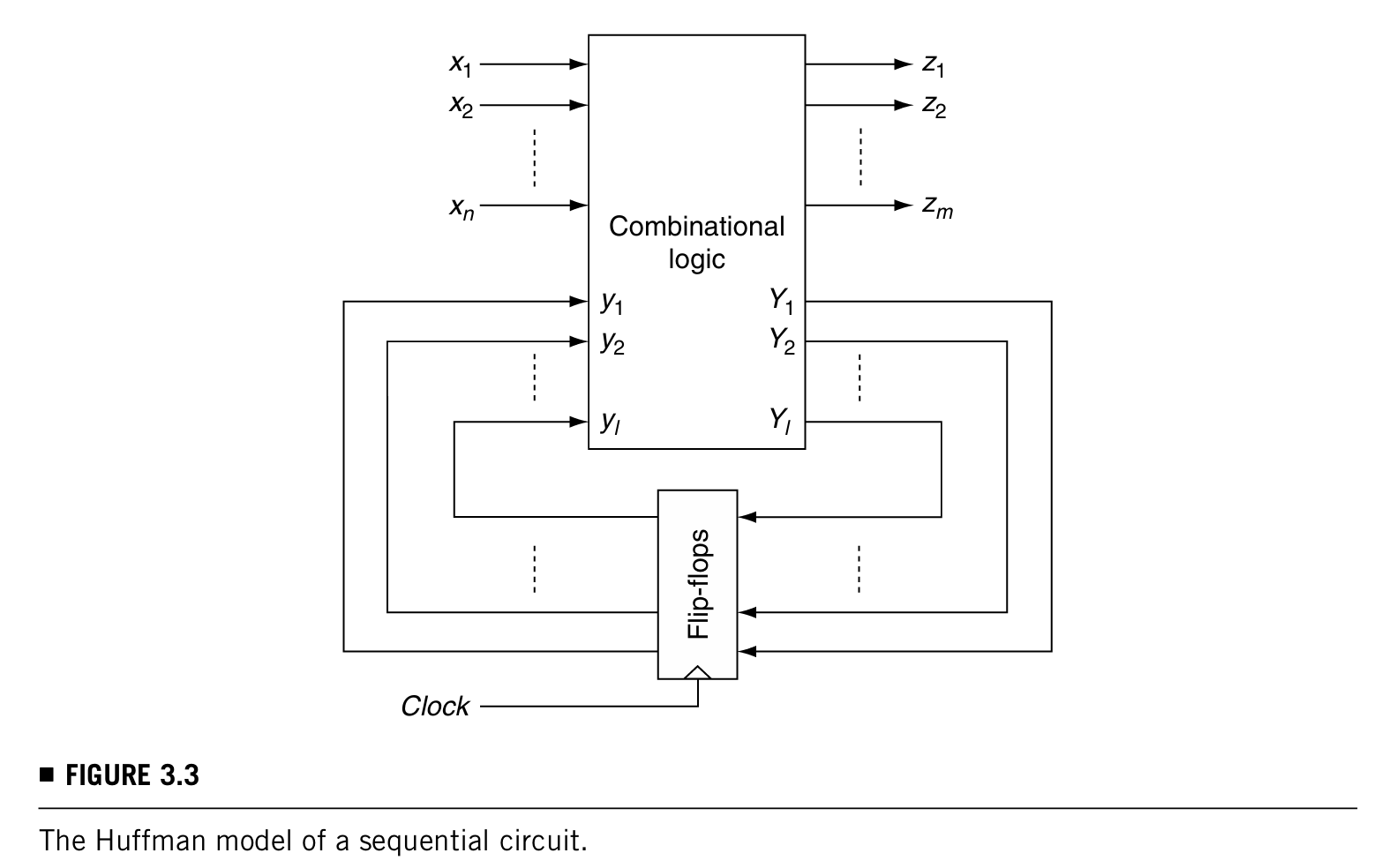

对应的布尔逻辑运算如下:

3.2.1.1 Sequential Circuits

Sequential circuits时序逻辑电路(大部分设计都是时序的)分为两种:

- 同步synchronous(这节讨论这种,因为更为广泛使用)

- 异步asynchronous

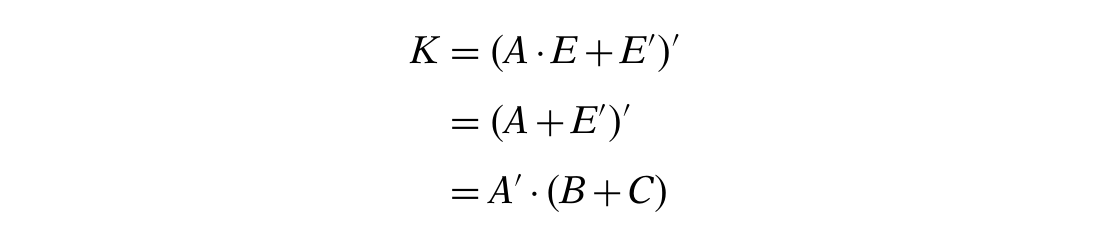

下图例为一个时序逻辑电路的Huffman model:

分为两部分:

- combinational logic

- flip-flops

combinational logic的输入分为:

- primary inputs (PIs) x1,x2,......,xn

- flip-flop的输出y1,y2,......,yl,也叫pseudo primary inputs (PPIs)

combinational logic的输出分为:

- primary outputs (POs) z1,z2,......,zm

- flip-flop的输入Y1,Y2,......,Yl,也叫pseudo primary outputs (PPOs)

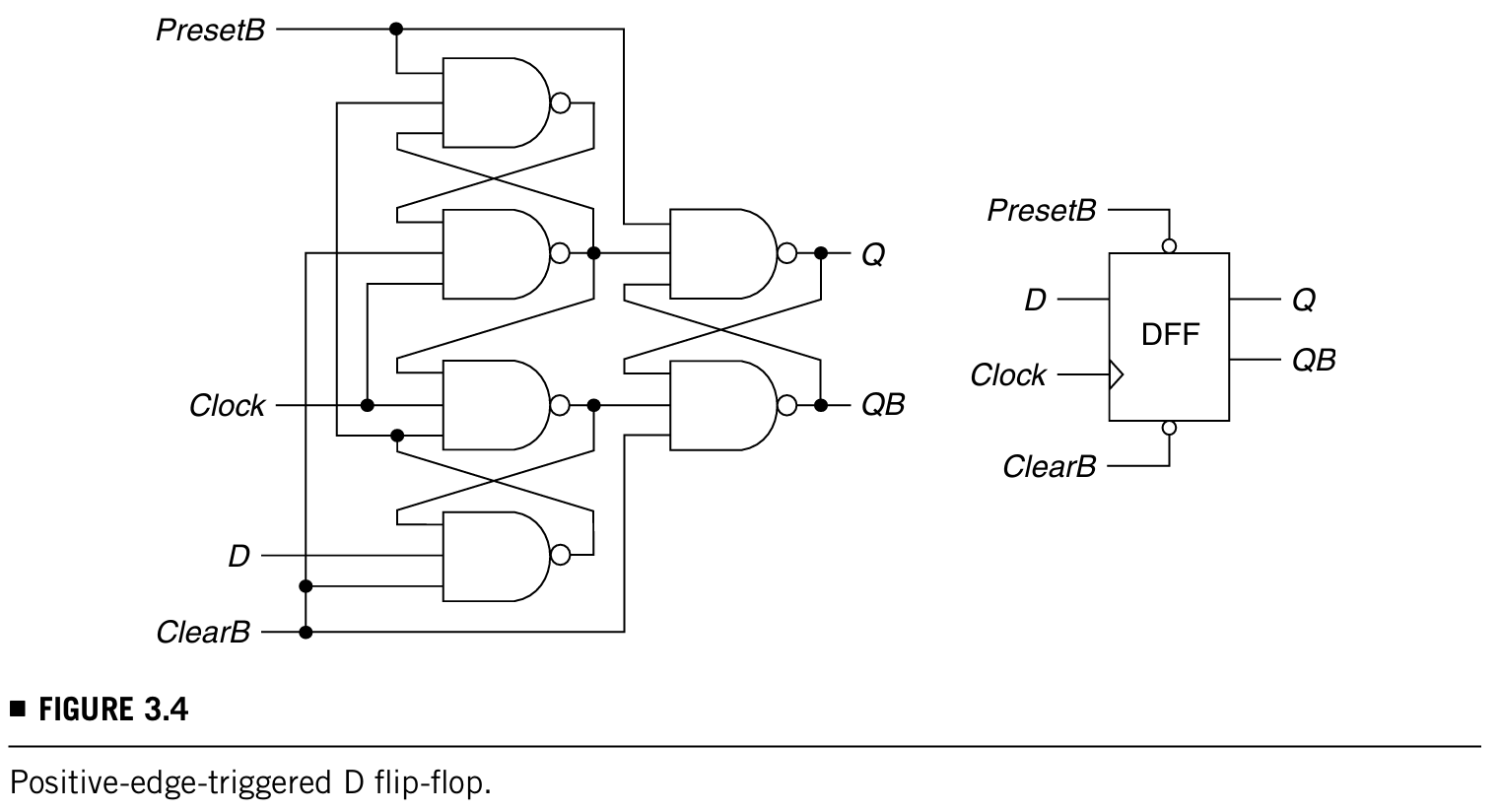

门级的描述中,flip-flop相当于一个functional block或者逻辑门的互连,如下图例(由D flip-flop组成的NAND,只是举个例子不具有实用价值):

输入输出:

- D:数据输入

- Clock:时钟(上升沿触发)

- PresetB:异步复位(低电平触发)

- ClearB:清零(低电平触发)

- Q:不取反

- QB:取反