AFE5832 LVDS时序介绍:

在调用HSSIO之前,首先需要简单了解下,本次实验要使用的ADC芯片,型号为AFE5832,是一款,德州仪器公司推出的,使用LVDS接口,速率模式为12位40MSPS或是10位50MSPS的32通道输出的ADC;

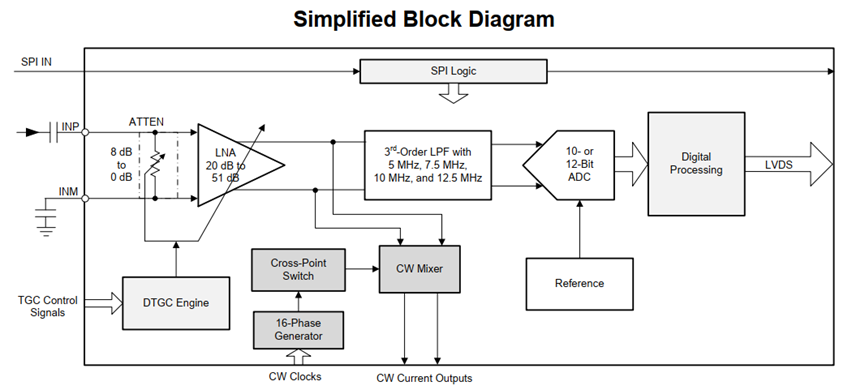

上图为单通道模块示意图,由SPI控制寄存器,LVDS输出数据,还有TGC等复杂增益控制;

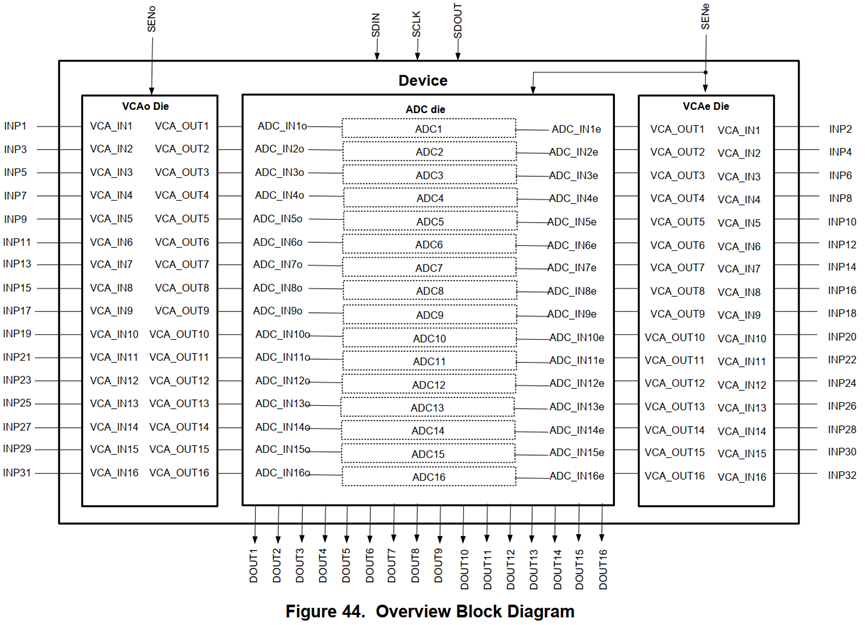

上图为一片AFE5832的输入输出通道和内部大致模块划分,一片AFE5832,共32个通道,但是可以看到上图中心框,ADC die中只有16个ADC,左右框分别是VCAo Die和VCAe Die,其中VCAo为奇数通道,VCAe为偶数通道,可以看到左右两侧INP1INP32,共32个输入通道,其中通道号为奇数的131通道连接到左侧VCAo Die,通道号为偶数的2~32通道连接到右侧的VCAe Die,然后下方输出的LVDS接口,则是输出16个数据通道;

该芯片是使用的通道复用的逻辑,将奇数通道1,偶数通道2,这两个相邻的奇偶通道的数据,一起共用了DOUT1这个通道,这个DOUT通道,例如使用10bit模式,第一个10bit 携带奇通道数据,下一个10bit携带偶通道数据,下一个10bit携带奇通道数据,同一个数据通道,两个奇偶通道分时复用;

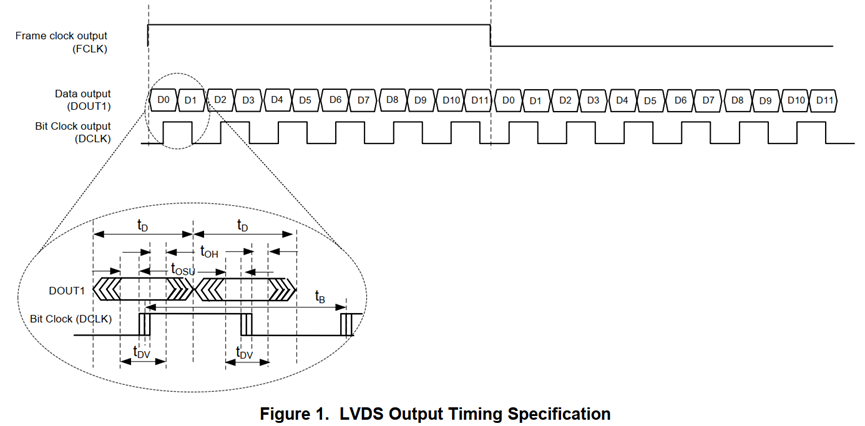

本次实验使用其10位50MSPS模式,LVDS接口时序如下:

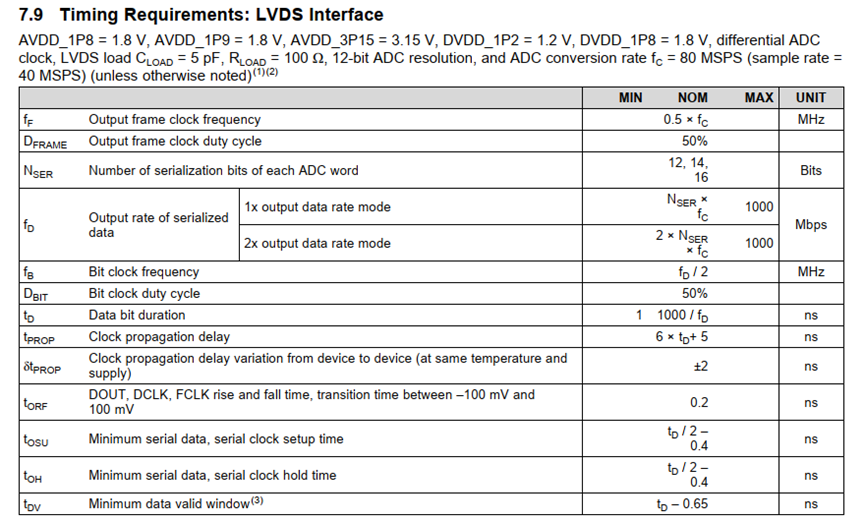

图中是12bit的时序,10bit同理,比特时钟边沿对准数据眼中心,帧时钟边沿对准数据眼边沿;

按照上图中奇偶通道复用的逻辑,此时FCLK帧时钟为高时,是奇(偶)通道数据,FCLK帧时钟为低时,是偶(奇)通道数据;

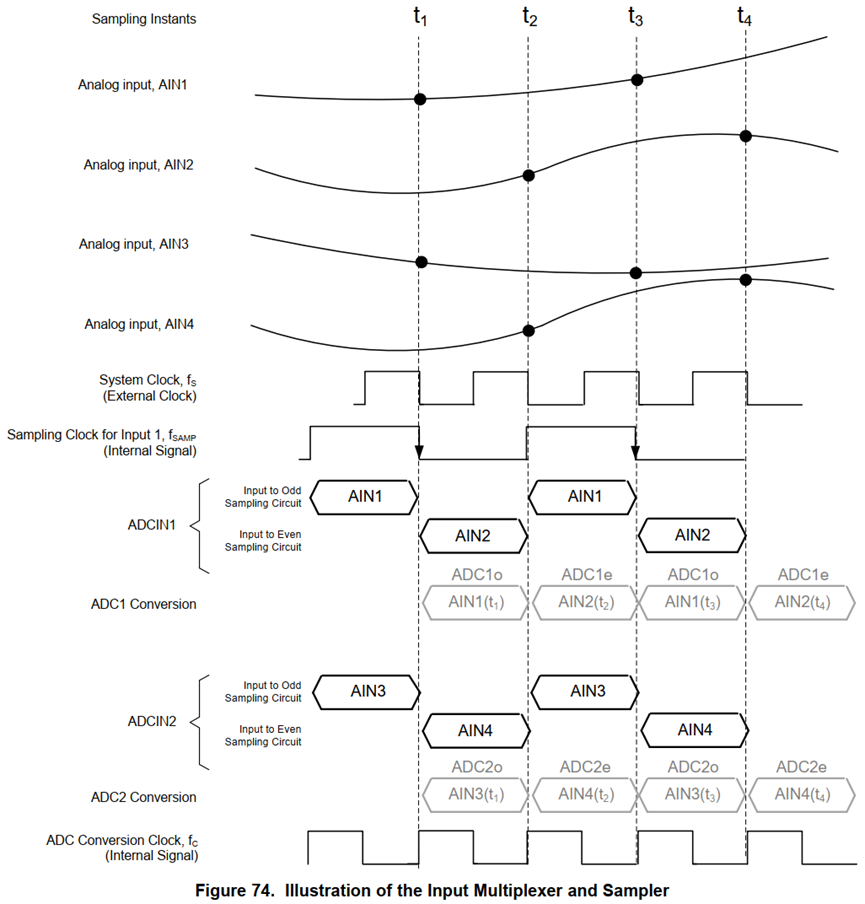

从上图也能看出来,数据是两个相邻的奇偶通道数据分时使用;

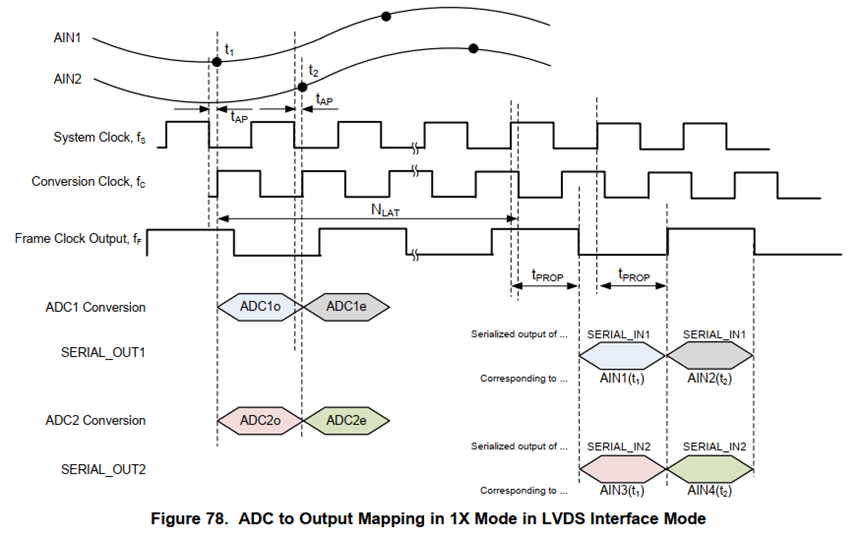

1x数据模式入上图;

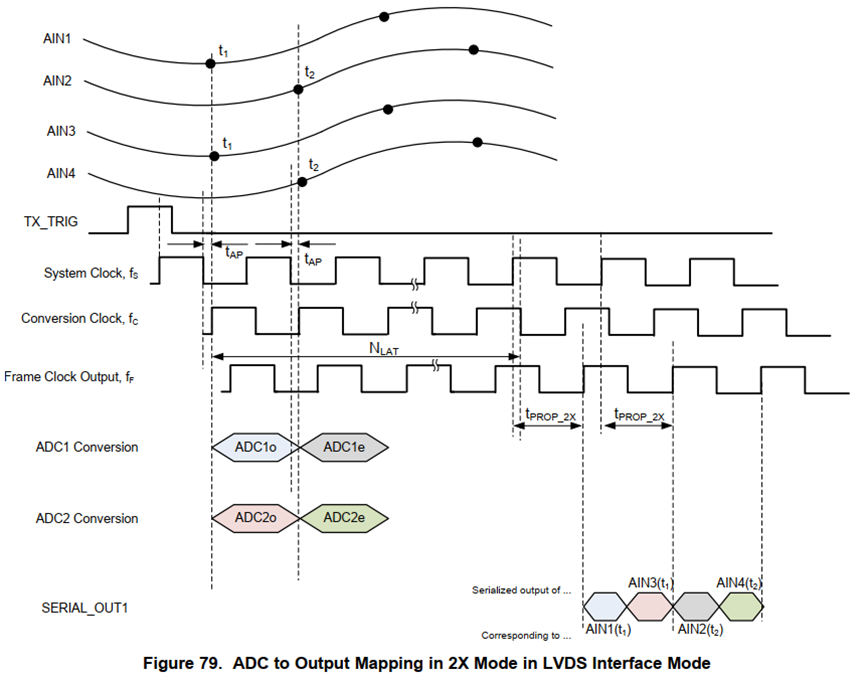

2x数据模式入上图;

1x和2x的区别,是1x,是1个LVDS通道携带2个ADC通道数据,2x,是1个LVDS通道携带4个ADC通道数据,本次实验使用默认的1x模式,

上图中,默认设置是使用12bit 40MSPS模式,若改为10bit 50MSPS模式,那么采样率为50M,fc = 100MSPS,在1x数据模式中可以看到,fc是ADC转换时钟,1x模式中,fc的速率是帧时钟的2倍;

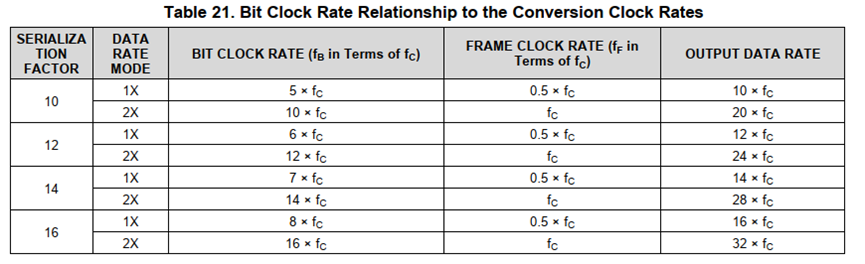

上图为序列化因子和数据模式,和LVDS速率的关系;

其中fc = 100M,

那么根据上表,本次使用使用10序列化因子,50M帧时钟,1x数据模式,

此时比特时钟为5fc = 500M,

帧时钟为0.5 fc = 50M,

数据输出速率为 10*fc = 1000M,

使用以上参数,就可以去配置HSSIO的细节了,关于AFE5832的更详细的使用与操作流程,在最后进行讲解;

本文章由威三学社出品

对课程感兴趣可以私信联系