3.4.2 Parallel Fault Simulation(并行故障仿真)

并行仿真,和逻辑仿真一样,就是同时能处理多位,比如32-bit CPU可以同时处理32位数。

并行故障仿真分为两类:

- parallel fault simulation

- parallel pattern fault simulation

3.4.2.1 Parallel Fault Simulation

对于w-bit的数据位宽,w − 1 bits用于w − 1个故障电路,剩余的1 bit用于fault-free电路。

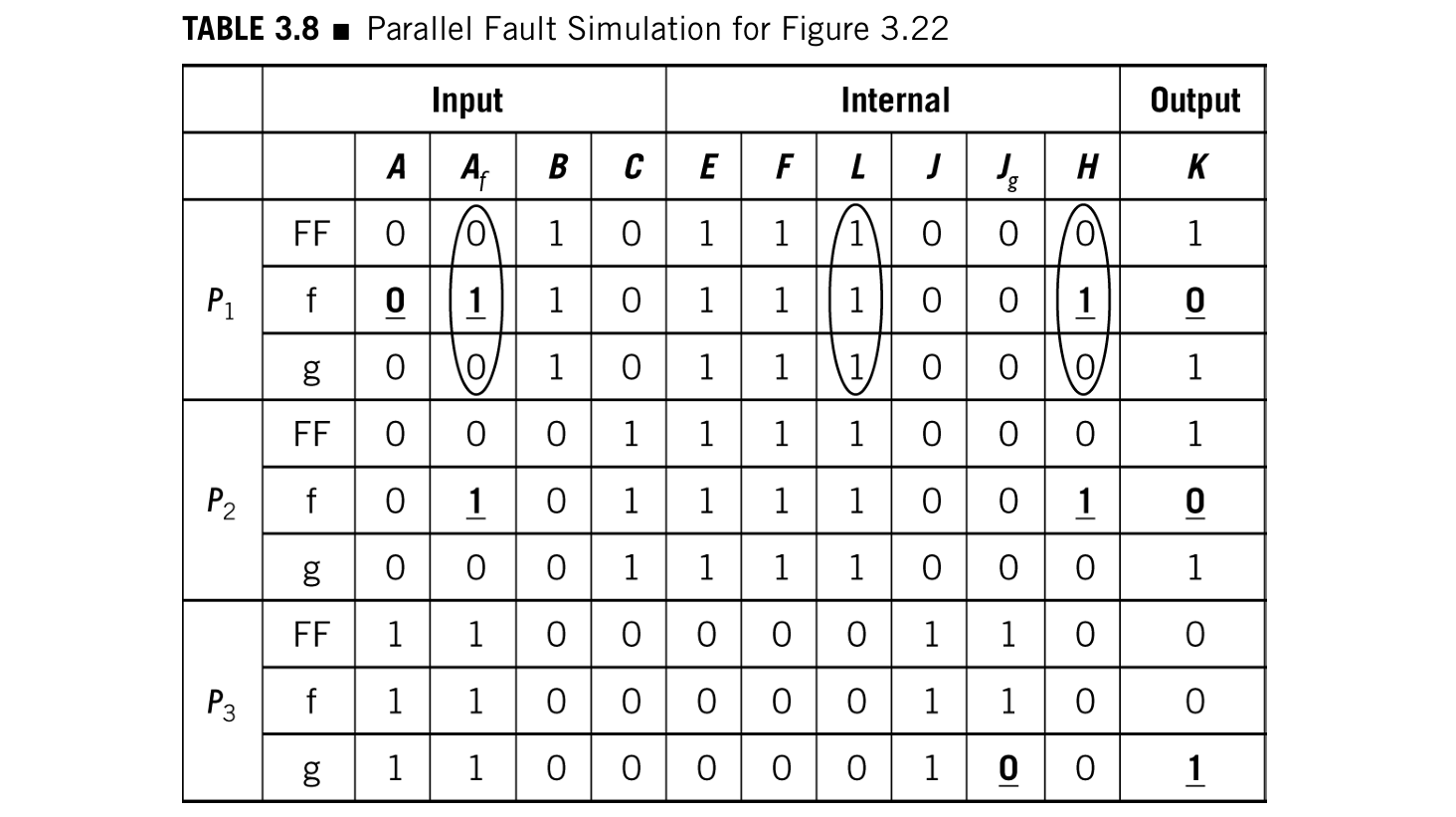

还是用串行故障仿真的例子,仿真过程如下表(假设数据位宽是3位,一个fault-free两个针对fault):

上面的并行仿真只需要仿真3次,只需要1个simulation pass。所以相对于串行故障仿真,能节省2/3的仿真时间。

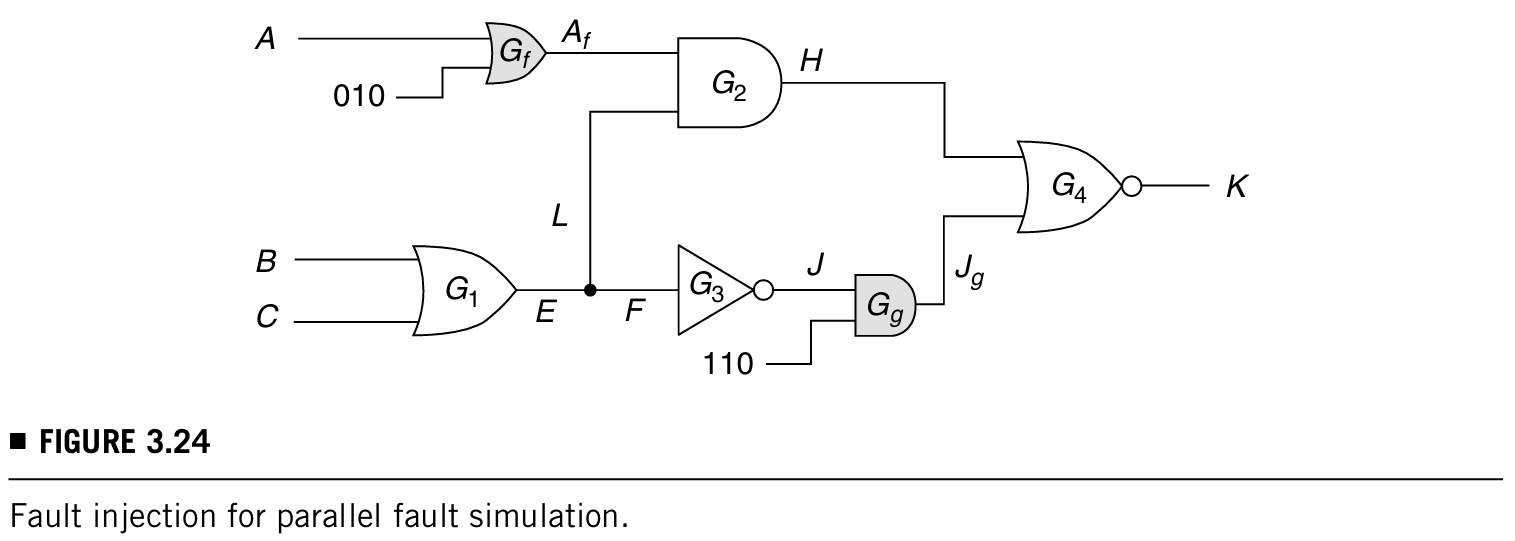

并行仿真可以通过插入额外的逻辑的方式插入故障,如下图:

Af通过插入一个或门,Jg通过插入一个与门实现,而且这两个门的插入还不会影响fault-free电路的正常工作。

parallel fault simulation的缺点:

- 只能用在unit or zero delay models,因为故障都是并行同时仿真的,没办法用delay models

- 只有在所有故障都仿真完才能终止仿真,比如不能在P1完成时候停止仿真

parallel fault simulation是仿真大量故障的test patterns的初始阶段的最佳选择。

3.4.2.2 Parallel-Pattern Fault Simulation

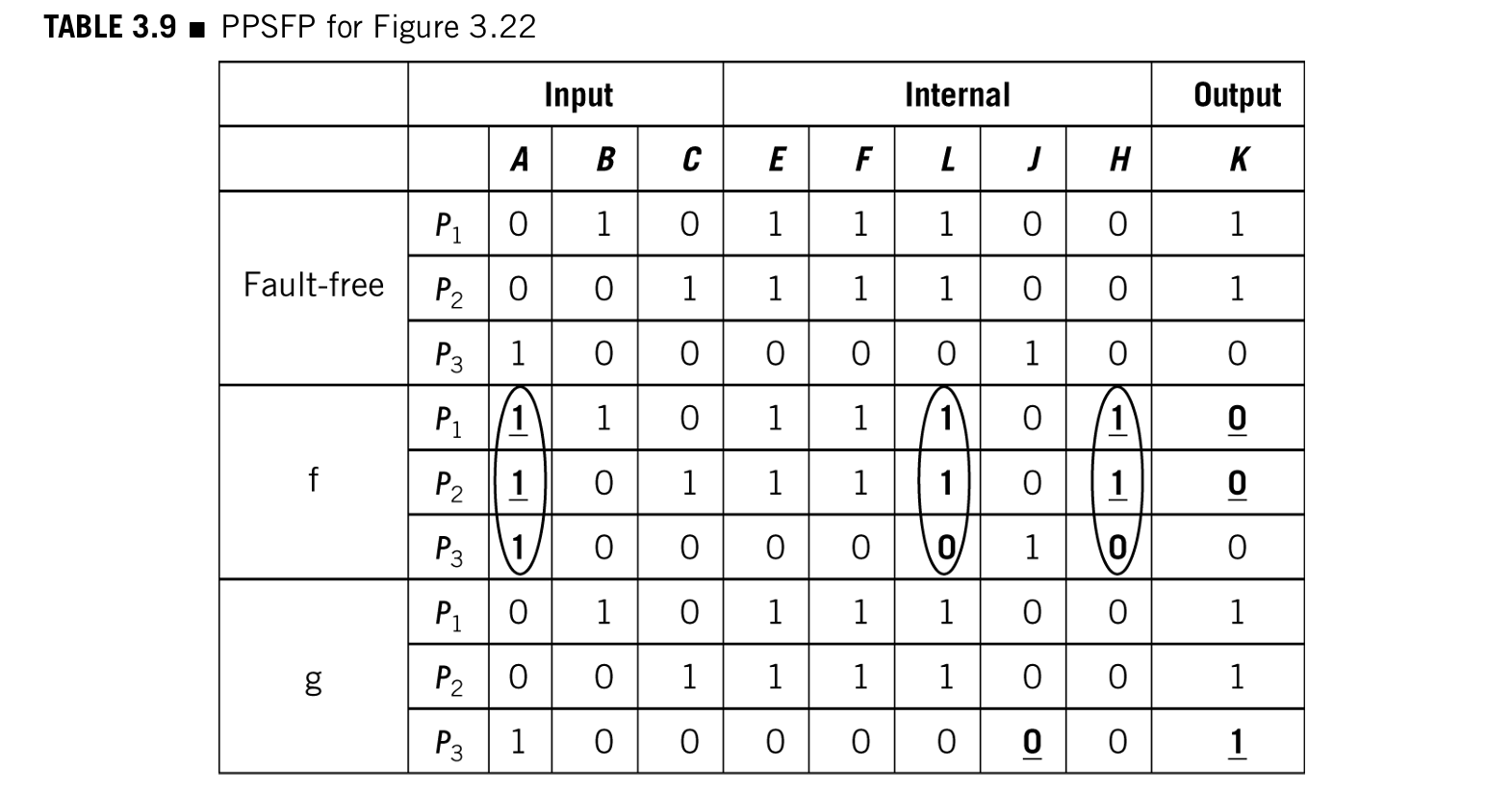

parallel-pattern single-fault propagation (PPSFP) :这一节的parallel-pattern fault simulation是这样,w-bit的数据位宽,w个测试pattern同时并行输入,每个pattern占一位。(其实从故障仿真的名字前缀就可以理解仿真的方法是什么样的)

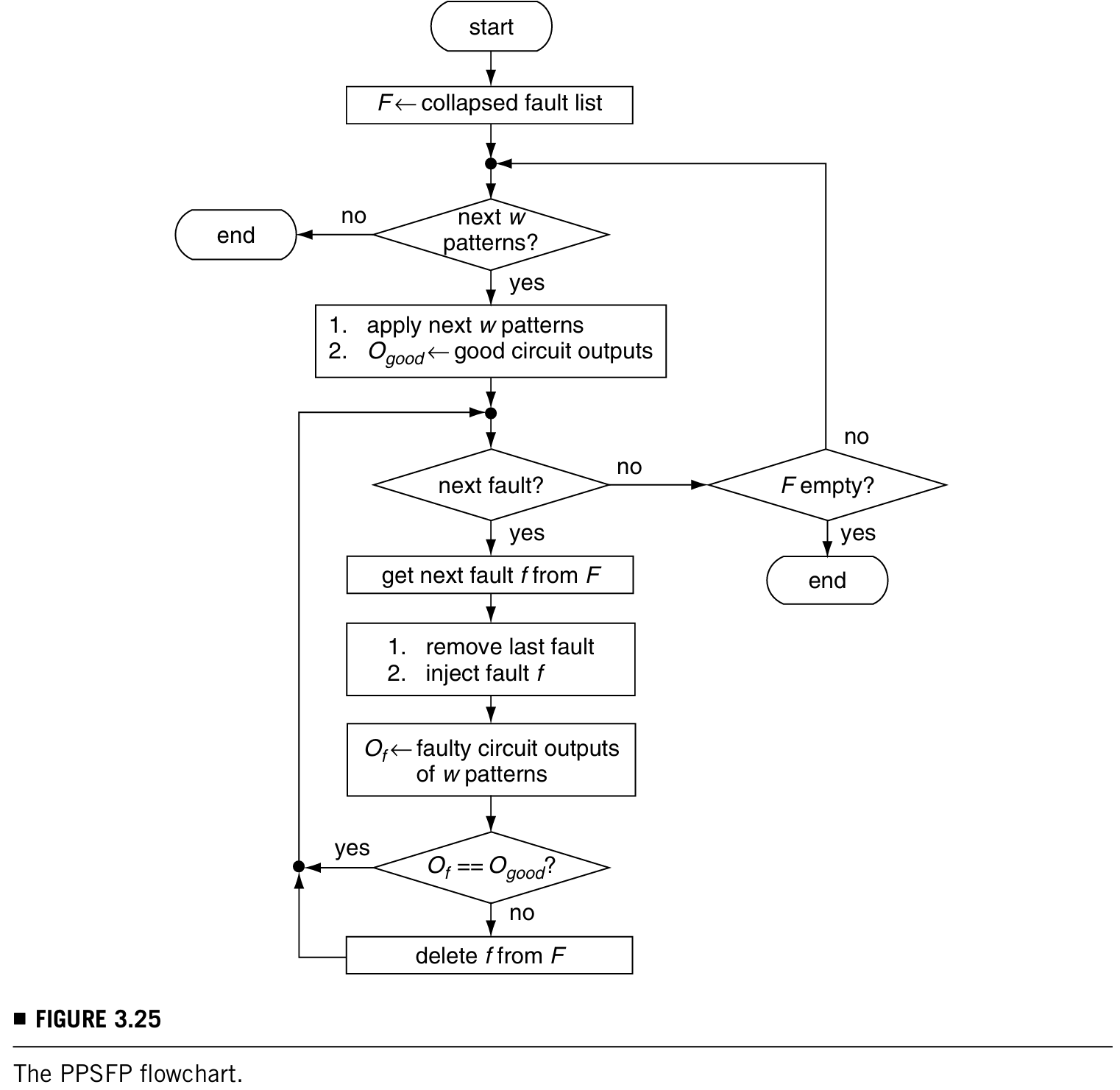

先仿真fault-free电路,记下它的输出,然后每次仿真一个故障电路,与fault-free输出对比确认故障是否被检测到。PPSFP的过程如下图:

*在PPSFP中,故障的插入是通过控制信号的上升和下降实现的(还记得parallel fault simulation是通过插入额外的逻辑门实现的吗)

下图是PPSFP的流程图,和并行仿真一样,第一步也是fault collapsing,得到fault list F。

PPSFP的优缺点:

- 优点:最适合用在测试序列中较晚发生的test pattern上(上一节说过的Parallel fault simulation不能实现,因为这个方法一定是等所有的fault仿真完成之后仿真才能停止)。

- 缺点:无法用在时序逻辑电路中,因为时序电路需要电路的前一个状态,而在这种仿真方式中pattern都是并行输入的,没法考虑电路的前一个状态。