3.3.4 Hazards(应该是指电路中的冒险)

hazards:因为汇集信号通路之间可能延迟不同,就会造成传输中出现不应该出现的瞬态脉冲或干扰信号。

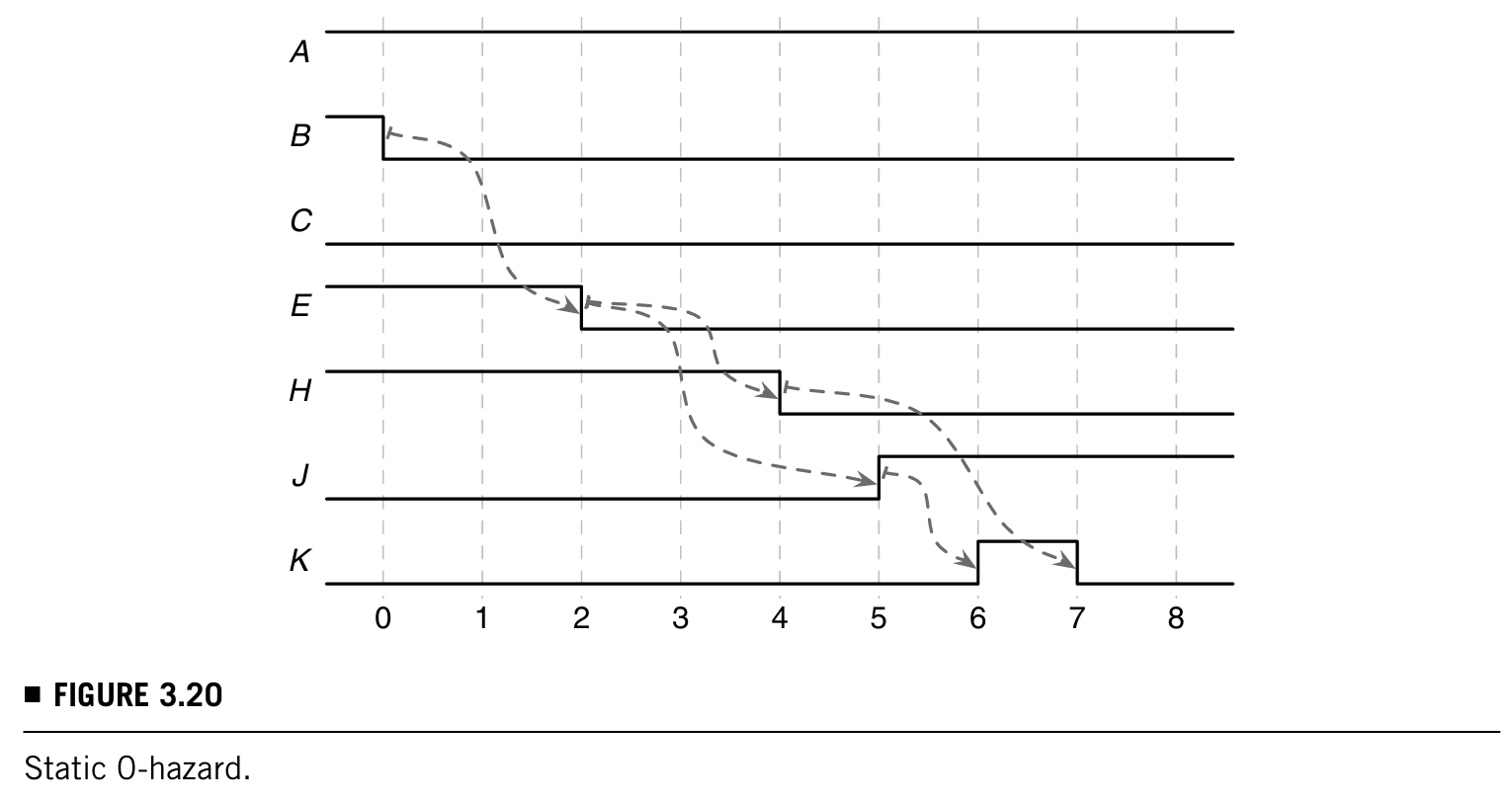

还是用电路N举例,如下图:

输入向量ABC从110变为100,反相器的nominal delay是3 ns,其他门的nominal delays是2 ns,本来输出K是应该保持0不变的,但是因为延迟,仿真就会出现一个假脉冲,这种叫static 0-hazard。

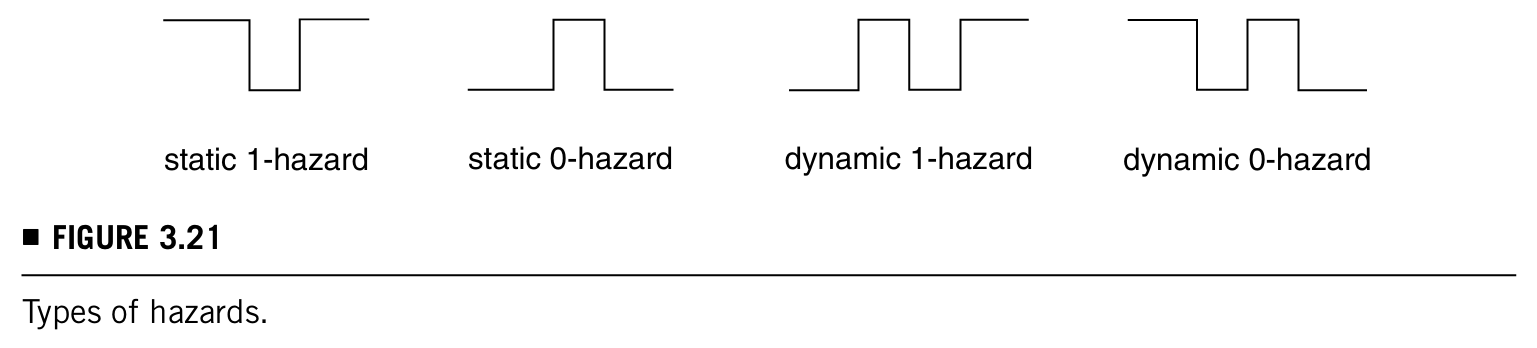

hazard分为以下几类,可见下图:

- static hazard:

- static 1-hazard

- static 0-hazard

- dynamic hazard:

- dynamic 1-hazard

- dynamic 0-hazard

*数字0或者1可以理解为本来应该是0或者1

*图中虽然只画了一个脉冲,但是实际情况可能会出现多个脉冲

如果时间信息是有的,那么Hazard detection就会很明确,但是实际芯片有工艺偏差,导致出现时序偏差,这种方法的准确性就无法保证。

下面分节讨论多值逻辑的hazard detection技术。

3.3.4.1 Static Hazard Detection

如果不知道具体的delay时间信息,那么就没办法知道准确的冒险发生的时间点,解决这个困难的方法就是,在每一个输入信号传输中加入一个不确定间隔,例如,0 → 1变成0 → u → 1,1 → 0变成1 → u → 0,因为0u1就代表001或者011,这也真实地反映了我们不知道转换发生的具体时间点。

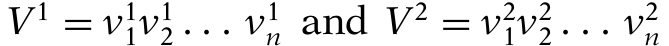

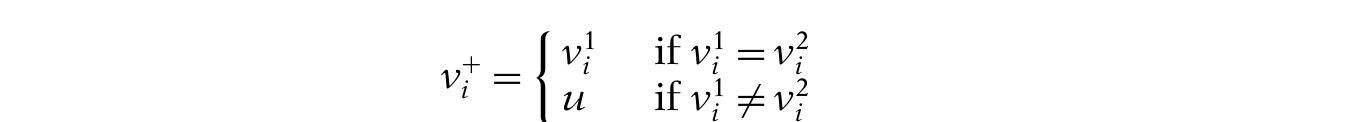

用公式来表示的话,假设两个连续的向量是:

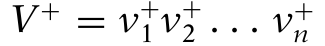

中间加入的不确定状态的间隔向量是:

那么有下面的规则:

那么如果有0u0或者1u1向量被从输出检测到,就代表检测到了static hazard。

以电路N举例,V1 = 110,V2 = 100,根据上面的规则,就有V+ = 1u0,仿真V1 V+ V2这三个向量得到的K = 0u0,那么一个static 0-hazard就被检测出来了,和图3.20得到的结论一样。

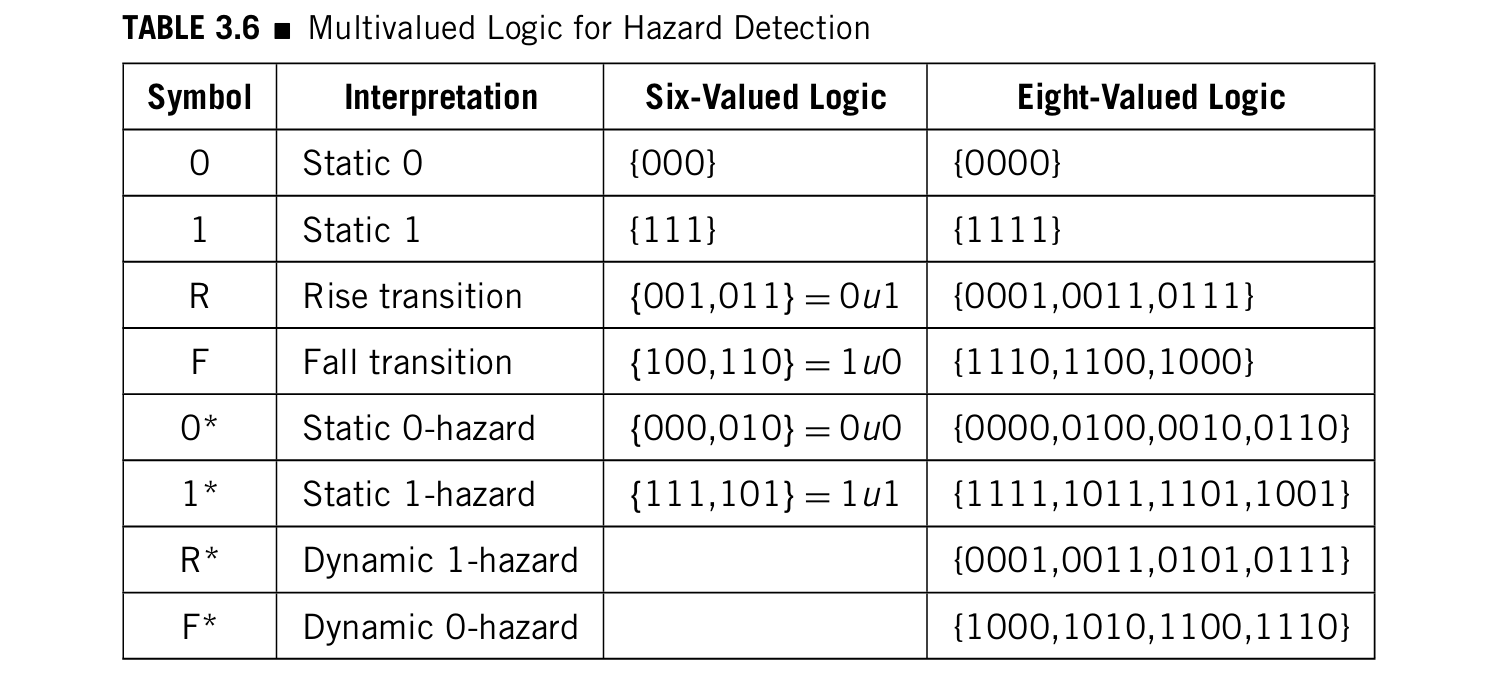

基于这个方法,还可以得到six-valued logic(3比特)下探测hazard的方法,相关的符号和解释如下表:

3.3.4.2 Dynamic Hazard Detection

dynamic hazard是在0-to-1或者1-to-0转换过程中发生的不想发生的状态,为了去检测dynamic hazard,要用到eight-valued logic(4比特),它的标志和解释如表3.6。

3.4 FAULT SIMULATION

Fault simulation是比logic simulation更加复杂的,因为logic simulation只仿真没有错误的电路,但是fault simulation是仿真各种故障下的电路。

如果一次只仿真一个故障,那么计算量大概和电路规模、测试向量的数量、modeled faults的数量成正比。而电路规模和modeled faults的数量基本成比例,那么fault simulation的时间复杂度可以评估为O(pn^2)(for p test patterns and n logic gates),这对于大规模的电路是不可能的。

下面几节围绕stuck-at fault model讨论各种仿真技术。

需要注意两个名词的区分,这两个词在大多数情况下是可以互换的,但要注意:

- test vectors:logic simulation更爱用,因为是designers为了设计验证而写

- test patterns:fault simulation更爱用,因为它通常用来与ATPG对test pattern分级

3.4.1 Serial Fault Simulation(串行故障仿真)

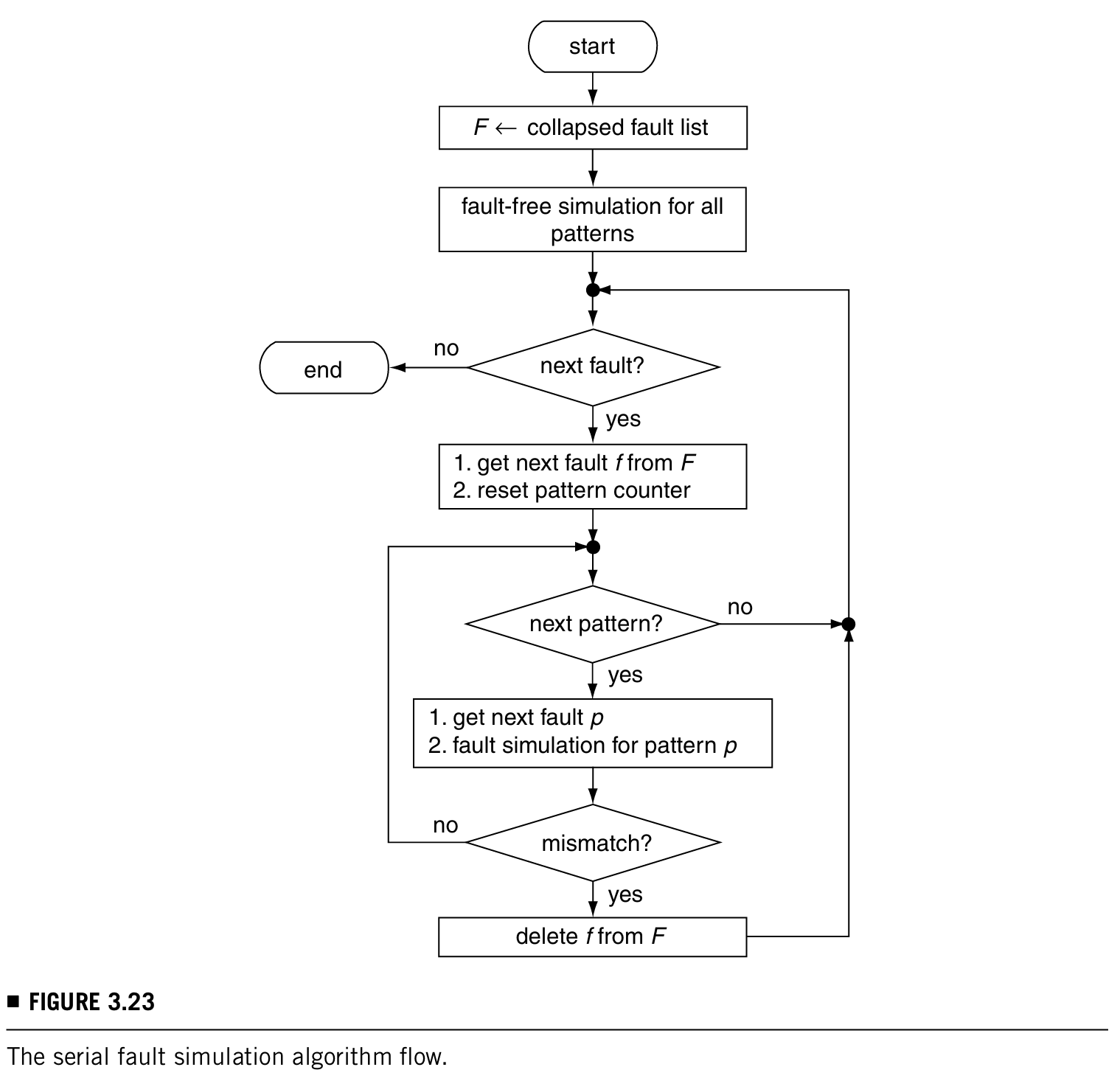

Serial fault simulation的流程,包括:

- fault-free circuit simulations

- 进行fault-free logic simulation,得到fault-free电路的响应

- fault-free电路响应被存起来,用来在之后确定test pattern是否能检测到fault

- faulty circuit simulations(一次仿真一个故障)

- 对初始的电路进行fault injection操作,让电路模拟成有故障的样子

- 故障电路在仿真的时候会根据提供的test pattern产生故障响应,联系第1点的第二条,与fault-free响应对比,判断pattern行不行

上面的步骤每次仿真重复一遍,直到fault list都被仿真过为止。

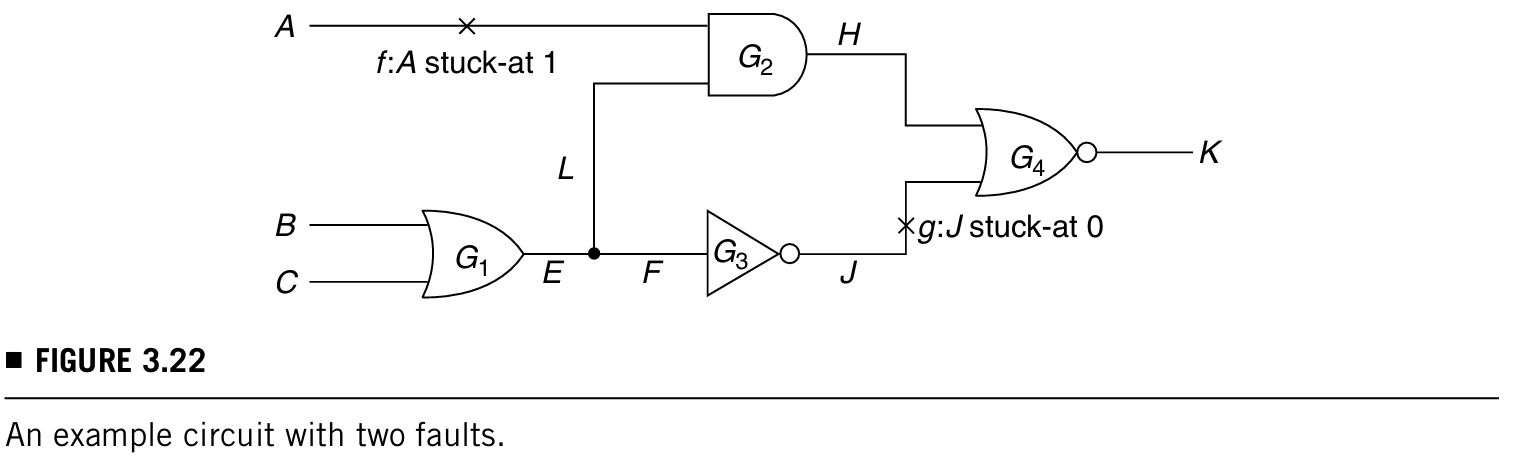

还是用电路N举例,假设fault list有两个:A stuck-at one (用 f 表示) and J stuck-at zero (用 g 表示)。如下图:

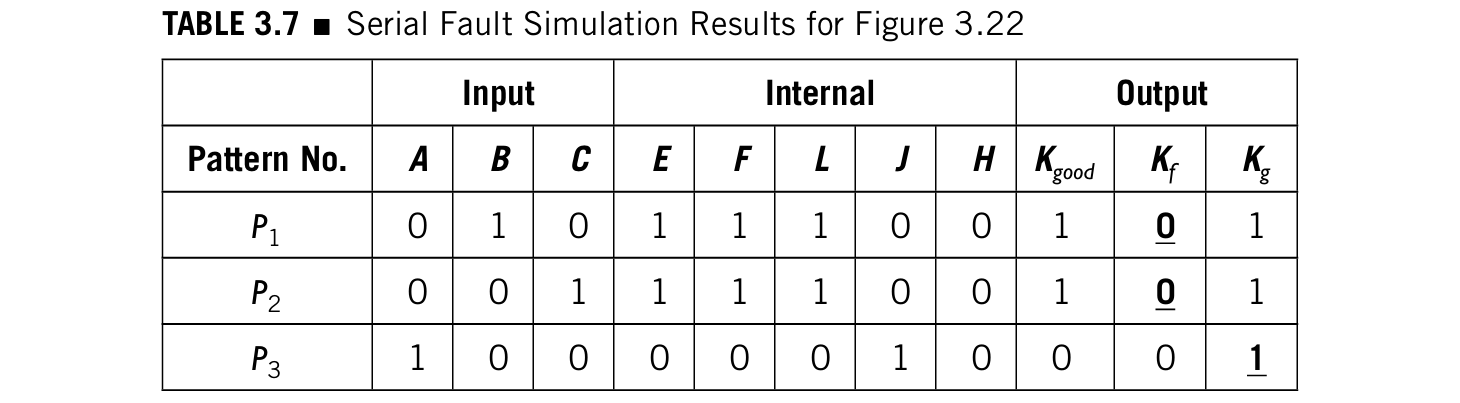

fault-free和两个faulty电路响应如下表总结(具体怎么玩儿的看原文或者自己推,easy):

这里有两个概念:

- simulation passes:上面这个例子跑了9次仿真,fault-free和两次faulty一共3次仿真叫做3个simulation passes,每次仿真各跑3次,也就是3个向量P1、P2、P3

- fault dropping:P1和P2都能检测到Kf故障,用一个就行,这就叫fault dropping(有点像故障坍塌但不是,注意区分)。需要注意的是fault diagnosis不能这样做。

serial fault simulation的流程如下图所示:

*注意要在第一步做一个fault collapsing,减少fault list F。

serial fault simulation的优缺点:

- 优点:

- 流程简单,易于完成

- 能仿真很多类型的fault models

- 缺点:性能差一点,下一节有并行故障仿真,会提高仿真性能