2026 年,AMD 在 FPGA 领域持续发力,不仅宣布扩充 Kintex UltraScale Gen 2 系列中端 FPGA 产品阵容,丰富行业应用选择,更重磅推出全系列 FPGA 及自适应 SoC 长期供货计划,将多款核心产品生命周期大幅延长至 2040、2045 甚至更久,以双维度布局夯实其在嵌入式、工业等领域的市场竞争力。

AMD升级Kintex UltraScale+ FPGA

AMD在2026年欧洲集成系统展(ISE 2026)(https://www.iseurope.org/)上发布了第二代中端Kintex UltraScale+现场可编程门阵列(FPGA)产品系列。与上一代产品相比,新一代FPGA系列拥有更强大的内存和安全性能,并为视频采集/播放、测试测量、工业自动化以及包括机器视觉和机器人技术在内的高级成像应用提供了更高的带宽。

AMD Kintex UltraScale+ Gen 2 FPGA系列(https://www.amd.com/en/products/adaptive-socs-and-fpgas/fpga/gen2/kintex-ultrascale-plus.html)基于台积电高效节能的 16 nm FinFET 架构(与 AMD 的所有 UltraScale+ FPGA 相同),与其他 Kintex 产品在价格、性能和功耗之间取得平衡有所不同。

与 Kintex UltraScale+ 系列不同,第二代产品拥有更低的查找表 (LUT) 开销。它支持 32 位 LPDDR4X、LPDDR5 和 LPDDR5X,可通过 AMD 专有的 XP5IO 接口(主要用于 Spartan UltraScale+ FPGA)连接多达六个 4266 Mb/s 的控制器。因此,第二代产品支持低延迟直接内存访问 (DMA),这意味着能够实时传输更大的数据流。

这些硬内存控制器与片上 27 Mb UltraRAM (URAM) 和 18.1 Mb Block RAM (BRAM) 配合使用,与上一代产品相比,内存带宽提高了 5 倍,从而在重负载下保持稳定的同时,提供可靠的视频帧传输和精确的定时/同步。

图 1:AMD Kintex UltraScale+ Gen 2 FPGA(来源:AMD)

图 1:AMD Kintex UltraScale+ Gen 2 FPGA(来源:AMD)

更高的内存带宽为边缘智能提供动力

新型 AMD Kintex UltraScale+ FPGA 的内存中心架构(特别是内存控制器)释放了查找表 (LUT) 空间,可用于特定应用逻辑。这些释放出来的模块随后可用于自定义算法。

增强型片上 51MB 内存(URAM+BRAM)有助于将数据流更靠近计算资源,从而提高 DSP 资源的利用率。因此,尽管第二代 FPGA 的 LUT 数量约为 22.5 万,而上一代产品最多可达 84.2 万个 LUT,但其片上有效智能水平却有所提升。

剩余的逻辑块/查找表 (LUT) 也可用于创建激励向量,以高速驱动被测器件 (DUT) 引脚,从而在晶圆分选或最终测试期间检测缺陷。片上存储器则用于捕获故障。这两者在存储器和片上系统 (SoC) 测试中都至关重要。

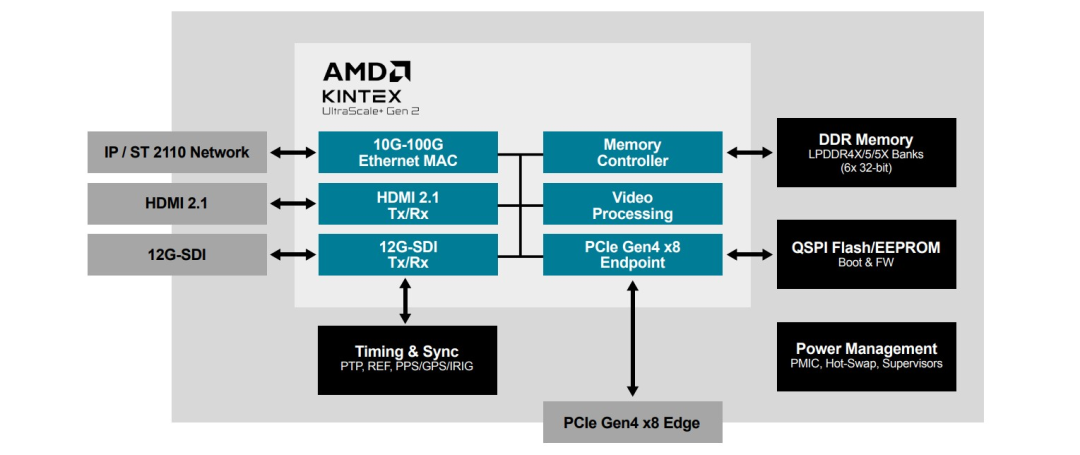

I/O接口专为视频应用而设计

除了支持设备端本地智能外,AMD Kintex UltraScale+ 还配备了与上一代产品相同的 Gen4 PCIe 接口,支持多达 8 通道未压缩的 4K60 视频或 48 通道 1080p60 视频。该 FPGA 系列还配备多达 24 个 GTY 收发器,数据传输速率高达 32.75 Gb/s。这两个接口均可实现 4K AV-over-IP 多媒体流传输以及远程制作。

PCIe接口还支持将UHD视频流传输到服务器端GPU,以运行实时AI推理。此外,FPGA最多支持四个HDMI端口、16个12G-SDI端口和两个ST 2110 over 100 GE端口,可满足广播和视频播放/采集应用的需求。

第二代 FPGA 支持 3.2 Gb/s MIPI D-PHY 和高达 32MP 分辨率的成像。配合内存控制器,第二代系列 FPGA 还可通过云端实现实时诊断成像应用。这些接口使得 AMD Kintex UltraScale+ FPGA 非常适合多摄像头、实时视频处理和机器视觉环境及应用。

图 2:AMD Kintex UltraScale+ Gen 2 FPGA 系列框图(来源:AMD(https://www.amd.com/content/dam/amd/en/documents/products/adaptive-socs-and-fpgas/fpga/ultrascale-plus/kintex-ultrascale-gen2-broadcast-solution-brief.pdf))

图 2:AMD Kintex UltraScale+ Gen 2 FPGA 系列框图(来源:AMD(https://www.amd.com/content/dam/amd/en/documents/products/adaptive-socs-and-fpgas/fpga/ultrascale-plus/kintex-ultrascale-gen2-broadcast-solution-brief.pdf))

安全性升级

Kintex UltraScale+ Gen 2 FPGA 系列是其前代产品的升级版,采用后量子密码学 (PQC) 和经 NIST 认证的算法,支持 CNSA 2.0 安全标准。此外,Kintex UltraScale+ Gen 2 FPGA 还扩展了认证设备操作、比特流加密、AEC-GCM 解密以及物理不可克隆函数 (PUF) 等反克隆机制。

除了知识产权保护、防篡改和网络安全之外,延长支持期限也是一项优先事项。AMD延长了其所有 FPGA 产品组合的生命周期,将 UltraScale+ 系列的支持期限延长至 2045 年。

此外,工程师可以通过 AMD 的 Vivado 和 Vitis 工具,将现有 IP 核从之前的 Kintex FPGA 无缝移植到新的第二代 FPGA。这些工具的仿真支持预计将于 2026 年第三季度推出。具体而言,Vivado 有助于在目标时钟频率内实现设计性能目标,这是FPGA设计中最耗时的步骤之一。

Kintex UltraScale+ Gen 2 系列将提供三种芯片封装。预生产型 XC2KU050P FPGA 芯片将于 2026 年第四季度开始提供样品,预计将于 2027 年上半年量产。

设计人员可以使用基于可迁移的 XCSU200P 器件的 Spartan UltraScale+ SCU200 评估套件,提前体验 PCIe Gen4、硬内存控制器和高级安全功能,从而在第四季度为 Kintex UltraScale+ Gen 2 FPGA 提供迁移路径。

Kintex Ultrascale+ Gen 2 FPGA 系列在 Kintex FinFET 架构的基础上,优化了尺寸、功耗和性能规格,以满足视频、图像处理和高性能边缘智能应用的需求。该系列 FPGA 重新设计并简化了存储器层次结构,同时保持了与 AMD FPGA 产品组合的兼容性。

路线图和可用性

AMD采取分阶段推出的方式,使开发人员能够立即开始设计工作:

-

2026 年第三季度:通过 Vivado™ 和 Vitis™ 工具提供仿真支持。

-

2026 年第四季度:XC2KU050P 型号的硅样品开始发放,同时发布专用评估套件。

-

预计2027年上半年全面投产。

AMD支持长生命周期FPGA设计,直至2040年、2045年及以后。

(所有温度和速度等级,不包括 HBM 器件)

2026年2月3日,AMD宣布,将所有 AMD 7 系列设备的生命周期延长至 2040 年,并将 UltraScale+ 设备的生命周期至少延长至 2045 年。

尽管AMD计划新器件系列至少拥有15年的生命周期,但AMD 7系列和UltraScale+ FPGA以及自适应SoC仍能为新设计提供卓越的价值和功能。对于需要高性能和高集成度的设计,AMD Versal自适应SoC的供应周期将更长,直至2045年及以后。

通过此次生命周期延长,部分AMD设备将从发布之日起持续供应长达28年。这时间相当长。在某些情况下,甚至足以让下一代设计师继承其重新设计的设计理念。

这意味着什么?到 2040 年及以后,共有 19 个产品系列和超过 150 种独特的设备正在生产中,现在正是打造经久耐用产品的最佳时机。

参考来源

https://www.amd.com/en/blogs/2024/amd-supports-new-long-lifecycle-fpga-designs-thro.html

https://www.techporn.ph/amd-unveils-kintex-ultrascale-gen-2-fpga/

https://www.embedded.com/amd-upgrades-the-kintex-ultrascale-fpgas

结语

在当下智能化、数字化转型加速的背景下,FPGA 作为灵活可重构的核心计算载体,正成为各行业技术创新的重要支撑。AMD 此次在中端 FPGA 产品的升级与全系列长生命周期的布局,既为广播 AV、工业自动化等细分领域提供了更具性价比的实时计算解决方案,也以长期稳定的供应为行业技术创新筑牢了硬件根基。这一系列动作,不仅彰显了 AMD 在 FPGA 领域的技术积淀与市场洞察力,更让其在竞争激烈的自适应计算市场中,以 "技术领先 + 长期陪伴" 的姿态,为客户创造持续价值,也为整个 FPGA 行业的发展树立了兼顾创新与可持续性的标杆。未来,随着 Kintex UltraScale+ Gen 2 FPGA 的量产落地与长生命周期产品的持续供应,AMD 必将在嵌入式、工业、广播等更多领域,与客户携手推动技术创新的落地,让灵活、可靠的自适应计算能力,成为各行业数字化升级的核心动力。