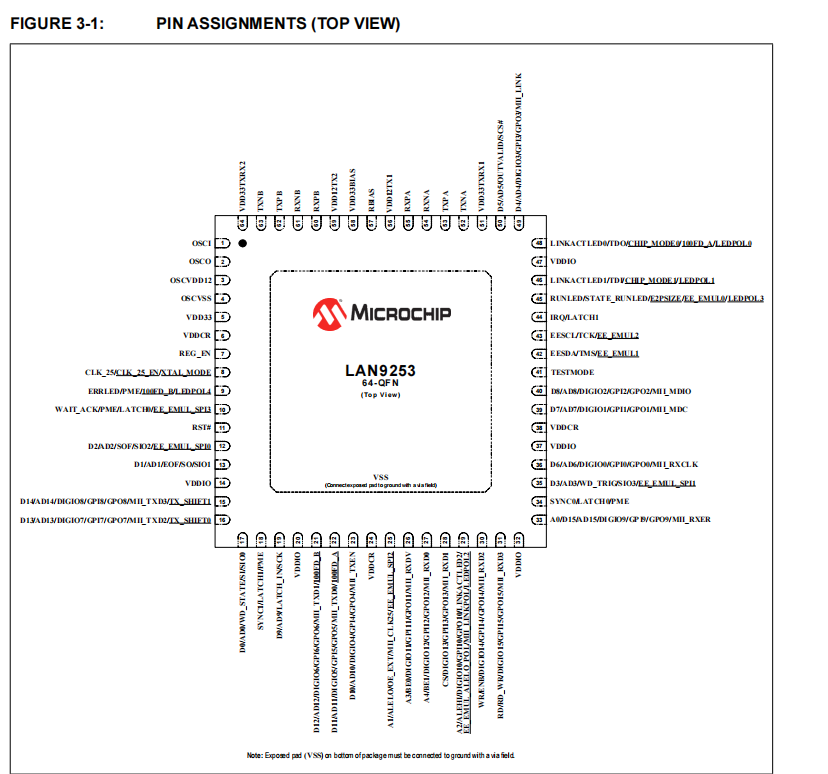

引脚描述与配置

3.1 引脚分配

3.1.1 引脚分配图

3.2.1 LAN 端口 A 引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 端口 A 双绞线发送 / 接收正通道 1 | TXPA | AIO | 端口 A 双绞线发送 / 接收正通道 1(见注 3-1) |

| 1 | 端口 A 双绞线发送 / 接收负通道 1 | TXNA | AIO | 端口 A 双绞线发送 / 接收负通道 1(见注 3-1) |

| 1 | 端口 A 双绞线发送 / 接收正通道 2 | RXPA | AIO | 端口 A 双绞线发送 / 接收正通道 2(见注 3-1) |

| 1 | 端口 A 双绞线发送 / 接收负通道 2 | RXNA | AIO | 端口 A 双绞线发送 / 接收负通道 2(见注 3-1) |

注 3-1:通道 1 或通道 2 可作为发送对,另一通道作为接收对;双绞线引脚的名称符号适用于正常连接;若启用自动交叉侦测(AutoMDIX)且检测到反向连接或手动选择反向连接,RX 和 TX 引脚将在内部交换;端口 A 连接 EtherCAT 端口 0 或 2。

3.2.2 LAN 端口 B 引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 端口 B 双绞线发送 / 接收正通道 1 | TXPB | AIO | 端口 B 双绞线发送 / 接收正通道 1(见注 3-2) |

| 1 | 端口 B 双绞线发送 / 接收负通道 1 | TXNB | AIO | 端口 B 双绞线发送 / 接收负通道 1(见注 3-2) |

| 1 | 端口 B 双绞线发送 / 接收正通道 2 | RXPB | AIO | 端口 B 双绞线发送 / 接收正通道 2(见注 3-2) |

| 1 | 端口 B 双绞线发送 / 接收负通道 2 | RXNB | AIO | 端口 B 双绞线发送 / 接收负通道 2(见注 3-2) |

注 3-2:通道 1 或通道 2 可作为发送对,另一通道作为接收对;双绞线引脚的名称符号适用于正常连接;若启用自动交叉侦测(AutoMDIX)且检测到反向连接或手动选择反向连接,RX 和 TX 引脚将在内部交换;端口 B 连接 EtherCAT 端口 1。

3.2.3 LAN 端口 A&B 电源与公共引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 偏置参考 | RBIAS | AI | 用于内部偏置电路;需外接 12.1kΩ、1% 精度电阻到地(见参考电路图);标称电压 1.2V,电阻功耗约 1mW |

| 1 | 模拟电源(端口 A 3.3V) | VDD33TXRX1 | P | 端口 A 模拟电源(见注 3-3) |

| 1 | 模拟电源(端口 B 3.3V) | VDD33TXRX2 | P | 端口 B 模拟电源(见注 3-3) |

| 1 | 偏置电源(3.3V) | VDD33BIAS | P | 偏置电路 3.3V 电源(见注 3-3) |

| 1 | 发送器电源(端口 A 1.2V) | VDD12TX1 | P | 由 VDDCR 电源(外部供电或内部稳压器输出)供电;必须与 VDD12TX2 引脚短接以确保正常工作(见注 3-3) |

| 1 | 发送器电源(端口 B 1.2V) | VDD12TX2 | P | 由 VDDCR 电源(外部供电或内部稳压器输出)供电;必须与 VDD12TX1 引脚短接以确保正常工作(见注 3-3) |

注 3-3:详细连接信息参考 "电源连接" 章节、器件参考电路图和 LANCheck 原理图检查清单。

3.2.4 EtherCAT MII 端口 & 配置带引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 25MHz 时钟 | MII_CLK25 | VO12(注 3-4) | 自由运行的 25MHz 时钟,可用作 PHY 的时钟输入;建议串联终端电阻以优化 PCB 信号完整性 |

| 1 | EEPROM 仿真 SPI 配置带 2 | EE_EMUL_SPI2(注 3-5) | VIS(PD) | 与 EE_EMUL_SPI0、EE_EMUL_SPI1、EE_EMUL_SPI3 配合,配置 EEPROM 仿真模式下 Beckhoff SPI 接口的工作方式;配置 SCS# 极性(0:SCS# 低电平有效;1:SCS# 高电平有效) |

| 4 | MII 端口接收数据 | MII_RXD[3:0] | VIS(PD) | 来自外部 PHY 的接收数据引脚 |

| 1 | MII 端口接收数据有效 | MII_RXDV | VIS(PD) | 来自外部 PHY 的接收数据有效信号 |

| 1 | MII 端口接收错误 | MII_RXER | VIS(PD) | 来自外部 PHY 的接收错误信号 |

| 1 | MII 端口接收时钟 | MII_RXCLK | VIS(PD) | 来自外部 PHY 的接收时钟 |

| 4 | MII 端口发送数据 | MII_TXD[3:0] | VO8 | 发送到外部 PHY 的发送数据引脚 |

| 2 | MII 发送时序偏移配置带 | TX_SHIFT [1:0](注 3-5) | VIS(PU)(注 3-6) | 配置外部 MII 总线的发送时序;TX_SHIFT1 位于 MII_TXD3 引脚,TX_SHIFT0 位于 MII_TXD2 引脚;00:20ns;01:30ns;10:0ns;11:10ns |

| 1 | 100Mbps 全双工配置带 B | 100FD_B(注 3-5) | VIS(PD)(注 3-6) | 3 端口模式下(由 CHIP_MODE1 选择),配置硬件配置寄存器(HW_CFG)中 "PHY B 自动协商禁用" 和 "PHY B AutoMDIX 禁用" 字段的默认值,默认将 PHY 设置为固定 100Mbps 全双工模式;0:默认启用自动协商和 AutoMDIX;1:默认禁用自动协商和 AutoMDIX(固定 100Mbps 全双工);2 端口模式下,该配置带位于 ERRLED 引脚 |

| 1 | 100Mbps 全双工配置带 A | 100FD_A(注 3-5) | VIS(PD)(注 3-6) | 3 端口模式下(由 CHIP_MODE1 选择),配置硬件配置寄存器(HW_CFG)中 "PHY A 自动协商禁用" 和 "PHY A AutoMDIX 禁用" 字段的默认值,默认将 PHY 设置为固定 100Mbps 全双工模式;0:默认启用自动协商和 AutoMDIX;1:默认禁用自动协商和 AutoMDIX(固定 100Mbps 全双工);2 端口模式下,该配置带位于 LINKACTLED0 引脚 |

| 1 | MII 端口发送使能 | MII_TXEN | VO8 | 发送到外部 PHY 的发送使能信号 |

| 1 | MII 端口链路状态 | MII_LINK | VIS | PHY 提供的信号,指示已建立 100Mbps 全双工链路;极性可通过 MII_LINKPOL 配置带配置 |

| 1 | SMI 时钟 | MII_MDC | VO8 | 到外部 PHY 的串行管理时钟 |

| 1 | SMI 数据 | MII_MDIO | VIS/VO8 | 到外部 PHY 的串行管理接口数据输入 / 输出;必须外接上拉电阻,确保 MDIO 信号未驱动时为逻辑 1 |

注 3-4 :建议串联终端电阻以优化 PCB 信号完整性;注 3-5 :带下划线的符号名称为配置带,配置带值在上电复位、EtherCAT 复位或 RST# 解除断言时锁存,详见 3.3 节;注 3-6:根据外部 MAC/PHY 器件的输入电流负载,可能需要外接辅助上拉或下拉电阻。

3.2.5 主机总线引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 读 | RD | VIS | 主机总线读选通信号;默认低电平有效,极性可通过配置寄存器设置 |

| 1 | 读 / 写 | RD_WR | VIS | 主机总线方向控制信号;与 ENB 引脚配合指示读或写操作;默认 1 为读、0 为写(R/nW),极性可通过配置寄存器设置 |

| 1 | 写 | WR | VIS | 主机总线写选通信号;默认低电平有效,极性可通过配置寄存器设置 |

| 1 | 使能 | ENB | VIS | 主机总线数据使能选通信号;与 RD_WR 引脚配合指示操作的数据阶段;默认低电平有效,极性可通过配置寄存器设置 |

| 1 | 片选 | CS | VIS | 主机总线片选信号,指示当前传输选中该器件;默认低电平有效,极性可通过配置寄存器设置 |

| 2 | 字节使能 | BE1/BE0 | VIS(PD) | 16 位数据模式下,指示要读写的字节;8 位数据模式下未使用;仅在多路复用模式下可用;默认低电平有效,极性可通过配置寄存器设置;下拉电阻使未驱动状态为有效,确保未驱动这些信号的早期 PCB 设计可支持 16 位总线周期 |

| 5 | 地址 | A[4:0] | VIS | 索引地址模式下提供地址;16 位数据模式下 bit0 未使用;地址 bit0 与数据 bit15 共享 |

| 16 | 数据 | D[15:0] | VIS/VO8 | 非多路复用地址模式下的主机总线数据总线;8 位数据模式下 bit15-8 未使用,输入 / 输出驱动器禁用;地址 bit0 与数据 bit15 共享 |

| 16 | 地址和数据 | AD[15:0] | VIS/VO8 | 多路复用地址模式下的主机总线地址 / 数据总线;单相位多路复用地址模式下,bit15-8 提供地址高字节,bit7-0 提供地址低字节;双相位多路复用地址模式下,bit7-0 提供地址的两个字节;8 位数据双相位多路复用地址模式下,bit15-8 未使用,输入 / 输出驱动器禁用 |

| 1 | 地址锁存使能高 | ALEHI | VIS | 多路复用地址模式下指示地址阶段;双相位多路复用地址模式下用于加载地址高字节;默认低电平有效(上升沿锁存地址),极性可通过配置寄存器设置 |

| 1 | EEPROM 仿真 ALELO 极性配置带 0 | EE_EMUL_ALELO_POL(注 3-7) | VIS(PU) | EEPROM 仿真模式下,若默认 PDI 选择设为 HBI 多路复用 1 相位,该配置带用于在加载 EEPROM 配置数据前设置 HBI ALE 极性 |

| 1 | 地址锁存使能低 | ALELO | VIS | 多路复用地址模式下指示地址阶段;单相位多路复用地址模式下用于加载两个地址字节,双相位多路复用地址模式下用于加载地址低字节;默认低电平有效(上升沿锁存地址),极性可通过配置寄存器设置 |

| 1 | 等待 / 确认 | WAIT_ACK | VO8/VOD8 | 指示主机总线周期可结束;器件未选中时为三态;默认推挽输出,缓冲类型可通过配置寄存器设为开漏;推挽操作时默认低电平表示等待,极性可通过配置寄存器设置;两个 bit 均为低时该引脚禁用 |

注 3-7:带下划线的符号名称为配置带,配置带值在上电复位、EtherCAT 复位或 RST# 解除断言时锁存,详见 3.3 节。

3.2.6 SPI/SQI 引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | SPI/SQI 客户端片选 | SCS# | VIS(PU) | SPI/SQI 客户端片选输入;低电平时选中 SPI/SQI 客户端进行传输;高电平时 SPI/SQI 串行数据输出(多个)为三态;使用 Beckhoff SPI 接口时,该信号极性由内部寄存器控制 |

| 1 | SPI/SQI 客户端串行时钟 | SCK | VIS(PU) | SPI/SQI 客户端串行时钟输入 |

| 4 | SPI/SQI 客户端串行数据输入 / 输出 | SIO[3:0] | VIS/VO8(PU) | 多比特 I/O 的 SPI/SQI 客户端数据输入和输出 |

| 1 | SPI 客户端串行数据输入 | SI | VIS(PU) | SPI 客户端串行数据输入;与 SIO0 共享 |

| 1 | SPI 客户端串行数据输出 | SO | VO8(PU)(注 3-8) | SPI 客户端串行数据输出;与 SIO1 共享 |

| 1 | EEPROM 仿真 SPI 配置带 1 | EE_EMUL_SPI1(注 3-9) | VIS(PU) | 与 EE_EMUL_SPI0、EE_EMUL_SPI2、EE_EMUL_SPI3 配合,配置 EEPROM 仿真模式下 Beckhoff SPI 接口的工作方式;EE_EMUL_SPI [1:0] 配置 SPI 模式;EE_EMUL_SPI1 位于 SIO3 引脚;00:SPI 模式 0;01:SPI 模式 1;10:SPI 模式 2;11:SPI 模式 3 |

| 1 | EEPROM 仿真 SPI 配置带 0 | EE_EMUL_SPI0(注 3-9) | VIS(PU) | 与 EE_EMUL_SPI1、EE_EMUL_SPI2、EE_EMUL_SPI3 配合,配置 EEPROM 仿真模式下 Beckhoff SPI 接口的工作方式;EE_EMUL_SPI [1:0] 配置 SPI 模式(详见 EE_EMUL_SPI1 引脚描述);EE_EMUL_SPI0 位于 SIO2 引脚 |

| 1 | EEPROM 仿真 SPI 配置带 3 | EE_EMUL_SPI3(注 3-9) | VIS(PD) | 与 EE_EMUL_SPI0、EE_EMUL_SPI1、EE_EMUL_SPI2 配合,配置 EEPROM 仿真模式下 Beckhoff SPI 接口的工作方式;配置数据输出采样模式;0:正常数据输出采样(SPI_DO 和 SPI_DI 在同一 SPI_CLK 边沿采样);1:延迟数据输出采样(SPI_DO 和 SPI_DI 在不同 SPI_CLK 边沿采样) |

注 3-8 :该引脚虽为 SPI 指令的输出,但包含上拉电阻(实际为 SIO bit1);注 3-9:带下划线的符号名称为配置带,配置带值在上电复位、EtherCAT 复位或 RST# 解除断言时锁存,详见 3.3 节。

3.2.7 EtherCAT 分布式时钟引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 2 | 同步 | SYNC1/SYNC0 | VO8/VOD8/VOS8 | 分布式时钟同步(输出)信号;EEPROM 加载完成前未驱动(高阻抗) |

| 2(见注) | 锁存 | LATCH1/LATCH0 | VIS | 分布式时钟锁存(输入)信号;通常与 SYNC0/SYNC1 功能共享,启用 SYNC 功能时,部分器件配置中这些信号映射到备用引脚(详见 11.2.1 节 "SYNC/LATCH 引脚多路复用") |

3.2.8 EtherCAT 数字 I/O 和 GPIO 引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 16 | 通用输入 | GPI[15:0] | VIS | 通用输入引脚,直接映射到通用输入寄存器;不保证通用输入的一致性 |

| 16 | 通用输出 | GPO[15:0] | VO8/VOD8 | 通用输出引脚,反映通用输出寄存器的值(无看门狗保护);EEPROM 加载完成前未驱动(高阻抗) |

| 16 | 数字 I/O | DIGIO[15:0] | VIS/VO8 | 输入 / 输出或双向数据引脚;EEPROM 加载完成前未驱动(高阻抗) |

| 1 | 输出有效 | OUTVALID | VO8 | 指示输出有效,可捕获到外部寄存器;EEPROM 加载完成前未驱动(高阻抗) |

| 1 | 锁存输入 | LATCH_IN | VIS | 外部数据锁存信号;检测到 LATCH_IN 上升沿时采样输入数据 |

| 1 | 看门狗触发 | WD_TRIG | VO8 | 同步管理器看门狗触发输出;EEPROM 加载完成前未驱动(高阻抗) |

| 1 | 看门狗状态 | WD_STATE | VO8 | 同步管理器看门狗状态输出;0 表示看门狗超时;EEPROM 加载完成前未驱动(高阻抗) |

| 1 | 帧起始 | SOF | VO8 | 以太网 / EtherCAT 帧起始输出;EEPROM 加载完成前未驱动(高阻抗) |

| 1 | 帧结束 | EOF | VO8 | 以太网 / EtherCAT 帧结束输出;EEPROM 加载完成前未驱动(高阻抗) |

| 1 | 输出使能 | OE_EXT | VIS | 输出使能输入;低电平时清除输出数据 |

3.2.9 EEPROM 引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | EEPROM I2C 串行数据输入 / 输出 | EESDA | VIS/VOD8 | 访问外部 EEPROM 时,为 I2C 串行数据输入 / 开漏输出;必须始终通过外部电阻上拉 |

| 1 | EEPROM 仿真配置带 1 | EE_EMUL1(注 3-10) | VIS | 与 EE_EMUL2 配合配置 EEPROM 仿真硬带值;任一为低则启用仿真;与 EE_EMUL0、EE_EMUL2 配合配置 EEPROM 仿真模式下的默认 PDI 选择(详见 EE_EMUL2 引脚描述) |

| 1 | EEPROM I2C 串行时钟 | EESCL | VIS/VOD8 | 访问外部 EEPROM 时,为 I2C 时钟输入 / 开漏输出;若使用 EEPROM,必须始终通过外部电阻上拉 |

| 1 | EEPROM 仿真配置带 2 | EE_EMUL2(注 3-10) | VIS | 与 EE_EMUL1 配合配置 EEPROM 仿真硬带值;任一为低则启用仿真;与 EE_EMUL0、EE_EMUL1 配合配置 EEPROM 仿真模式下的默认 PDI 选择;EE_EMUL [2:0]:000=SPI;001=HBI 索引 16 位 EtherCAT 直接映射;010=HBI 多路复用 1 相位 16 位 EtherCAT 直接映射;011=HBI 多路复用 2 相位 16 位 EtherCAT 直接映射;100=SPI EtherCAT 直接映射;101=Beckhoff SPI 模式;110 = 不适用(EEPROM 启用);111 = 不适用(EEPROM 启用) |

注 3-10:带下划线的符号名称为配置带,配置带值在上电复位、EtherCAT 复位或 RST# 解除断言时锁存,详见 3.3 节。

3.2.10 LED & 配置带引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 错误 LED | ERRLED/LEDPOL4 | OD12/OS12 | 错误 LED 输出,由 ESC 或本地 MCU 控制;配置为开漏 / 开源输出;开漏 / 开源默认选择及引脚默认极性由复位时采样的配置带值决定;通过 ASIC 配置寄存器(0x0142:0x0143)的 bit14(ERR LED 使能)启用输出;低电平有效时,EEPROM 加载错误时强制启用该引脚 |

| 1 | 100Mbps 全双工配置带 B | 100FD_B(注 3-12) | IS(PD) | 2 端口模式下(由 CHIP_MODE1 选择),配置硬件配置寄存器(HW_CFG)中 "PHY B 自动协商禁用" 和 "PHY B AutoMDIX 禁用" 字段的默认值,默认将 PHY 设置为固定 100Mbps 全双工模式;0:默认启用自动协商和 AutoMDIX;1:默认禁用自动协商和 AutoMDIX(固定 100Mbps 全双工);3 端口模式下,该配置带移至 MII_TXD1 引脚;若使用外部上拉,应连接到 VDD33;若 ERRLED 用作 PME 输出(可能为线或共享信号),需谨慎考虑配置带值;主机软件可能需要通过硬件配置寄存器(HW_CFG)的 "PHY B AutoMDIX 禁用" 和 "PHY B 自动协商禁用" 位修正配置带结果,并重新配置 PHY B |

| 1 | 运行 LED | RUNLED/LEDPOL3 | VOD12/VOS12 | 运行 LED 输出,由 AL 状态寄存器控制;配置为开漏 / 开源输出;开漏 / 开源默认选择及引脚默认极性由复位时采样的配置带值决定 |

| 1 | 状态运行 LED | STATE_RUNLED/LEDPOL3 | VOD12/VOS12 | 状态运行 LED 输出,等于 RUN LED 与 ERR LED 的非组合;可用于控制双色 RUN/ERR LED 的 RUN 端;配置为开漏 / 开源输出;开漏 / 开源默认选择及引脚默认极性由复位时采样的配置带值决定;通过 ASIC 配置寄存器(0x0142:0x0143)的 bit6(STATE_RUN LED 使能)选择 RUN 或 STATE_RUN |

| 1 | EEPROM 大小配置带 | E2PSIZE/EE_EMUL0(注 3-12) | VIS(PU) | 配置 EEPROM 大小;0:选择 1K 位(128x8)至 16K 位(2Kx8);1:选择 32K 位(4Kx8)至 4M 位(512Kx8);与 EE_EMUL1、EE_EMUL2 配合配置 EEPROM 仿真模式下的默认 PDI 选择(详见 EE_EMUL2 引脚描述) |

| 1 | 端口 2 链路 / 活动 LED | LINKACTLED2/MII_LINKPOL/LEDPOL2(注 3-12) | VOD12/VOS12 | 端口 2 的链路 / 活动 LED 输出(灭 = 无链路;亮 = 有链路无活动;闪烁 = 有链路有活动);配置为开漏 / 开源输出;开漏 / 开源默认选择及引脚默认极性由复位时采样的配置带值决定;配置 MII_LINK 引脚的极性(0:MII_LINK 低电平表示已建立 100Mbps 全双工链路;1:MII_LINK 高电平表示已建立 100Mbps 全双工链路) |

| 1 | 端口 1 链路 / 活动 LED | LINKACTLED1/CHIP_MODE1/LEDPOL1(注 3-12) | VOD12/VOS12 | 端口 1 的链路 / 活动 LED 输出(灭 = 无链路;亮 = 有链路无活动;闪烁 = 有链路有活动);配置为开漏 / 开源输出;开漏 / 开源默认选择及引脚默认极性由复位时采样的配置带值决定;与 CHIP_MODE0 配合配置 EtherCAT 芯片模式(CHIP_MODE [1:0]:0X=2 端口模式(端口 0 和 1 连接内部 PHY A 和 B);10=3 端口下行模式(端口 0 和 1 连接内部 PHY A 和 B,端口 2 连接外部 MII 引脚);11=3 端口上行模式(端口 2 和 1 连接内部 PHY A 和 B,端口 0 连接外部 MII 引脚) |

| 1 | 端口 0 链路 / 活动 LED | LINKACTLED0/CHIP_MODE0/100FD_A/LEDPOL0(注 3-12) | VOD12/VOS12 | 端口 0 的链路 / 活动 LED 输出(灭 = 无链路;亮 = 有链路无活动;闪烁 = 有链路有活动);配置为开漏 / 开源输出;开漏 / 开源默认选择及引脚默认极性由复位时采样的配置带值决定;与 CHIP_MODE1 配合配置芯片模式硬带值(详见 CHIP_MODE1 描述);2 端口模式下,CHIP_MODE0 未使用;2 端口模式下(由 CHIP_MODE1 选择),配置硬件配置寄存器(HW_CFG)中 "PHY A 自动协商禁用" 和 "PHY A AutoMDIX 禁用" 字段的默认值,默认将 PHY 设置为固定 100Mbps 全双工模式(0:默认启用自动协商和 AutoMDIX;1:默认禁用自动协商和 AutoMDIX(固定 100Mbps 全双工));3 端口模式下,该配置带移至 MII_TXD0 引脚 |

注 3-11 :若 LED 用作下拉配置带,需外接辅助下拉电阻以确保有效低电平;注 3-12:带下划线的符号名称为配置带,配置带值在上电复位、EtherCAT 复位或 RST# 解除断言时锁存,详见 3.3 节。

3.2.11 杂项引脚

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 中断输出 | IRQ | VO8/VOD8 | 中断请求输出;信号极性、源和缓冲类型可通过配置寄存器编程 |

| 0(见注) | 电源管理事件输出 | PME | VO8/VOD8/O8/OD8(见注) | 正确编程后,检测到唤醒事件时断言;信号极性和缓冲类型可通过内部寄存器编程(详见 "电源管理" 章节);可选启用,可通过内部寄存器映射到多个其他引脚;映射到 ERRLED 引脚时,位于 VDD33 电压域,缓冲类型为 O8/OD8;映射到 ERRLED 引脚时,EEPROM 加载错误会强制启用 ERRLED 功能,可能产生虚假 PME 事件 |

| 1 | 系统复位输入 | RST# | VIS/VOD8(PU) | 输入时,低电平有效信号允许外部硬件复位器件;器件内置上电复位电路,无需外部硬件复位时可悬空;使用时需遵守 "工作特性" 章节中的复位时序要求;输出时,上电复位期间或响应主设备控制器或主机接口的 EtherCAT 复位命令序列时驱动为低电平 |

| 1 | 稳压器使能 | REG_EN | AI | 接 3.3V 时,启用内部 1.2V 稳压器 |

| 1 | 测试模式选择 | TESTMODE | VIS(PD) | 必须接 VSS 以确保正常工作 |

| 1 | 晶体输入 | OSCI | ICLK | 外部 25MHz 晶体输入;也可由单端时钟振荡器驱动(此时 OSCO 应悬空);时钟菊花链配置中,使用前级器件的 CLK_25 作为输入时钟源时,需通过 XTAL_MODE 配置带输入将该引脚设为施密特触发输入模式 |

| 1 | 晶体输出 | OSCO | OCLK | 外部 25MHz 晶体输出 |

| 1 | 晶体时钟输出 | CLK_25 | O8 | 25MHz 晶体输出 |

| 1 | 晶体时钟输出使能 & 输入模式配置带 | CLK_25_EN/XTAL_MODE(注 3-14) | AI(见注) | 多直流电平配置带,启用 CLK_25 输出并选择 OSCI 引脚的晶体振荡器放大器或施密特触发输入;低于 0.8V:禁用 CLK_25 输出,选择晶体振荡器放大器;1.5V:启用 CLK_25 输出,选择晶体振荡器放大器;高于 2.2V:启用 CLK_25 输出,选择施密特触发输入;配置带加载时悬空则偏置到 VDD33/2,无需外部分压;若用外部上拉设置为高于 2.2V,应连接到 VDD33;可通过外部下拉或接 VSS 设置为低于 0.8V |

| 1 | 晶体 1.2V 电源 | OSCVDD12 | P | 由片上稳压器供电(除非通过 REG_EN 引脚配置为稳压器关闭模式)(见注 3-13) |

| 1 | 晶体地 | OSCVSS | P | 晶体地 |

注 3-13 :详细连接信息参考 "电源连接" 章节、器件参考电路图和 LANCheck 原理图检查清单;注 3-14:带下划线的符号名称为配置带,配置带值在上电复位、EtherCAT 复位或 RST# 解除断言时锁存,详见 3.3 节。

3.2.12 JTAG 引脚

表格

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | JTAG 测试模式选择 | TMS | VIS | JTAG 测试模式选择 |

| 1 | JTAG 测试时钟 | TCK | VIS | JTAG 测试时钟 |

| 1 | JTAG 测试数据输入 | TDI | VIS | JTAG 测试数据输入 |

| 1 | JTAG 测试数据输出 | TDO | VO12 | JTAG 测试数据输出 |

3.2.13 内核与 I/O 电源和地引脚

表格

| 引脚数量 | 名称 | 符号 | 缓冲类型 | 描述 |

|---|---|---|---|---|

| 1 | 稳压器 3.3V 电源 | VDD33 | P | 内部稳压器的 3.3V 电源;即使禁用内部稳压器,也必须提供 3.3V(见注 3-15) |

| 5 | 可变 I/O 电源(1.8V-3.3V) | VDDIO | P | 1.8V 至 3.3V 可变 I/O 电源(见注 3-15) |

| 3 | 数字内核 1.2V 电源 | VDDCR | P | 由片上稳压器供电(除非通过 REG_EN 引脚配置为稳压器关闭模式);引脚 6(稳压器输出引脚)需并联 1μF 和 470pF 去耦电容到地(见注 3-15) |

| 1 | 地 | VSS | P | 公共地;裸露焊盘必须通过过孔阵列连接到地平面;晶体振荡器有独立地引脚 OSCVSS(见注 3-15) |

注 3-15:详细连接信息参考 "电源连接" 章节、器件参考电路图和 LANCheck 原理图检查清单。

3.3 配置带

配置带可将器件的各种功能自动配置为用户定义值,在上电复位(POR)、EtherCAT 复位或引脚复位(RST#) 时锁存;配置带以带下划线的符号名称标识,定义见 3.2 节 "引脚描述"。

配置带内置电阻以防止信号悬空;若特定配置带连接到负载,应外接上拉或下拉电阻以增强内部电阻,确保锁存前达到所需电压电平;内部电阻可通过外接电阻覆盖。

注:系统设计人员必须保证配置带引脚满足 "17.6.3 复位和配置带时序" 中规定的时序要求;若锁存前配置带引脚未处于正确电压电平,器件可能捕获错误的配置带值。