文章目录

-

- RAM

-

- [SRAM & DRAM](#SRAM & DRAM)

- [异步 SRAM& 同步 SRAM (SSRAM)](#异步 SRAM& 同步 SRAM (SSRAM))

- CY7C1041CV33

RAM

SRAM & DRAM

- 常见的RAM 断电后数据立即丢失,需要持续供电维持数据。

| 类型 | 全称 | 特点 | 应用 |

|---|---|---|---|

| SRAM | Static RAM(静态 RAM) | - 6 晶体管结构- 无需刷新- 速度快、功耗高、成本高 | CPU 缓存、FPGA 片外高速缓存 |

| DRAM | Dynamic RAM(动态 RAM) | - 1 晶体管 + 1 电容- 需定期刷新(~64ms)- 速度较慢、密度高、成本低 | 计算机主内存(DDR4/DDR5) |

- 此外,还有NVSRAM(Non-Volatile SRAM)、MRAM(Magnetoresistive RAM)、FRAM(Ferroelectric RAM)等用于汽车黑匣子、POS 机(需掉电保护关键状态)等环境的非易失性 RAM(Non-Volatile RAM, NVRAM)。

异步 SRAM& 同步 SRAM (SSRAM)

| 典型异步型号 | 容量 | 位宽 | 封装 | 应用场景 |

|---|---|---|---|---|

| CY7C1041CV33 | 512KB (256K × 16) | 16-bit | TSOPII-54 | 汽车电子、工业控制 |

| IS61LV25616AL | 512KB (256K × 16) | 16-bit | TSOP-44 | FPGA 开发板(如 DE2) |

| AS6C62256 | 32KB (32K × 8) | 8-bit | DIP/SOP | 嵌入式小系统 |

| 71V424 | 512KB (512K × 8) | 8-bit | TSOP | 网络设备缓存 |

- 异步 SRAM 的核心特点是:没有时钟输入引脚(CLK),所有操作由控制信号的电平变化直接触发。

| 类型 | 是否需时钟 | 刷新 | 访问延迟 | 控制复杂度 | 典型用途 |

|---|---|---|---|---|---|

| 异步 SRAM | 否 | 不需 | 极低(ns级) | 简单 | 高速缓存、状态机存储 |

| 同步 SRAM (SSRAM) | 是 | 不需 | 低(1~2 CLK) | 中等 | 高带宽嵌入式系统 |

| SDRAM | 是 | 需定期刷新 | 较高(含潜伏期) | 复杂 | 主存(PC、手机) |

- 异步 SRAM 的特性:

| 特性 | 说明 |

|---|---|

| 无需刷新 | 静态存储单元(6T 结构),只要通电数据就保持 |

| 无时钟依赖 | 所有操作由控制信号电平决定,响应快 |

| 确定性延迟 | 从地址稳定到数据有效的时间固定(如 t = 10 ns) |

| 高速访问 | 典型访问时间 8--15 ns,远快于 DRAM |

| 高功耗 & 高成本 | 单元面积大,不适合大容量主存 |

| 三态数据总线 | 支持多设备共享总线(高阻态隔离) |

CY7C1041CV33

- CY7C1041CV33 Automotive ------ 车规级高性能 CMOS 静态随机存取存储器(SRAM)芯片,CY7C1041CV33-10ZXI 4兆位( 256K ×16 )静态RAM。芯片适用于:

- 汽车电子控制单元(ECU)

- 仪表盘系统

- ADAS(高级驾驶辅助系统)

- 需要高可靠性、宽温范围和抗干扰能力的嵌入式系统

基本规格

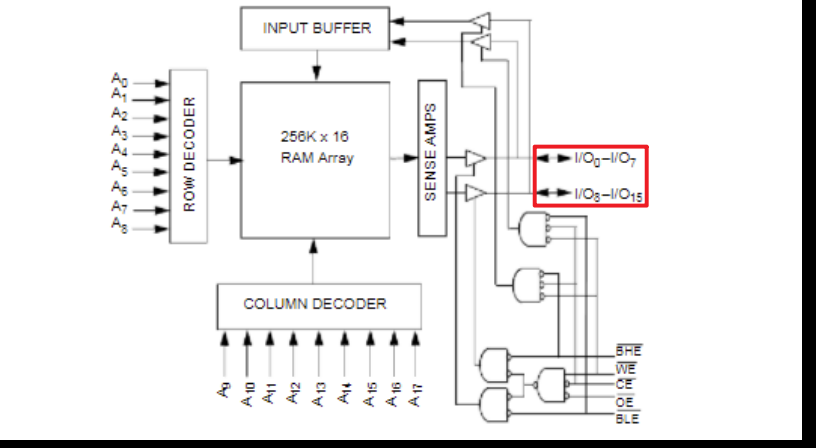

-

容量与结构 :

该 SRAM 的组织方式为 262,144 个字 × 16 位 ,即总容量为:

262,144 × 16 = 4,194,304 bits = 512 KB (字节) 262{,}144 \times 16 = 4{,}194{,}304\ \text{bits} = 512\ \text{KB (字节)} 262,144×16=4,194,304 bits=512 KB (字节)地址线为 A0--A17 ,共 18 根,可寻址 2 18 = 262,144 2^{18} = 262{,}144 218=262,144 个地址。

-

数据总线 :

16 位宽,分为低字节(I/O0--I/O7)和高字节(I/O8--I/O15)。

关键控制信号

- The CY7C1041CV33 Automotive is a high performance CMOSstatic RAM organized as 262,144 words by 16 bits. To write to the device, take Chip Enable (CE) and Write Enable(WE) inputs LOW. If Byte Low Enable (BLE) is LOW, then datafrom I/O pins (I/O0 through I/O7), is written into the locationspecified on the address pins (A0 through A17). If Byte HighEnable (BHE) is LOW, then data from I/O pins (I/O8 throughI/O15) is written into the location specified on the address pins(A0 through A17).To read from the device, take Chip Enable (CE) and OutputEnable (OE) LOW while forcing the Write Enable (WE) HIGH. IfByte Low Enable (BLE) is LOW, then data from the memorylocation specified by the address pins appear on I/O0 to I/O7. IfByte High Enable (BHE) is LOW, then data from memoryappears on I/O8 to I/O15. For more information, see the TruthTable on page 11 for a complete description of Read and Writemodes.The input and output pins (I/O0 through I/O15) are placed in ahigh impedance state when the device is deselected (CE HIGH),the outputs are disabled (OE HIGH), the BHE and BLE aredisabled (BHE, BLE HIGH), or during a write operation (CE LOWand WE LOW).

| 信号 | 功能 |

|---|---|

| CE | 芯片使能:LOW 表示选中芯片 |

| WE | 写使能:LOW 表示写操作 |

| OE | 输出使能:LOW 表示允许读出数据 |

| BLE | 低字节使能:LOW 表示操作 I/O0--I/O7 |

| BHE | 高字节使能:LOW 表示操作 I/O8--I/O15 |

- 一般可以将40(BHE)和39(BLE)直接接地。

写操作(Write)

-

可以只写低字节、只写高字节,或同时写两个字节(当 BLE 和 BHE 都为 LOW 时)。

-

要向芯片写入数据,需满足以下条件:

- CE(Chip Enable,片选) = LOW

- WE(Write Enable,写使能) = LOW

-

此时,根据两个字节使能信号决定写入哪一部分数据:

-

若 BLE(Byte Low Enable) = LOW :

将 I/O0--I/O7 上的数据写入由 A0--A17 指定的地址的 低字节。

-

若 BHE(Byte High Enable) = LOW :

将 I/O8--I/O15 上的数据写入同一地址的 高字节。

-

读操作(Read)

-

同样支持单独读低字节、高字节,或同时读取整个 16 位数据。

-

要从芯片读取数据,需满足:

- CE = LOW

- OE(Output Enable,输出使能) = LOW

- WE = HIGH(必须为高,防止误写)

-

此时:

- 若 BLE = LOW :

指定地址的 低字节数据 出现在 I/O0--I/O7。 - 若 BHE = LOW :

指定地址的 高字节数据 出现在 I/O8--I/O15。

- 若 BLE = LOW :

高阻态(High-Impedance / Tri-State)

- 高阻态对多设备共享总线非常重要,避免总线冲突。在以下任一情况下,所有 I/O 引脚(I/O0--I/O15)进入高阻态 (即断开输出,不驱动总线):

- CE = HIGH(芯片未被选中)

- OE = HIGH(输出被禁用)

- BLE = HIGH 且 BHE = HIGH(两个字节使能都无效)

- 正在进行写操作(CE = LOW 且 WE = LOW)------ 此时 I/O 作为输入,输出自然关闭

异步 SRAM 芯片

-

CY7C1041CV33 是一款 异步 SRAM 芯片 (Asynchronous Static RAM),本身 没有内部状态机或复杂协议,其读写完全由外部逻辑通过控制信号(CE、OE、WE、BLE、BHE)直接驱动。

-

示例:Verilog SRAM 控制器(支持字节/字写入、字读取)

这段Verilog代码实现了一个异步SRAM(CY7C1041CV33,512KB×16位)的控制器模块,核心作用是对接CPU/FIFO等上层逻辑与物理SRAM芯片:

- 接收上层的读写请求、地址、数据和字节选择信号;

- 按照SRAM的时序要求生成控制信号(片选、读使能、写使能、字节使能等);

- 处理双向数据总线的三态逻辑,完成数据读写,并通过应答信号告知上层操作完成。

verilog

// sram_controller.v

// 注:CY7C1041CV33是异步SRAM芯片,容量512KB字节(按16位宽算,共2^18=262144个存储单元); 前提假设:系统时钟频率足够高,能满足SRAM的时序要求(如地址访问时间tAA、写周期tWC)

// 模块定义,带参数化配置(方便适配不同规格SRAM)

module sram_controller #(

parameter ADDR_WIDTH = 18, // 地址位宽:2^18=262144个存储单元,对应512KB(512×1024)

parameter DATA_WIDTH = 16 // 数据位宽:16位(与SRAM的16位宽匹配)

)(

// 时钟与复位

input clk, // 系统时钟(控制器同步时钟)

input rst_n, // 低电平有效的异步复位

// CPU/FIFO上层接口(控制器的输入/输出)

input req, // 读写请求有效信号(高电平表示有请求)

input wr_en, // 写使能:1=写操作,0=读操作

input [ADDR_WIDTH-1:0] addr, // 读写地址

input [DATA_WIDTH-1:0] wdata, // 写数据(CPU/FIFO→SRAM)

output reg [DATA_WIDTH-1:0] rdata, // 读数据(SRAM→CPU/FIFO)

input byte_sel_low, // 低字节选择:1=操作低8位(I/O0-7)

input byte_sel_high, // 高字节选择:1=操作高8位(I/O8-15)

output reg ack, // 应答有效信号:高电平表示操作完成

// SRAM物理引脚接口(直接连接SRAM芯片)

output reg [ADDR_WIDTH-1:0] sram_addr, // SRAM地址线

inout [DATA_WIDTH-1:0] sram_dq, // SRAM双向数据总线(关键:inout类型)

output reg sram_ce_n, // SRAM片选(低有效)

output reg sram_oe_n, // SRAM读使能(低有效)

output reg sram_we_n, // SRAM写使能(低有效)

output reg sram_ble_n, // SRAM低字节使能(低有效,对应I/O0-7)

output reg sram_bhe_n // SRAM高字节使能(低有效,对应I/O8-15)

);

// Tri-state data bus:三态数据总线控制(核心!处理双向总线)

// 逻辑:只有写操作、片选有效、写使能有效时,才把wdata输出到sram_dq;否则总线置高阻(z)

assign sram_dq = (wr_en && !sram_ce_n && !sram_we_n) ? wdata : {DATA_WIDTH{1'bz}};

// Internal state (simple 2-cycle: setup + access):内部状态机定义(简单2周期:建立+访问)

reg [1:0] state; // 状态寄存器(2位足够表示3个状态)

// 状态常量定义(提高代码可读性)

localparam IDLE = 2'b00, // 空闲态:无请求,所有SRAM控制信号置无效

SETUP = 2'b01, // 建立态:锁存地址、字节选择,置位片选和读写使能

ACCESS = 2'b10; // 访问态:读操作锁存数据,置位应答,完成一次交易

// 时序逻辑:状态机核心(时钟上升沿/复位下降沿触发)

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin // 异步复位(低有效):所有信号置初始态

state <= IDLE; // 回到空闲态

ack <= 0; // 应答无效

sram_ce_n <= 1'b1; // 片选无效(高)

sram_oe_n <= 1'b1; // 读使能无效(高)

sram_we_n <= 1'b1; // 写使能无效(高)

sram_ble_n <= 1'b1; // 低字节使能无效(高)

sram_bhe_n <= 1'b1; // 高字节使能无效(高)

sram_addr <= 0; // 地址置0

end else begin // 非复位状态:状态机逻辑

ack <= 0; // 先默认应答无效(避免锁存,仅在ACCESS态置1)

case (state)

IDLE: begin // 空闲态:等待请求

// 空闲态下,所有SRAM控制信号置无效(防止误操作)

sram_ce_n <= 1'b1;

sram_oe_n <= 1'b1;

sram_we_n <= 1'b1;

sram_ble_n <= 1'b1;

sram_bhe_n <= 1'b1;

// 检测到有效请求(req=1),进入建立态

if (req) begin

sram_addr <= addr; // 锁存上层输入的地址

sram_ble_n <= ~byte_sel_low; // 字节使能:低有效,所以取反(sel=1→ble_n=0)

sram_bhe_n <= ~byte_sel_high;// 同理,高字节选择→bhe_n置低

state <= SETUP; // 进入建立态

end

end

SETUP: begin // 建立态:配置SRAM控制信号,为读写做准备

// Address and enables are already set:地址和字节使能已在IDLE→SETUP时锁存

// Assert CE and direction-specific enables:置位片选,并区分读写使能

sram_ce_n <= 1'b0; // 片选有效(低):选中SRAM芯片

if (wr_en) begin // 写操作

sram_we_n <= 1'b0; // 写使能有效(低)

sram_oe_n <= 1'b1; // 读使能无效(避免读写冲突)

end else begin // 读操作

sram_we_n <= 1'b1; // 写使能无效

sram_oe_n <= 1'b0; // 读使能有效(低)

end

state <= ACCESS; // 进入访问态

end

ACCESS: begin // 访问态:完成读写,置位应答

// Sample read data or hold write data:读操作锁存数据,写操作保持数据

if (~wr_en) begin // 仅读操作时

rdata <= sram_dq; // 锁存SRAM输出的读数据到rdata

end

ack <= 1'b1; // 应答有效:告知上层本次操作完成

state <= IDLE;// 回到空闲态,等待下一次请求

end

default: state <= IDLE; // 异常状态:回到空闲态(提高鲁棒性)

endcase

end

end

endmodule三态总线(sram_dq)

- SRAM的数据线是双向的(读时SRAM输出,写时控制器输出),Verilog中用

inout类型表示; - 控制器写SRAM时,把

wdata驱动到sram_dq;读SRAM时,sram_dq置高阻(z),由SRAM驱动数据; - 条件

(wr_en && !sram_ce_n && !sram_we_n)确保只有"写操作+片选有效+写使能有效"时才输出数据,避免总线冲突。

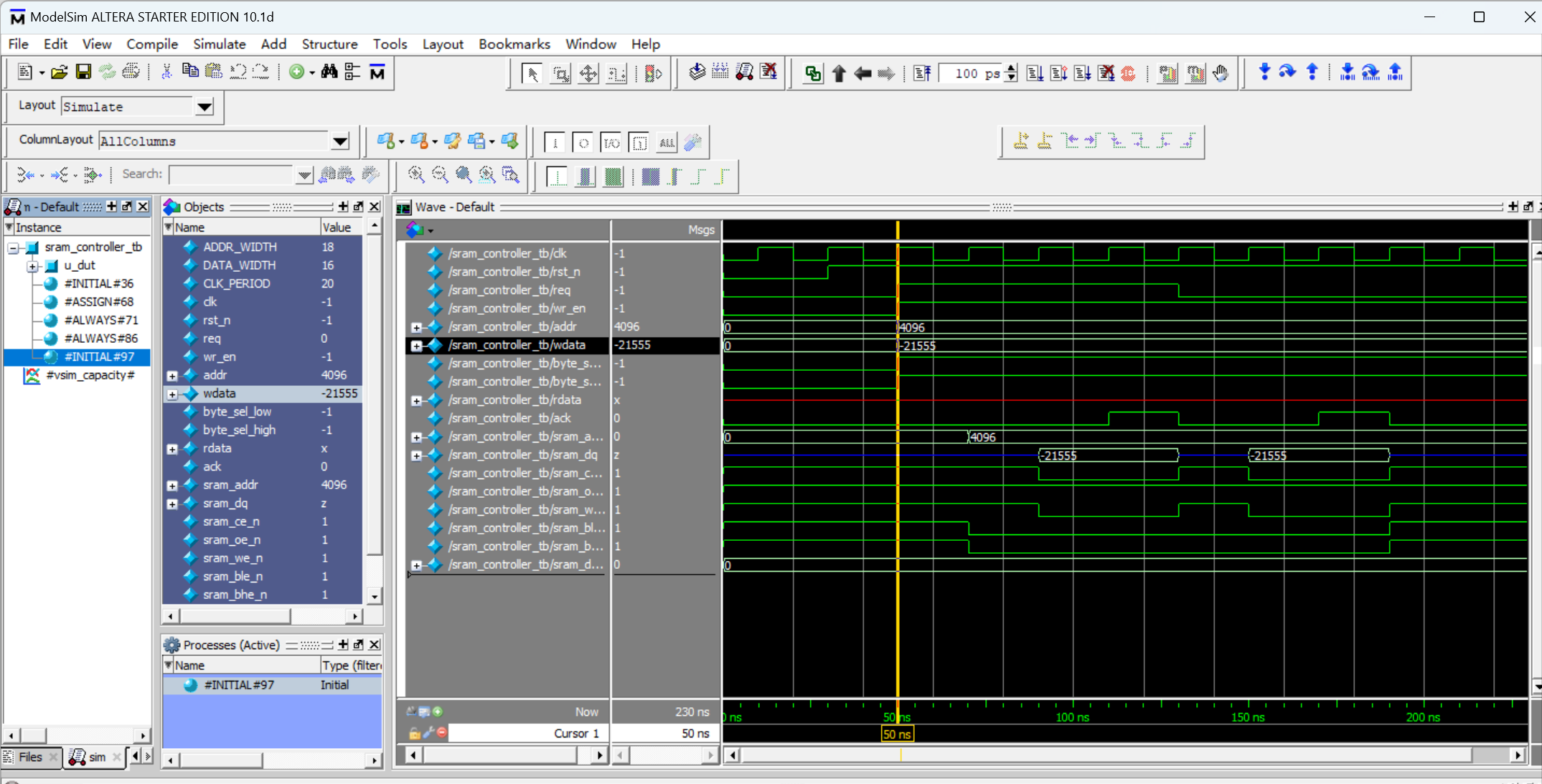

Testbench

- Testbench 包含以下关键部分:

- 时钟/复位生成:产生 50MHz 系统时钟(20ns 周期)和异步复位信号;

- SRAM 行为模型:模拟 CY7C1041CV33 异步 SRAM 的读写行为(存储数据、响应控制信号);

- 激励生成:向控制器发送写请求→读请求(验证写后读)、单字节读写、全字读写等测试用例;

- 结果检查:自动比对读回数据与写入数据,输出测试结果。

verilog

`timescale 1ns / 1ps

module sram_controller_tb;

// ====================== 1. 参数定义 ======================

parameter ADDR_WIDTH = 18;

parameter DATA_WIDTH = 16;

parameter CLK_PERIOD = 20; // 50 MHz

// ====================== 2. 信号声明 ======================

reg clk;

reg rst_n;

reg req;

reg wr_en;

reg [ADDR_WIDTH-1:0] addr;

reg [DATA_WIDTH-1:0] wdata;

reg byte_sel_low;

reg byte_sel_high;

wire [DATA_WIDTH-1:0] rdata;

wire ack;

wire [ADDR_WIDTH-1:0] sram_addr;

wire [DATA_WIDTH-1:0] sram_dq;

wire sram_ce_n;

wire sram_oe_n;

wire sram_we_n;

wire sram_ble_n;

wire sram_bhe_n;

// SRAM 行为模型存储

reg [7:0] sram_mem [0:(1<<ADDR_WIDTH)-1][1:0]; // [addr][0=low, 1=high]

reg [DATA_WIDTH-1:0] sram_dq_out;

// ====================== 3. 时钟生成 ======================

initial begin

clk = 1'b0;

forever #(CLK_PERIOD/2) clk = ~clk;

end

// ====================== 4. 实例化 DUT ======================

sram #(

.ADDR_WIDTH(ADDR_WIDTH),

.DATA_WIDTH(DATA_WIDTH)

) u_dut (

.clk(clk),

.rst_n(rst_n),

.req(req),

.wr_en(wr_en),

.addr(addr),

.wdata(wdata),

.byte_sel_low(byte_sel_low),

.byte_sel_high(byte_sel_high),

.ack(ack),

.rdata(rdata),

.sram_addr(sram_addr),

.sram_dq(sram_dq),

.sram_ce_n(sram_ce_n),

.sram_oe_n(sram_oe_n),

.sram_we_n(sram_we_n),

.sram_ble_n(sram_ble_n),

.sram_bhe_n(sram_bhe_n)

);

// ====================== 5. SRAM 行为模型 ======================

assign sram_dq = (!sram_ce_n && !sram_oe_n && sram_we_n) ? sram_dq_out : {DATA_WIDTH{1'bz}};

// 写操作:在 WE_n 下降沿锁存数据(按字节使能)

always @(negedge sram_we_n or negedge rst_n) begin

if (!rst_n) begin

// 初始化数据

// integer i, j;

// for (i = 0; i < (1 << ADDR_WIDTH); i = i + 1) begin

// sram_mem[i][0] = 8'h00;

// sram_mem[i][1] = 8'h00;

// end

end else if (!sram_ce_n) begin

if (!sram_ble_n) sram_mem[sram_addr][0] = sram_dq[7:0];

if (!sram_bhe_n) sram_mem[sram_addr][1] = sram_dq[15:8];

end

end

// 读操作:在 OE_n 下降沿输出数据

always @(negedge sram_oe_n or negedge rst_n) begin

if (!rst_n) begin

sram_dq_out <= {DATA_WIDTH{1'b0}};

end else if (!sram_ce_n) begin

sram_dq_out <= {16{1'b0}};

if (!sram_ble_n) sram_dq_out[7:0] <= sram_mem[sram_addr][0];

if (!sram_bhe_n) sram_dq_out[15:8] <= sram_mem[sram_addr][1];

end

end

// ====================== 6. 单次写入测试激励 ======================

initial begin

// 初始化

rst_n = 1'b0;

req = 1'b0;

wr_en = 1'b0;

addr = 0;

wdata = 0;

byte_sel_low = 1'b0;

byte_sel_high = 1'b0;

// 复位保持 2 个周期

repeat(2) @(posedge clk);

rst_n = 1'b1;

// === 单次写入:地址 0x1000,数据 0xABCD,全字节 ===

@(posedge clk);

req = 1'b1;

wr_en = 1'b1;

addr = 18'h1000;

wdata = 16'hABCD;

byte_sel_low = 1'b1; // 使能低字节

byte_sel_high = 1'b1; // 使能高字节

wait(ack == 1'b1); // 等待写完成

@(posedge clk);

req = 1'b0; // 撤销请求

// 仿真再跑几个周期以便观察波形

repeat(5) @(posedge clk);

$finish;

end

endmodule

-

用二维数组

sram_mem[地址][0/1]模拟 SRAM 存储阵列(0=低字节,1=高字节),支持按字节读写; -

双向总线

sram_dq处理:读操作时 SRAM 输出数据(sram_dq_out),写操作时 SRAM 接收数据并存储; -

响应

sram_we_n(写使能)和sram_oe_n(读使能)的低电平有效信号,模拟真实 SRAM 的读写时序。 -

输入接口:

req:发起一次访问wr_en:1=写,0=读addr:18 位地址(A0--A17)wdata:要写入的数据(16 位)byte_sel_low/high:控制是否操作低/高字节(类似 ARM 的strb)

-

输出:

ack:操作完成标志(单周期脉冲)rdata:读取的数据(仅在读操作有效)

-

SRAM 引脚:

- 所有

_n信号为低有效(符合芯片手册) sram_dq为双向三态总线

- 所有

电气建议

- 对于 CY7C1041CV33 这类纯异步 SRAM ,关键在于 满足最小脉冲宽度和地址建立/保持时间,通常需在 FPGA 中插入等待周期或使用 slower clock domain。

- 如果时钟较快(如 >50 MHz),建议在访问 SRAM 时插入 1~2 个等待周期 ,或使用 状态机延时 来满足 t(地址到数据有效时间,典型值 10--12 ns)。

verilog

// 新增延时计数器参数

parameter WAIT_CYCLES = 2; // 可配置等待周期,适配不同SRAM时序

reg [3:0] wait_cnt; // 延时计数器

// 在SETUP态后增加WAIT态,计数器减到0再进入ACCESS态

localparam IDLE=0, SETUP=1, WAIT=2, ACCESS=3;

always @(posedge clk) begin

if(state == WAIT) begin

wait_cnt <= wait_cnt - 1'b1;

if(wait_cnt == 0) state <= ACCESS;

end

end- 对于车规应用,请确保 FPGA I/O 电压与 SRAM 兼容(CY7C1041CV33 为 3.3V)

- 模拟实际系统中连接 FPGA、CPU 或总线时的寄生电容和阻抗:AC测试负载和波形图:提供了测试时使用的负载和波形,用于评估SRAM的性能

- 所有同步输入均通过由时钟的上升沿控制的输入寄存器。所有数据输出均通过由时钟的上升沿控制的输出寄存器。时钟输入由时钟使能(CEN)信号所控制;当该信号被取消激活时,它将暂停操作并延续前一个时钟周期。

读写测试

- 实例化

sram控制器,自动生成 一次写操作(地址 0,数据 0x1234) ,紧接着执行 一次读操作(地址 0) ,将读回的数据输出到顶层端口(便于仿真观察)。SRAM 是易失性、无内部状态机的存储器,只要能正确完成"写入 → 读出 → 数据比对"流程,基本可判定芯片功能完好。 - 一般将40(BHE)和39(BLE)直接接地。

verilog

// sramt.v

// Top-level module to perform: WRITE(addr=0, data=0x1234) → READ(addr=0)

// 模块 sramt 实现(先写后读地址 0) Uses the provided 'sram' controller

module sramt (

input clk,

input rst_n,

// Debug output: read-back data from address 0

output reg [15:0] final_rdata,

output reg done // High when both write and read are complete

);

parameter ADDR_WIDTH = 18;

parameter DATA_WIDTH = 16;

// Internal signals for sram controller interface

reg req;

reg wr_en;

reg [ADDR_WIDTH-1:0] addr;

reg [DATA_WIDTH-1:0] wdata;

reg byte_sel_low;

reg byte_sel_high;

wire [DATA_WIDTH-1:0] rdata;

wire ack;

// SRAM physical pins (not exposed at top level)

wire [ADDR_WIDTH-1:0] sram_addr;

wire [DATA_WIDTH-1:0] sram_dq;

wire sram_ce_n;

wire sram_oe_n;

wire sram_we_n;

wire sram_ble_n;

wire sram_bhe_n;

// State machine for test sequence

typedef enum logic [1:0] {

IDLE_ST,

WRITE_REQ,

WAIT_WRITE_ACK,

READ_REQ,

WAIT_READ_ACK,

FINISHED

} test_state_t;

test_state_t test_state;

// Instantiate the sram controller

sram #(

.ADDR_WIDTH(ADDR_WIDTH),

.DATA_WIDTH(DATA_WIDTH)

) u_sram (

.clk(clk),

.rst_n(rst_n),

.req(req),

.wr_en(wr_en),

.addr(addr),

.wdata(wdata),

.byte_sel_low(byte_sel_low),

.byte_sel_high(byte_sel_high),

.rdata(rdata),

.ack(ack),

.sram_addr(sram_addr),

.sram_dq(sram_dq),

.sram_ce_n(sram_ce_n),

.sram_oe_n(sram_oe_n),

.sram_we_n(sram_we_n),

.sram_ble_n(sram_ble_n),

.sram_bhe_n(sram_bhe_n)

);

// Test control logic

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

test_state <= IDLE_ST;

req <= 1'b0;

wr_en <= 1'b0;

addr <= 18'd0;

wdata <= 16'd0;

byte_sel_low <= 1'b0;

byte_sel_high <= 1'b0;

final_rdata <= 16'd0;

done <= 1'b0;

end else begin

req <= 1'b0; // default deassert request

case (test_state)

IDLE_ST: begin

if (rst_n) begin

test_state <= WRITE_REQ;

end

end

WRITE_REQ: begin

req <= 1'b1;

wr_en <= 1'b1;

addr <= 18'd0; // Address 0

wdata <= 16'h1234; // Write data

byte_sel_low <= 1'b1; // Enable low byte

byte_sel_high <= 1'b1; // Enable high byte

test_state <= WAIT_WRITE_ACK;

end

WAIT_WRITE_ACK: begin

if (ack) begin

test_state <= READ_REQ;

end

end

READ_REQ: begin

req <= 1'b1;

wr_en <= 1'b0; // Read operation

addr <= 18'd0; // Address 0

byte_sel_low <= 1'b1;

byte_sel_high <= 1'b1;

test_state <= WAIT_READ_ACK;

end

WAIT_READ_ACK: begin

if (ack) begin

final_rdata <= rdata; // Capture read data

done <= 1'b1;

test_state <= FINISHED;

end

end

FINISHED: begin

done <= 1'b1; // Hold done high

// Stay here forever

end

default: test_state <= IDLE_ST;

endcase

end

end

endmodule| 特性 | 说明 |

|---|---|

| 目标地址 | 固定为 0(18'd0) |

| 写入数据 | 16'h1234(可修改) |

| 字节使能 | 全字(低+高字节都使能) |

| 操作顺序 | 写 → 等待 ack → 读 → 等待 ack → 输出结果 |

| 输出信号 | final_rdata:读回的数据;done:操作完成标志 |

| 复位安全 | 异步复位,初始状态可控 |