摘自:ARM-中断状态,中断响应流程(四大步三小步)-CSDN博客

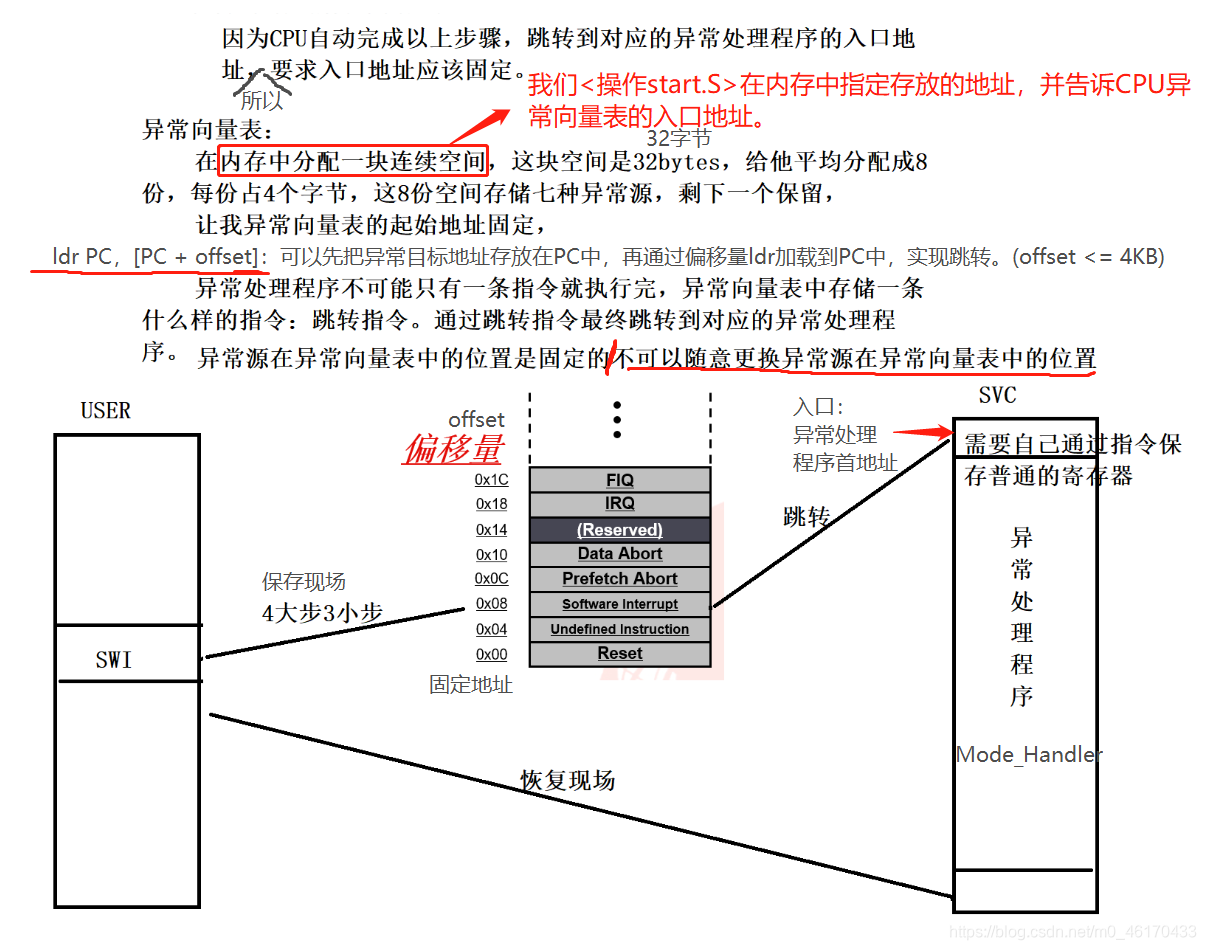

当异常发生时,ARM处理器核心会自动完成以下操作来保存现场:

-

保存CPSR :将当前程序状态寄存器 (

CPSR) 的内容复制到相应异常模式的备份寄存器 (SPSR_mode) 中。 -

设置CPSR:

-

切换处理器进入 ARM状态。

-

根据需要,禁止中断 (设置

FIQ或IRQ禁止位)。 -

根据异常类型,切换到对应的异常模式。

-

-

保存返回地址 :将当前程序计数器 (

PC) 的值保存到相应异常模式的链接寄存器 (lr_mode) 中。 -

跳转处理 :强制将

PC设置为异常向量表的固定首地址,开始执行中断服务程序。

-

软/硬中断区别 :硬中断 由硬件随机产生;软中断 (如

SWI指令)由软件预先安排,用于主动进入特权模式。 -

恢复现场 :上述由硬件完成,而中断返回时必须由软件手动恢复 现场,包括从

SPSR_mode恢复CPSR、从lr_mode恢复PC等。 -

Cortex-M vs Cortex-A :文章指出,Cortex-M系列 (如STM32)支持中断嵌套 ;而Cortex-A系列因处理速度快,硬件上不支持嵌套。

| 概念类别 | 核心内容/状态 | 简要说明 |

|---|---|---|

| 中断状态 | 1. 挂起态 | 中断已发生,但尚未被处理 |

| 2. 激活态 | 正在执行对应的中断处理函数 | |

| 3. 未激活态 | 无中断请求发生 | |

| 异常类型 (7种) | 1. 复位异常 | 优先级最高,用于系统启动 |

| 2. 数据异常 | 访问数据时出错(如地址无效) | |

| 3. 快速中断(FIQ) | 高速、低延迟中断 | |

| 4. 外部中断(IRQ) | 普通外设中断 | |

| 5. 预取异常 | 取指令时出错 | |

| 6. 软中断(SWI) | 软件主动触发,用于系统调用 | |

| 7. 未定义指令异常 | 指令译码失败 |