硬件上的差异

| 项目 | D-PHY | C-PHY |

|---|---|---|

| 时钟方式 | 有独立差分时钟 Lane | 时钟内嵌,无单独时钟线 |

| 每 Lane 线数 | 2 根(P/N) | 3 根(A/B/C) |

| 信号类型 | 差分信号 | 三相 / 三态信号 |

| 典型连线 | Clock + Data Lanes | 直接 Data Lanes |

| 模式 | 1/2/4 lane | 1/2/3 通道 |

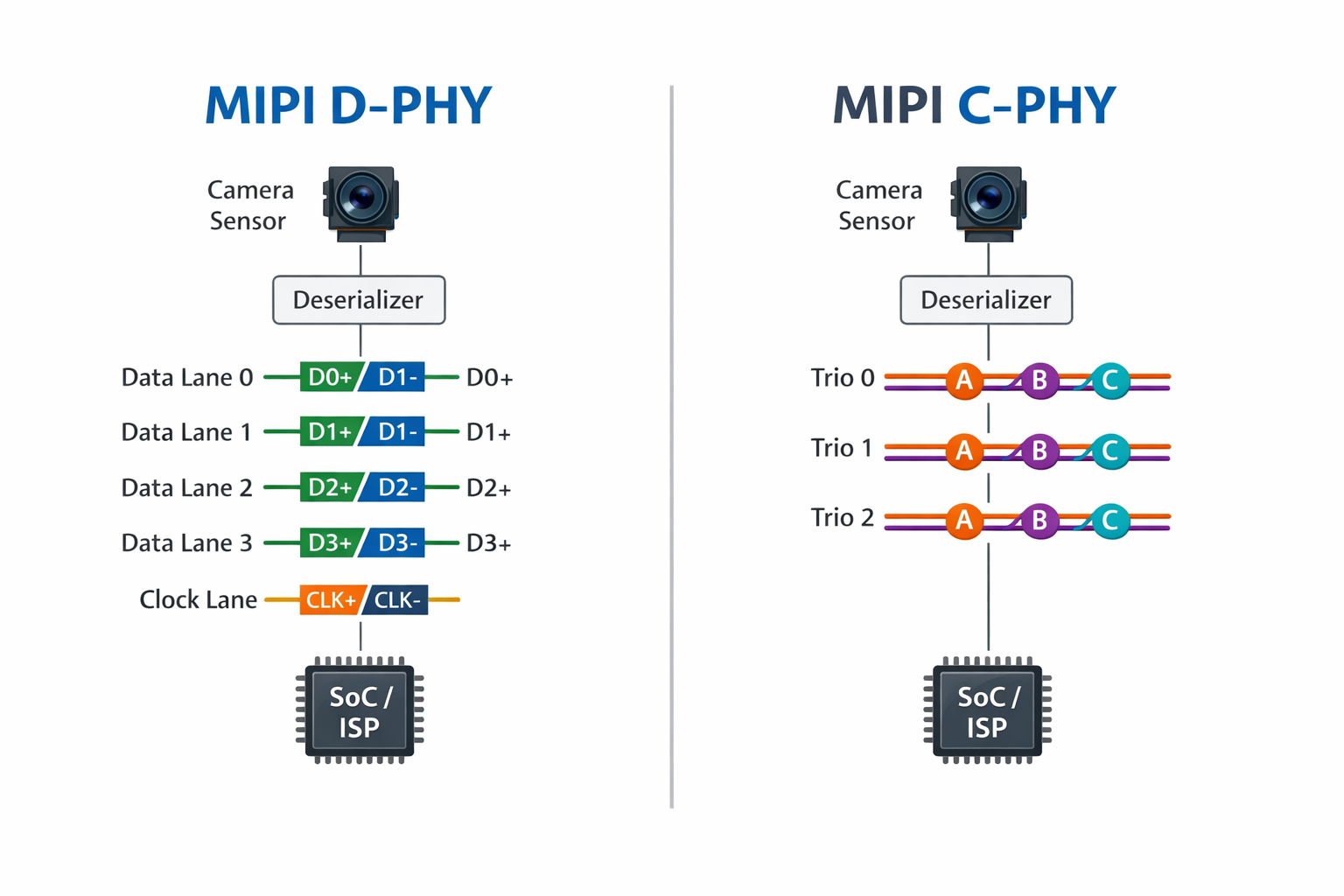

D-PHY 采用LVDS差分对结构,每条数据通道(lane)使用一对差分线,配合一对全局时钟差分线。数据 lane 数量可灵活配置,一般为 1、2 或 4 条,用于适配不同分辨率和帧率的摄像头或显示器;虽然理论上支持 3-lane,但在实际产品中极少使用,因为会增加设计复杂度且带宽没有整齐倍数优势。接收端设计成熟、兼容LVDS接口,但布线复杂度较高。

C-PHY 采用三线架构,每个通道由三条信号线组成,利用三电平(3-phase)编码在三条线上传输数据,每个符号可表示多比特信息。无需独立时钟线,时钟信息嵌入在符号编码中,接收端通过符号边沿恢复时钟,使布线更紧凑。接收端需实现三线多电平解码,对信号完整性要求较高。

性能/参数差异

| 对比项 | D-PHY | C-PHY |

|---|---|---|

| 每 Lane 线数 | 2 线(差分对:P/N) | 3 线(三相:A/B/C) |

| 单 Lane 速率 | 不同版本速率上限不同: v1.0:1.0 Gbps v1.1:1.5 Gbps v1.2:2.5 Gbps v2.0:4.5 Gbps v2.1:6.0 Gbps v3.0:9.0 Gbps(标准通道)/11 Gbps(短通道 | v1.0:2.5 Gsps ≈ 5.7 Gbps / trio v1.1:3.0 Gsps ≈ 6.8 Gbps / trio v1.2:3.5 Gsps ≈ 8.0 Gbps / trio v2.0:6.0 Gsps ≈ 13.7 Gbps / trio |

| 带宽效率 | 较低(需要额外时钟线) | 更高(三线编码,线更少、带宽密度更高) |

| 信号类型 | LVDS 差分信号 | 三相 / 三态编码(非差分) |

| 布线要求 | 对差分对匹配要求高 | 对三相线等长和耦合要求更严格 |

| 功耗 | 相对较高(时钟线持续工作) | 相对较低(无独立时钟,编码效率高) |

使用场景差异

D-PHY 更适合的场景

- 成熟、成本敏感的消费电子:如手机摄像头、显示屏、车载娱乐系统等,生态成熟、器件选择多。

- 对兼容性要求高的系统:需要对接大量现有 D-PHY 设备,不想做协议转换。

- 中低速、短距离传输:如 1080p/4K 摄像头、中等分辨率显示屏,带宽需求在 2~8 Gbps 范围。

C-PHY 更适合的场景

- 高分辨率、高帧率设备:如 8K 摄像头、VR/AR 头显、车载高清传感器,需要更高带宽密度。

- 空间 / 布线受限的设计:如轻薄笔记本、可穿戴设备、汽车内部线束,用更少线实现更高带宽。

- 对功耗敏感的移动 / 车载场景:如手机主摄、自动驾驶传感器,需要在有限功耗下提升传输能力。