时钟skew和时钟jitter的概念

clock skew(时钟偏移)

定义

时钟 skew 是指同一个时钟信号由于布线长度、负载差异或驱动能力不同,到达芯片上不同寄存器(触发器)的时间差异。

-

核心关键词: 空间差异、静态、确定性。

-

类比理解: 就像一场赛跑,发令枪响的同时,声音传到不同运动员耳朵里的时间有早有晚。

产生原因

-

布线长度: 时钟线从时钟源到寄存器A的距离比到寄存器B的距离长,导致到达时间不同。

-

负载不均衡: 如果某个时钟分支挂了太多的寄存器,容性负载大,会导致该路径的延时变大。

-

工艺、电压、温度(PVT)差异: 芯片不同区域的电压或温度不同,导致金属线或晶体管的传输延迟不同。

clock jitter(时钟抖动)

定义

clock jitter 是指时钟信号的边沿(上升沿或下降沿)在时间轴上发生短期、非理想性的偏移。即时钟周期在每一个瞬间并不完全相等。

-

核心关键词: 时间轴波动、动态、随机性。

-

类比理解: 运动员虽然同时听到了发令枪,但每个人的心跳节奏不稳定,导致起跑反应时间有微小的随机差异。

产生原因

-

电源噪声: 电源电压的波动会影响时钟发生器(PLL,即锁相环)或缓冲器的开关阈值,导致边沿提前或推迟。

-

热噪声: 晶体管内部的电子随机运动产生的噪声。

-

串扰: 相邻信号线的跳变通过耦合电容干扰时钟信号。

-

PLL 本身的局限性: 锁相环无法做到完美的频率合成,本身存在相位噪声。

正负时钟偏斜对建立时间和保持时间的影响

-

正 skew: 时钟到达第二个寄存器的时间比到达第一个寄存器的时间晚。如果控制得当,可以帮助满足建立时间,但可能会破坏保持时间。

-

负 skew: 时钟到达第二个寄存器的时间比到达第一个寄存器的时间早。这通常会使得时序收敛更加困难(对建立时间不友好,但对保持时间友好)。

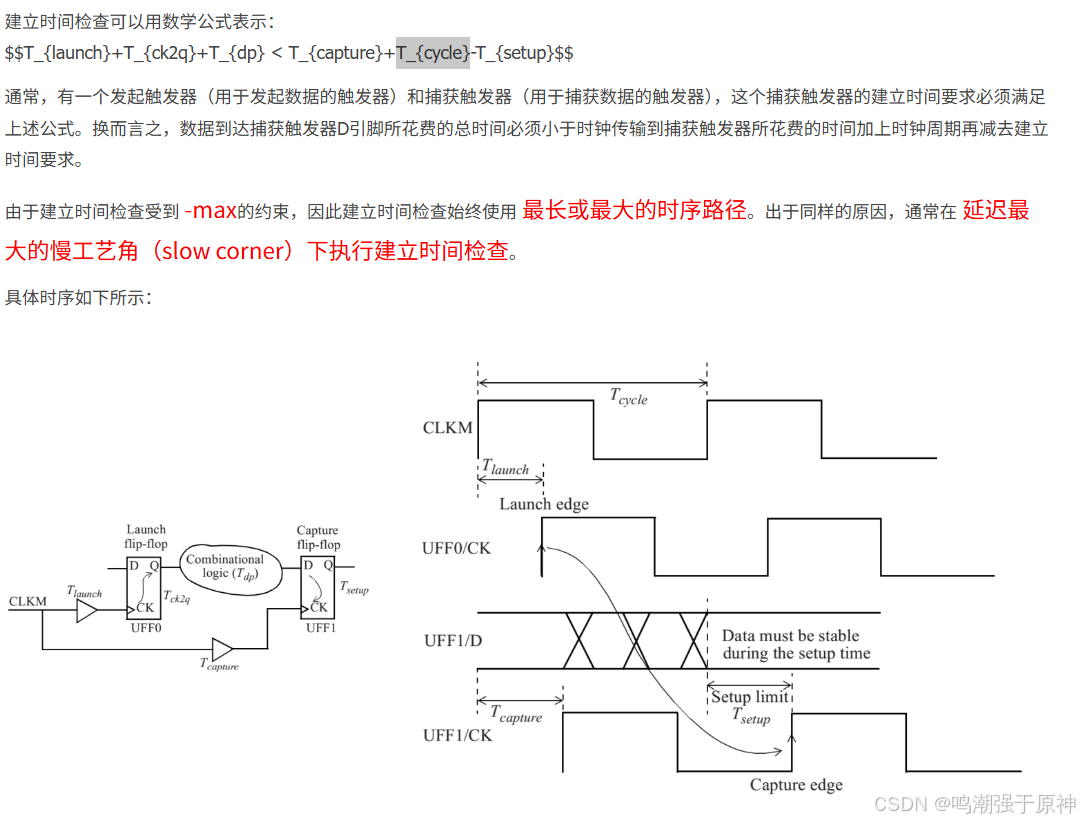

根据建立时间检查公式和保持时间检查公式

T_launch + T_ck2q + T_dp < T_capture + T_cycle - T_setup

即T_setup < T_capture + (T_cycle - T_launch - T_ck2q - T_dp)

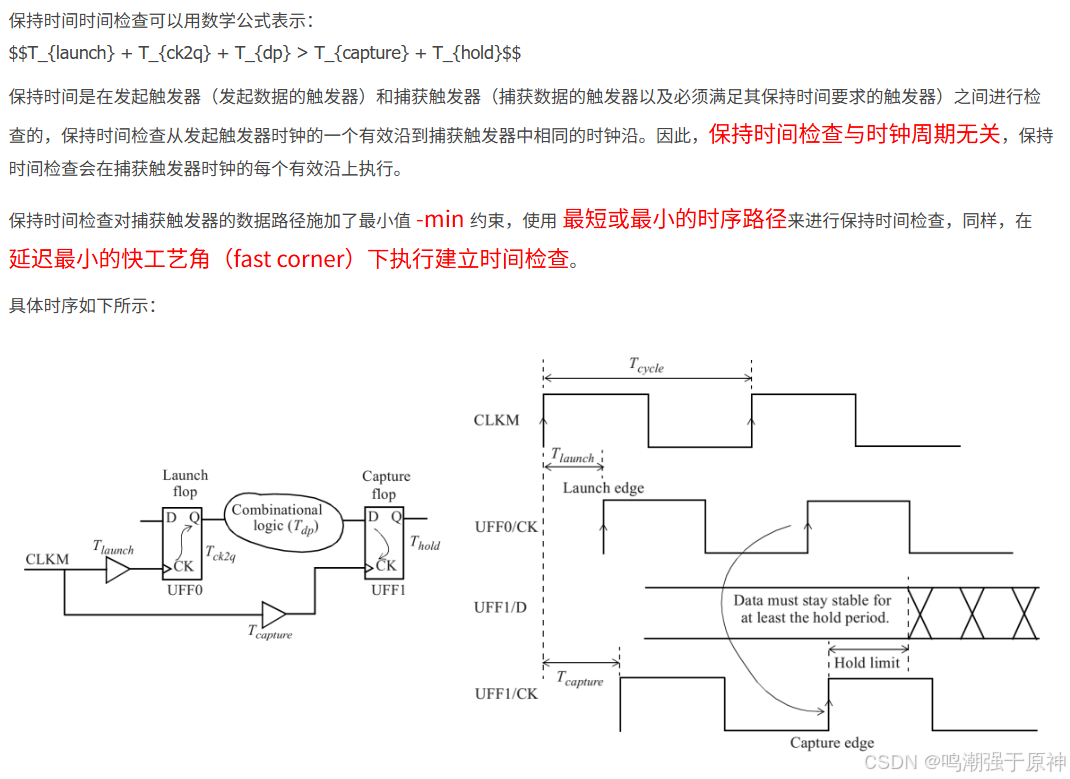

T_lanuch + T_ck2q + T_dp > T_capture +T_hold

即T_hold < (T_lanuch + T_ck2q + T_dp)- T_capture

括号包括的为不变量

根据控制变量法假设UFF0/CK的T_launch不变(包括其余变量),要想达到时钟正偏斜的效果,即增大UFF1/CK的T_capture,并且根据上述公式可以得出T_capture和建立时间成正比,和保持时间成反比,因此正偏斜对建立时间有利不利于保持时间,负偏斜则相反。

如果公式理解不了也可以借助上图将UFF1/CK的时钟沿往后推,即为正偏斜,往前即为负偏斜,观察图中的Setup limit和 Hold limit的变化。

引用文档: