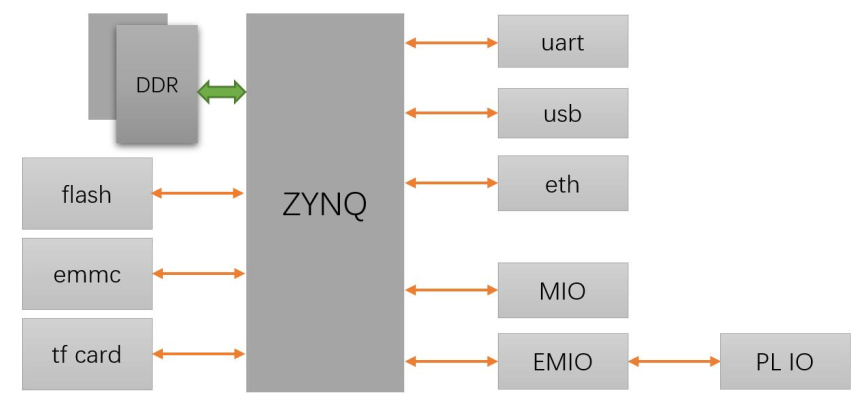

PSMIO一般会分配到固定的外设,包括FLASH、EMMC、TFCARD、UART、USB2.0、ETH以太网。PS的IO也可以单独配置成普通的GPIO,如果IO不够用也可以通过EMIO扩展更多IO,对于ZYNQ最多支持扩展64个EMIO。

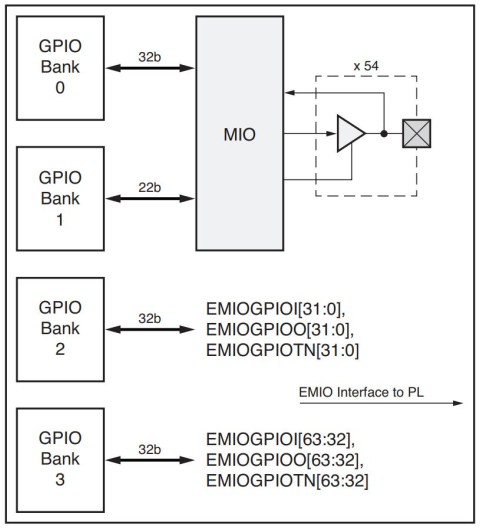

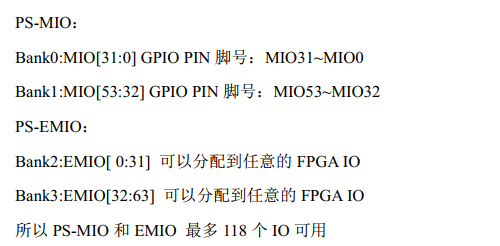

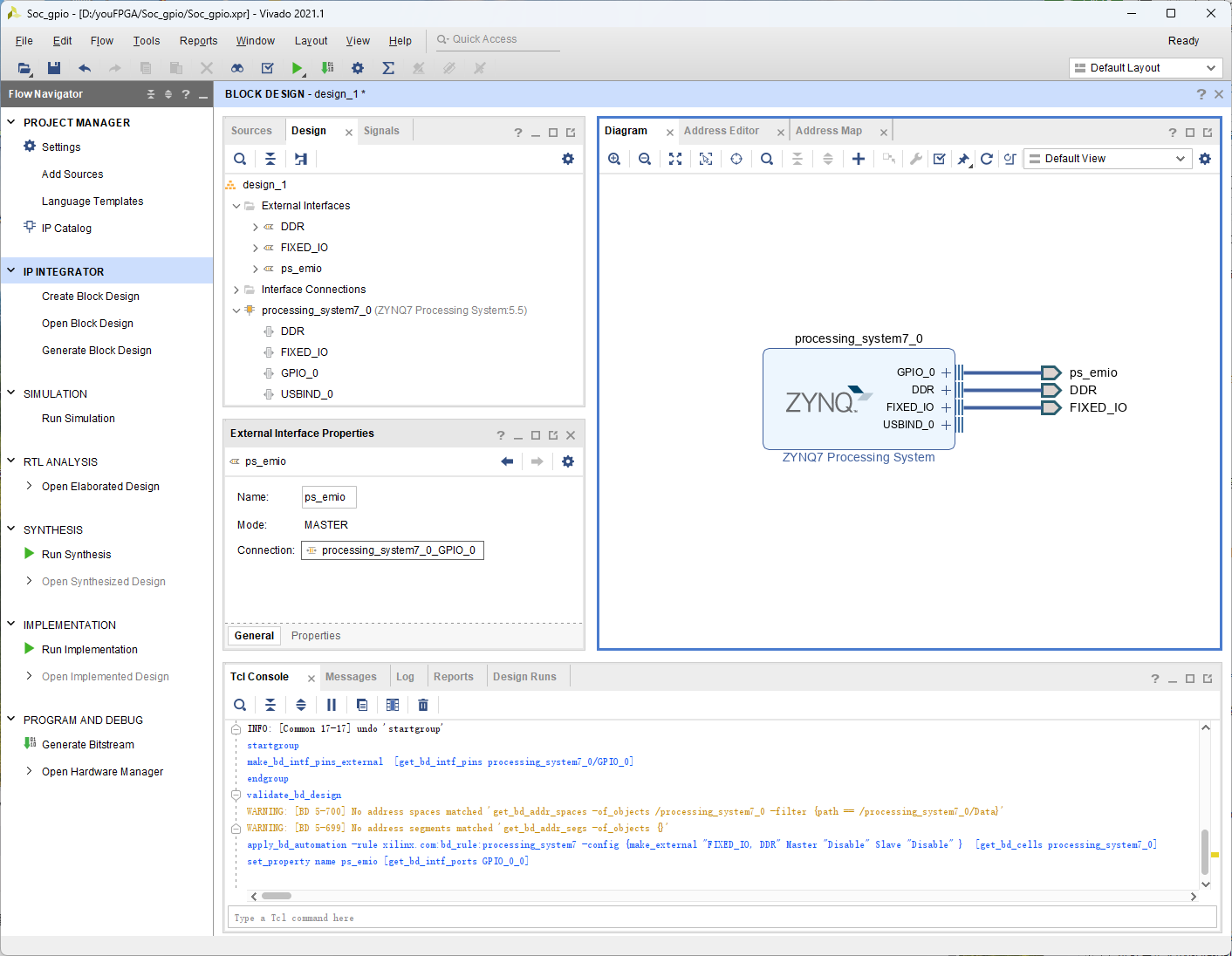

Zynq7000系列芯片中GPI0直接引到管脚的端口有54个,那么还有64个接口引入到了FPGA逻辑侧,这样这64个接口可以通过FPGA的IO进行输入输出了,所有接口都支持三态。结构框图如下

完整基础设置:

//Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

//--------------------------------------------------------------------------------

//Tool Version: Vivado v.2021.1 (win64) Build 3247384 Thu Jun 10 19:36:33 MDT 2021

//Date : Tue Mar 10 19:45:29 2026

//Host : LAPTOP-6SVODQGK running 64-bit major release (build 9200)

//Command : generate_target design_1_wrapper.bd

//Design : design_1_wrapper

//Purpose : IP block netlist

//--------------------------------------------------------------------------------

`timescale 1 ps / 1 ps

module design_1_wrapper

(DDR_addr,

DDR_ba,

DDR_cas_n,

DDR_ck_n,

DDR_ck_p,

DDR_cke,

DDR_cs_n,

DDR_dm,

DDR_dq,

DDR_dqs_n,

DDR_dqs_p,

DDR_odt,

DDR_ras_n,

DDR_reset_n,

DDR_we_n,

FIXED_IO_ddr_vrn,

FIXED_IO_ddr_vrp,

FIXED_IO_mio,

FIXED_IO_ps_clk,

FIXED_IO_ps_porb,

FIXED_IO_ps_srstb,

ps_emio_tri_io);

inout [14:0]DDR_addr;

inout [2:0]DDR_ba;

inout DDR_cas_n;

inout DDR_ck_n;

inout DDR_ck_p;

inout DDR_cke;

inout DDR_cs_n;

inout [3:0]DDR_dm;

inout [31:0]DDR_dq;

inout [3:0]DDR_dqs_n;

inout [3:0]DDR_dqs_p;

inout DDR_odt;

inout DDR_ras_n;

inout DDR_reset_n;

inout DDR_we_n;

inout FIXED_IO_ddr_vrn;

inout FIXED_IO_ddr_vrp;

inout [53:0]FIXED_IO_mio;

inout FIXED_IO_ps_clk;

inout FIXED_IO_ps_porb;

inout FIXED_IO_ps_srstb;

inout [5:0]ps_emio_tri_io;

wire [14:0]DDR_addr;

wire [2:0]DDR_ba;

wire DDR_cas_n;

wire DDR_ck_n;

wire DDR_ck_p;

wire DDR_cke;

wire DDR_cs_n;

wire [3:0]DDR_dm;

wire [31:0]DDR_dq;

wire [3:0]DDR_dqs_n;

wire [3:0]DDR_dqs_p;

wire DDR_odt;

wire DDR_ras_n;

wire DDR_reset_n;

wire DDR_we_n;

wire FIXED_IO_ddr_vrn;

wire FIXED_IO_ddr_vrp;

wire [53:0]FIXED_IO_mio;

wire FIXED_IO_ps_clk;

wire FIXED_IO_ps_porb;

wire FIXED_IO_ps_srstb;

wire [0:0]ps_emio_tri_i_0;

wire [1:1]ps_emio_tri_i_1;

wire [2:2]ps_emio_tri_i_2;

wire [3:3]ps_emio_tri_i_3;

wire [4:4]ps_emio_tri_i_4;

wire [5:5]ps_emio_tri_i_5;

wire [0:0]ps_emio_tri_io_0;

wire [1:1]ps_emio_tri_io_1;

wire [2:2]ps_emio_tri_io_2;

wire [3:3]ps_emio_tri_io_3;

wire [4:4]ps_emio_tri_io_4;

wire [5:5]ps_emio_tri_io_5;

wire [0:0]ps_emio_tri_o_0;

wire [1:1]ps_emio_tri_o_1;

wire [2:2]ps_emio_tri_o_2;

wire [3:3]ps_emio_tri_o_3;

wire [4:4]ps_emio_tri_o_4;

wire [5:5]ps_emio_tri_o_5;

wire [0:0]ps_emio_tri_t_0;

wire [1:1]ps_emio_tri_t_1;

wire [2:2]ps_emio_tri_t_2;

wire [3:3]ps_emio_tri_t_3;

wire [4:4]ps_emio_tri_t_4;

wire [5:5]ps_emio_tri_t_5;

design_1 design_1_i

(.DDR_addr(DDR_addr),

.DDR_ba(DDR_ba),

.DDR_cas_n(DDR_cas_n),

.DDR_ck_n(DDR_ck_n),

.DDR_ck_p(DDR_ck_p),

.DDR_cke(DDR_cke),

.DDR_cs_n(DDR_cs_n),

.DDR_dm(DDR_dm),

.DDR_dq(DDR_dq),

.DDR_dqs_n(DDR_dqs_n),

.DDR_dqs_p(DDR_dqs_p),

.DDR_odt(DDR_odt),

.DDR_ras_n(DDR_ras_n),

.DDR_reset_n(DDR_reset_n),

.DDR_we_n(DDR_we_n),

.FIXED_IO_ddr_vrn(FIXED_IO_ddr_vrn),

.FIXED_IO_ddr_vrp(FIXED_IO_ddr_vrp),

.FIXED_IO_mio(FIXED_IO_mio),

.FIXED_IO_ps_clk(FIXED_IO_ps_clk),

.FIXED_IO_ps_porb(FIXED_IO_ps_porb),

.FIXED_IO_ps_srstb(FIXED_IO_ps_srstb),

.ps_emio_tri_i({ps_emio_tri_i_5,ps_emio_tri_i_4,ps_emio_tri_i_3,ps_emio_tri_i_2,ps_emio_tri_i_1,ps_emio_tri_i_0}),

.ps_emio_tri_o({ps_emio_tri_o_5,ps_emio_tri_o_4,ps_emio_tri_o_3,ps_emio_tri_o_2,ps_emio_tri_o_1,ps_emio_tri_o_0}),

.ps_emio_tri_t({ps_emio_tri_t_5,ps_emio_tri_t_4,ps_emio_tri_t_3,ps_emio_tri_t_2,ps_emio_tri_t_1,ps_emio_tri_t_0}));

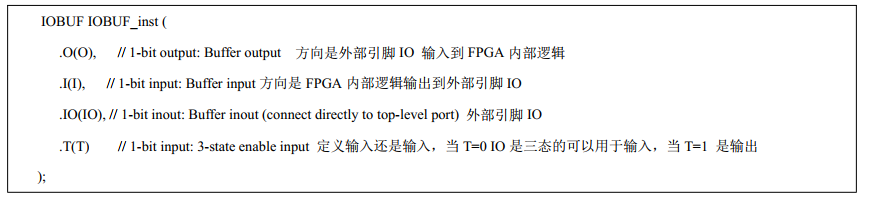

IOBUF ps_emio_tri_iobuf_0

(.I(ps_emio_tri_o_0),

.IO(ps_emio_tri_io[0]),

.O(ps_emio_tri_i_0),

.T(ps_emio_tri_t_0));

IOBUF ps_emio_tri_iobuf_1

(.I(ps_emio_tri_o_1),

.IO(ps_emio_tri_io[1]),

.O(ps_emio_tri_i_1),

.T(ps_emio_tri_t_1));

IOBUF ps_emio_tri_iobuf_2

(.I(ps_emio_tri_o_2),

.IO(ps_emio_tri_io[2]),

.O(ps_emio_tri_i_2),

.T(ps_emio_tri_t_2));

IOBUF ps_emio_tri_iobuf_3

(.I(ps_emio_tri_o_3),

.IO(ps_emio_tri_io[3]),

.O(ps_emio_tri_i_3),

.T(ps_emio_tri_t_3));

IOBUF ps_emio_tri_iobuf_4

(.I(ps_emio_tri_o_4),

.IO(ps_emio_tri_io[4]),

.O(ps_emio_tri_i_4),

.T(ps_emio_tri_t_4));

IOBUF ps_emio_tri_iobuf_5

(.I(ps_emio_tri_o_5),

.IO(ps_emio_tri_io[5]),

.O(ps_emio_tri_i_5),

.T(ps_emio_tri_t_5));

endmodule

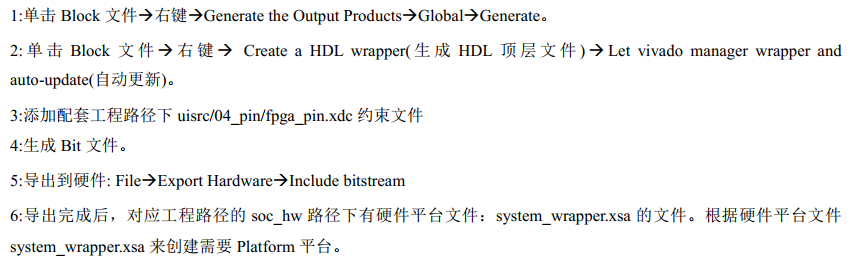

后续步骤: