目录

[1.1 什么是ARM](#1.1 什么是ARM)

[1.2 ARM与单片机(MCU)的区别](#1.2 ARM与单片机(MCU)的区别)

[1.3 ARM Cortex系列分类](#1.3 ARM Cortex系列分类)

[2.1 运算单元(ALU)](#2.1 运算单元(ALU))

[2.2 寄存器组](#2.2 寄存器组)

[通用寄存器 R0 ~ R12](#通用寄存器 R0 ~ R12)

[程序计数器 PC](#程序计数器 PC)

[链接寄存器 LR](#链接寄存器 LR)

[栈指针寄存器 SP](#栈指针寄存器 SP)

[当前程序状态寄存器 CPSR(重点)](#当前程序状态寄存器 CPSR(重点))

[保存程序状态寄存器 SPSR(重点:异常处理和中断)](#保存程序状态寄存器 SPSR(重点:异常处理和中断))

[2.3 流水线](#2.3 流水线)

[2.4 缓存(Cache)](#2.4 缓存(Cache))

[2.5 内存管理单元(MMU)](#2.5 内存管理单元(MMU))

[2.6 协处理器](#2.6 协处理器)

[3.1 寄存器](#3.1 寄存器)

[3.2 缓存(Cache)](#3.2 缓存(Cache))

[3.3 内存(RAM)](#3.3 内存(RAM))

[3.4 只读存储器(ROM)](#3.4 只读存储器(ROM))

[3.5 存储器访问效率对比](#3.5 存储器访问效率对比)

[4.1 总线类型](#4.1 总线类型)

[4.2 AMBA总线协议](#4.2 AMBA总线协议)

[4.3 常见外设控制器](#4.3 常见外设控制器)

[4.4 SOC概念](#4.4 SOC概念)

[5.1 冯诺伊曼结构与哈佛结构](#5.1 冯诺伊曼结构与哈佛结构)

[5.2 栈(Stack)详解](#5.2 栈(Stack)详解)

[7.1 多核异构](#7.1 多核异构)

[7.2 相关术语辨析](#7.2 相关术语辨析)

[8.1 二极管导通](#8.1 二极管导通)

[8.2 三极管导通](#8.2 三极管导通)

[8.3 MOS管导通](#8.3 MOS管导通)

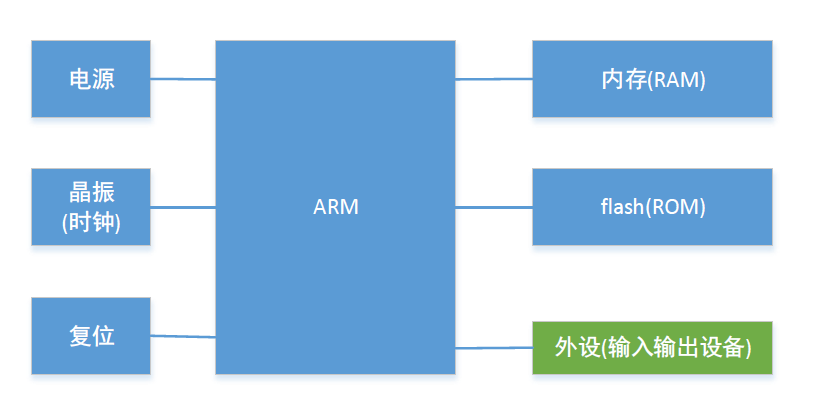

一、ARM处理器概述

1.1 什么是ARM

ARM(Advanced RISC Machines)是一种RISC(精简指令集计算机) 处理器架构,由ARM公司设计并授权给半导体厂商生产。其核心特点是指令集精简、执行效率高、功耗低。与之对应的是CISC(复杂指令集计算机),如x86架构,指令功能强大但硬件复杂。

1.2 ARM与单片机(MCU)的区别

-

单片机(MCU):通常将CPU、RAM、ROM、定时器、I/O等集成在一个芯片上,是一个完整的微型计算机系统。例如STM32系列基于Cortex-M内核。

-

ARM:既可以作为MCU的核心(如Cortex-M),也可以作为应用处理器(MPU)用于高性能设备(如Cortex-A)。ARM本身是处理器内核,需要搭配其他外设才能构成完整系统。

-

1.3 ARM Cortex系列分类

ARM根据应用场景将Cortex内核分为三个系列:

-

Cortex-A(Application):面向消费电子(手机、平板),低功耗

-

Cortex-R(Real-time):面向实时控制(汽车、工业),强调快速响应和可靠性。

-

Cortex-M(Microcontroller):面向微控制器(IoT、传感器),高能效

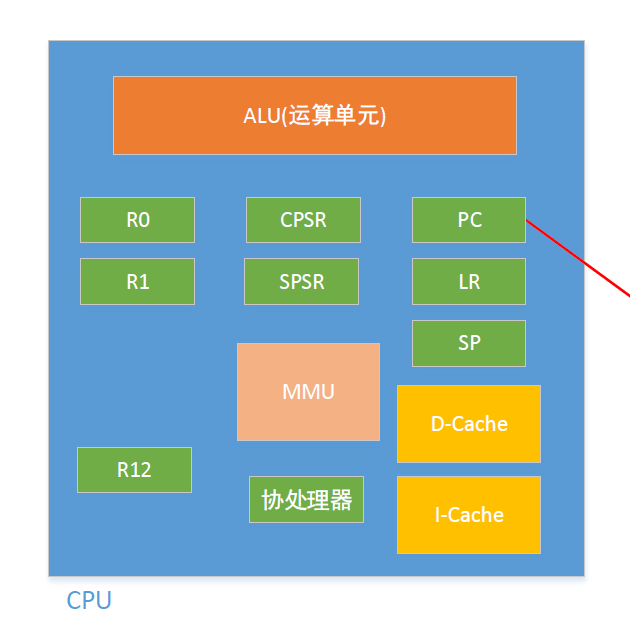

二、ARM处理器内部组成(核心部件)

ARM处理器内核主要由以下单元构成,它们协同工作完成指令执行和数据运算。

2.1 运算单元(ALU)

**ALU(运算单元)**是CPU执行算术运算(加、减、乘、除)和逻辑运算(与、或、非、异或)的硬件电路。它直接接收来自寄存器的数据,并将结果写回寄存器或内存。

2.2 寄存器组

寄存器是CPU内部最快的存储单元,用于临时存放指令、数据和地址。ARM处理器通常包含以下寄存器:

通用寄存器 R0 ~ R12

- 用于存储临时数据、变量或地址。R0~R12是32位寄存器(在ARMv7之前),其中R0~R7为低组寄存器,所有指令均可访问;R8~R12为高组寄存器,部分指令可能受限。

程序计数器 PC

-

PC(Program Counter) 一般指向正在运行的下下条指令,默认做自加运算,复位值为0

-

复位:CPU上电或复位时,PC被设置为复位向量地址(通常为0),并从该地址开始执行。

链接寄存器 LR

- **LR(Link Register)**存储函数的返回地址

栈指针寄存器 SP

- SP(Stack Pointer) 指向当前栈顶的地址。

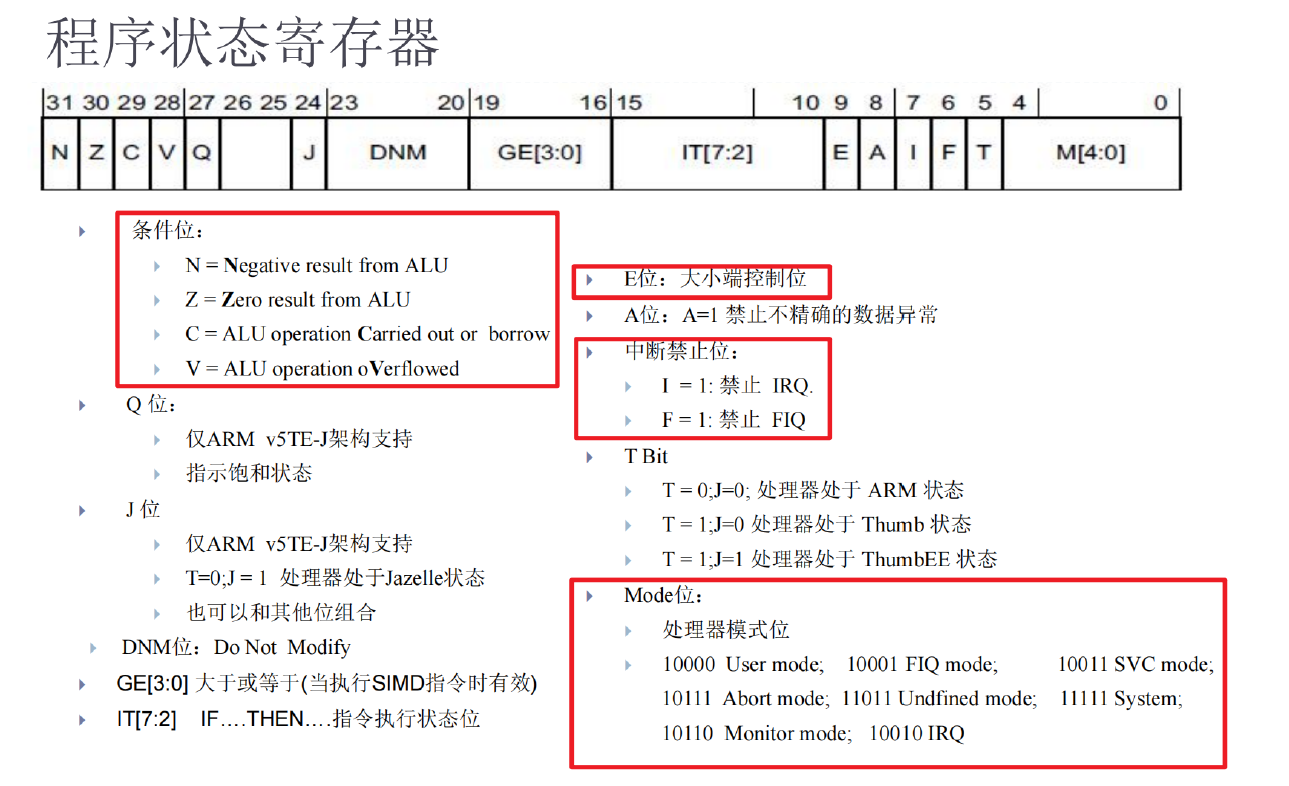

当前程序状态寄存器 CPSR(重点)

-

CPSR(Current Program Status Register)记录CPU的当前状态,包括:

-

条件标志位:N(负)、Z(零)、C(进位/借位)、V(溢出)

-

中断禁止位:I(IRQ禁止)、F(FIQ禁止)

-

处理器模式位(用户、系统、中断等)

-

大小端控制位(E)

-

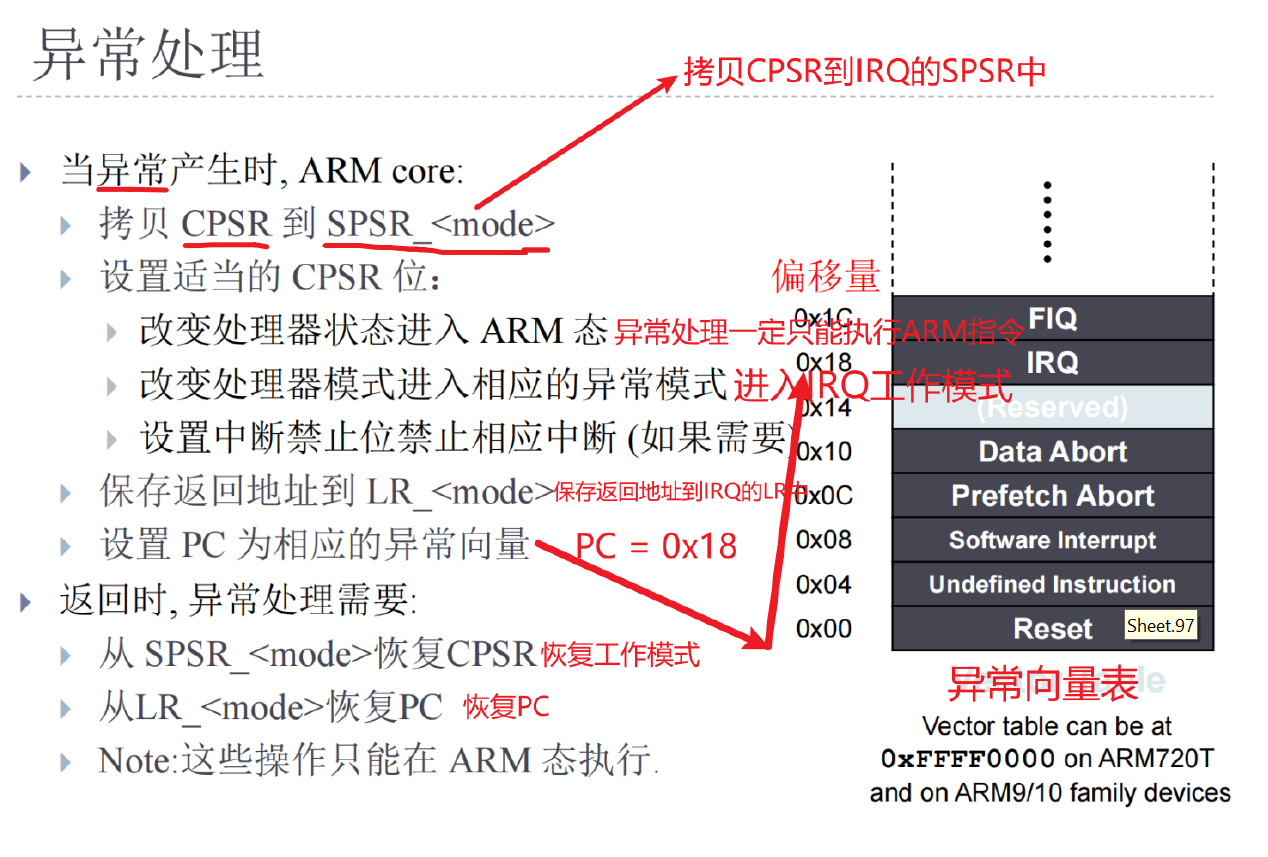

保存程序状态寄存器 SPSR(重点:异常处理和中断)

- **SPSR(Saved Program Status Register)保存程序状态寄存器,是CPSR的备份。**当发生异常(如中断)时,硬件自动将当前的CPSR保存到SPSR中,以便异常返回时恢复。每个异常模式都有自己的SPSR。

- 中断 :当外设触发中断,CPU保存当前上下文(自动保存PC到LR、CPSR到SPSR),跳转到中断向量表,执行中断服务程序,最后通过恢复现场返回。

2.3 流水线

现代ARM处理器采用指令流水线 技术(流水线提高了指令吞吐率),将指令执行过程分为多个阶段,使多条指令并行处理。典型的三级流水线包括:

-

取指(Fetch) :从内存中读取指令。

-

解码(Decode) :解析指令类型和操作数。

-

执行(Execute) :ALU运算或访存操作。

2.4 缓存(Cache)

Cache是缓存,访问速率介于寄存器和内存之间,提高程序执行的效率

-

I-Cache (指令缓存):缓存指令,减少取指延迟。

-

D-Cache (数据缓存):缓存数据,减少访存延迟。

-

访问速度:寄存器 > Cache > RAM > ROM/Flash。

2.5 内存管理单元(MMU)

MMU(Memory Management Unit) 负责将CPU生成的虚拟地址 转换为物理地址,并实现内存保护、页表管理、权限控制等功能。它是运行Linux等现代操作系统的必备组件。对于不带MMU的Cortex-M系列,则直接使用物理地址。

2.6 协处理器

ARM架构允许通过协处理器扩展功能,例如用于浮点运算的VFP(向量浮点单元)或NEON(SIMD指令集)。协处理器通过专用指令与CPU交互。

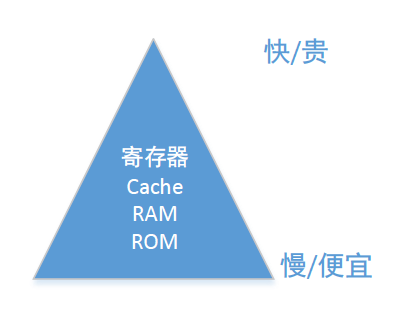

三、存储器层次结构

存储器系统遵循"速度越快、价格越贵、容量越小"的层次化设计。

3.1 寄存器

- 位于CPU内部,速度最快 (一个时钟周期),数量有限(通常十几个到几十个),用于临时存储。

3.2 缓存(Cache)

- 静态RAM(SRAM)实现,速度快但成本高。分为一级缓存(L1)和二级缓存(L2),部分处理器还有三级缓存(L3)。

3.3 内存(RAM)

RAM在运行时存放程序和数据,掉电后内容丢失。常见类型:

-

SRAM(静态RAM):用触发器存储,速度快但集成度低、功耗高,常用于Cache或片内RAM。

-

DRAM(动态RAM):用电容存储,需定期刷新,速度较慢但容量大、成本低,用作主存。

-

SDRAM(同步DRAM):与CPU时钟同步,提高数据传输效率。

-

DDR内存:双倍数据率SDRAM,在时钟上升沿和下降沿均传输数据(如DDR3、DDR4)。

3.4 只读存储器(ROM)

ROM掉电后数据不丢失,用于存储固件(如Bootloader)。常见类型:

-

PROM:可编程一次,出厂后无法修改。

-

EPROM:可擦除(紫外线照射)并重写,需专用编程器。

-

EEPROM:电可擦除,可字节级修改,常用于存储少量配置数据。

-

Flash(闪存) :**Flash访问速率快,掉电数据不丢失。**现代最常用的非易失存储器,分为NOR Flash(支持随机访问,可芯片内执行)和NAND Flash(高密度,用于存储设备)。

3.5 存储器访问效率对比

-

寄存器:最快/最贵

-

Cache:次之

-

RAM(SDRAM/DDR):中等速度/价格适中

-

ROM/Flash:较慢/便宜(但NOR Flash可较快随机读取)

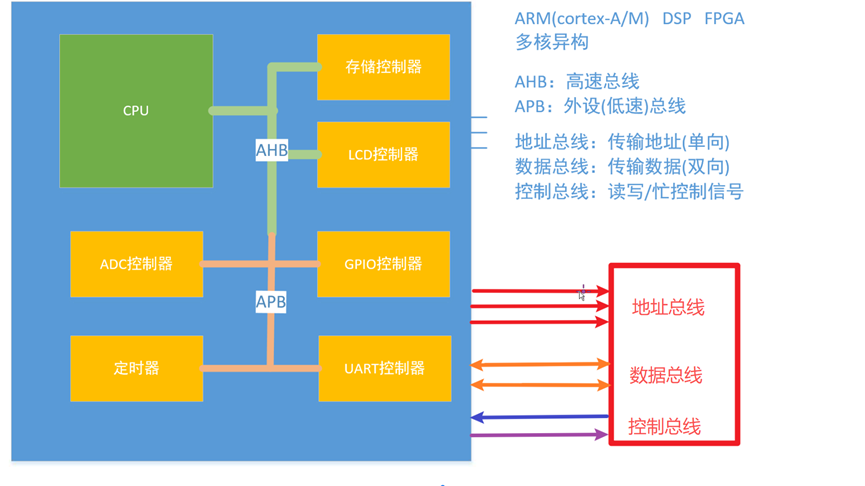

四、系统总线与SOC(片上系统)

现代ARM处理器往往以SOC形式集成,通过总线连接各个模块。

4.1 总线类型

-

地址总线 :单向,用于传输地址信息,确定访问的存储单元或外设。

-

数据总线 :双向,用于传输数据。

-

控制总线 :传输读写控制信号、忙信号、中断请求等。

4.2 AMBA总线协议

ARM公司定义了AMBA(高级微控制器总线架构)标准,常见总线有:

-

AHB(高速总线):连接高速模块,如CPU、存储控制器、DMA控制器、LCD控制器等。支持突发传输、流水线操作。

-

APB(外设(低速)总线):连接低速外设,如UART、定时器、I2C、ADC控制器等。通过桥接器与AHB相连,简化设计。

4.3 常见外设控制器

-

存储控制器:管理不同类型存储器(SDRAM、Flash)的时序和地址映射。

-

LCD控制器:驱动液晶显示屏,生成像素时钟和同步信号。

-

ADC控制器:模数转换,将模拟信号转换为数字值。

-

定时器:提供定时、计数、PWM输出等功能。

-

UART控制器:实现串行通信。

4.4 SOC概念

**SOC(片上系统)**将CPU、内存控制器、总线、外设控制器、甚至GPU等集成在同一芯片上,形成完整的系统。例如手机芯片(骁龙、麒麟)就是复杂的SOC。

五、内核结构与栈

理解程序如何执行是掌握体系结构的关键。

5.1 冯诺伊曼结构与哈佛结构

-

冯诺伊曼结构 :指令和数据存放在同一存储器中,通过同一总线访问(如PC和通用寄存器)。结构简单,但可能因总线争用导致瓶颈(冯诺伊曼瓶颈)。

-

哈佛结构 :指令和数据分别存放在独立的存储器中 ,有独立的总线,可同时访问,提高效率。现代处理器常采用改进型哈佛结构,即指令Cache和数据Cache分离,但共用外部存储器(如ARM Cortex-M)。

5.2 栈(Stack)详解

栈是内存中一种后进先出的数据结构,用于保存函数调用帧、局部变量、寄存器现场等。栈的操作方向与指针指向方式有多种类型,必须区分清楚:

增栈与减栈

-

增栈(Ascending Stack) :栈向高地址方向增长。压栈时SP增加,出栈时SP减小。

-

减栈(Descending Stack) :栈向低地址方向增长。压栈时SP减小,出栈时SP增加。ARM默认使用减栈。

空栈与满栈

-

空栈(Empty Stack):SP指向下一个空闲位置。压栈时先将数据存入SP指向的地址,然后SP移动;出栈时先移动SP,再取出数据。

-

满栈(Full Stack):SP指向最后一个压入的数据(即栈顶元素)。压栈时先移动SP,再将数据存入新位置;出栈时先取出数据,再移动SP。

组合类型(要知道)

-

满增栈:SP指向最后压入的数据,栈向高地址增长。

-

空增栈:SP指向下一个空闲位置,栈向高地址增长。

-

满减栈 :SP指向最后压入的数据,栈向低地址增长。这是ARM体系结构的默认栈类型(

FD,Full Descending)。 -

空减栈:SP指向下一个空闲位置,栈向低地址增长

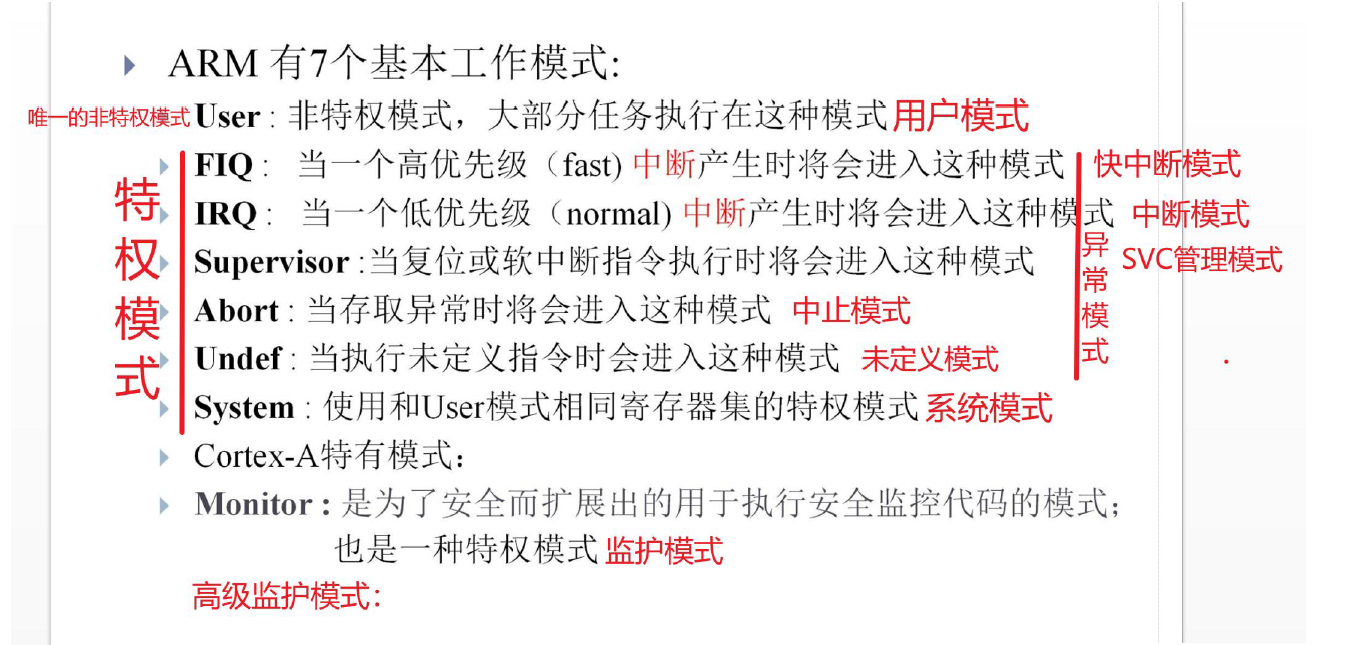

六、ARM的基本工作模式与Cortex-A扩展(重点)

七个工作模式和两个扩展模式要记住。

七、多核异构与相关术语

7.1 多核异构

现代复杂SOC常集成多种处理器核心,以平衡性能、功耗和专用计算需求。例如:

-

ARM Cortex-A + Cortex-M:A核运行操作系统,M核处理实时控制。

-

ARM + DSP:专用于音频、视频编解码。

-

ARM + FPGA:提供硬件可重构的加速能力。

7.2 相关术语辨析

-

CPU:中央处理单元,指处理器核心。

-

SOC:片上系统,集成CPU、内存、外设等。

-

MCU :微控制器,通常指包含CPU、RAM、ROM、外设的单芯片,用于嵌入式控制。

-

MPU :微处理器,通常指不带集成外设的高性能CPU(需外接内存和外设)。

-

DSP:数字信号处理器,针对信号处理算法优化。

-

FPGA:现场可编程门阵列,硬件可编程,可实现自定义逻辑。

八、扩展知识

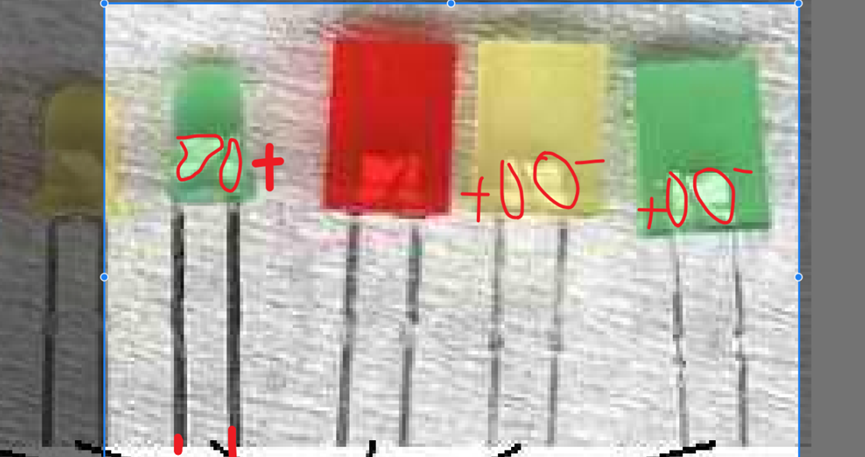

8.1 二极管导通

-

阳极(正极) 接 电源的正极(高电位)。

-

阴极(负极) 接 电源的负极(低电位)

如何区分二极管的正负极:

看引脚长短(长的为正,短的为负)

看内部结构(小的为正,大的是负):

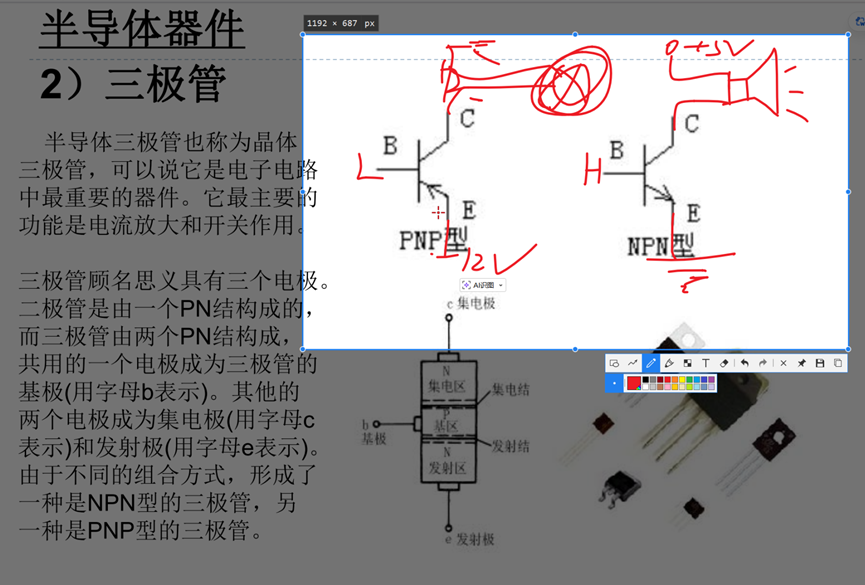

8.2 三极管导通

看箭头,PN结得正偏才能导通,PNP是B处低电平导通,NPN是高电平导通

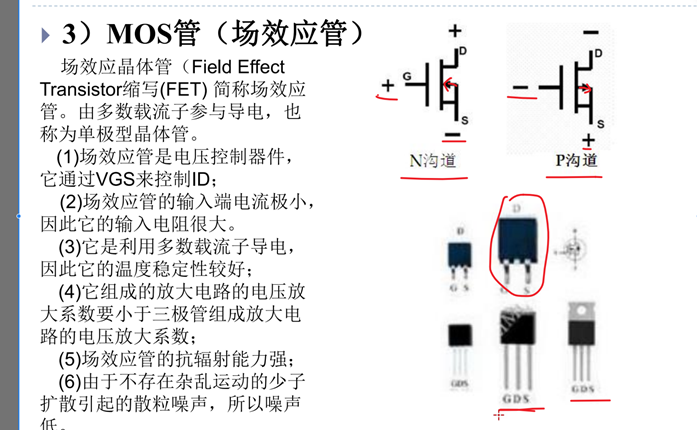

8.3 MOS管导通

也是看箭头

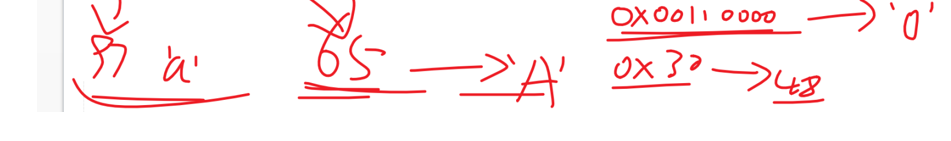

8.4常用ASCII码

大A小a和数字0都要记住(65、97、48)

九、总结

本文从ARM处理器内核出发,逐步扩展到存储器、总线、SOC以及程序执行机制,全面梳理了有关ARM的大部分专业术语 。理解这些概念不仅有助于嵌入式开发,也为深入学习计算机体系结构奠定基础。希望读者能通过本篇文章建立起清晰的知识脉络,并在实践中灵活运用。