目录

[一、CPU 结构(软考高频:部件功能 + 寄存器作用)](#一、CPU 结构(软考高频:部件功能 + 寄存器作用))

[1. CPU 整体组成](#1. CPU 整体组成)

[2. 运算器核心部件(必考功能)](#2. 运算器核心部件(必考功能))

[3. 控制器核心部件(软考最高频考点)](#3. 控制器核心部件(软考最高频考点))

[4. 寄存器分类总结](#4. 寄存器分类总结)

[CPU 结构 真题练习题(10 道)](#CPU 结构 真题练习题(10 道))

[二、流水线技术(软考重难点:概念 + 计算 + 冲突)](#二、流水线技术(软考重难点:概念 + 计算 + 冲突))

[1. 指令执行的 3 个基础阶段](#1. 指令执行的 3 个基础阶段)

[2. 流水线核心指标(软考必考计算)](#2. 流水线核心指标(软考必考计算))

[3. 流水线冲突(3 类,软考常考概念)](#3. 流水线冲突(3 类,软考常考概念))

[流水线 真题练习题(8 道,含计算)](#流水线 真题练习题(8 道,含计算))

[三、存储体系(主存 / 辅存 + 层次结构,软考必背)](#三、存储体系(主存 / 辅存 + 层次结构,软考必背))

[1. 存储层次结构(从快到慢)](#1. 存储层次结构(从快到慢))

[2. 主存储器(内存,主机内部,CPU 可直接访问)](#2. 主存储器(内存,主机内部,CPU 可直接访问))

[3. 辅助存储器(外存,CPU 不能直接访问)](#3. 辅助存储器(外存,CPU 不能直接访问))

[4. 局部性原理(Cache 存在的基础)](#4. 局部性原理(Cache 存在的基础))

[存储体系 真题练习题(10 道)](#存储体系 真题练习题(10 道))

一、CPU 结构(软考高频:部件功能 + 寄存器作用)

核心知识点精讲

CPU(中央处理器)是计算机的运算和控制核心 ,由运算器、控制器、寄存器组 三大部分组成,总线负责连接各部件。

1. CPU 整体组成

- 运算器 :负责数据运算(算术 + 逻辑)

- 控制器 :负责指令控制(取指、译码、发命令)

- 寄存器组:CPU 内部高速存储单元,速度远快于内存

- 内部总线:连接运算器、控制器、寄存器,传输数据 / 地址 / 控制信号

2. 运算器核心部件(必考功能)

运算器核心是算术逻辑单元 ALU,搭配辅助部件:

- ALU(算术逻辑单元)

核心部件,完成算术运算 (加减乘除)、逻辑运算(与或非、异或、比较) - 累加寄存器 AC

存放运算的操作数 / 运算结果,ALU 运算时暂存数据 - 状态条件寄存器 PSW

存放运算状态标志:**进位 (C)、零 (Z)、负 (N)、溢出 (O)**,用于判断程序分支 - 通用寄存器

存放临时数据、地址,减少 CPU 访问内存的次数 - 数据缓冲寄存器 DR

暂存内存 / 外设传来的数据,匹配速度差异

口诀:运算器管算数 + 逻辑,ALU 是核心,累加器存结果,状态寄存器记标志。

3. 控制器核心部件(软考最高频考点)

控制器负责自动取指令、分析指令、执行指令,控制整个计算机协同工作:

-

程序计数器 PC(指令计数器)

存下一条要执行的指令地址

顺序执行时,PC 自动 + 1;跳转时,PC 存入目标地址

-

指令寄存器 IR

存放当前正在执行的指令,CPU 执行指令期间不会改变

-

指令译码器 ID

解析 IR 中的指令,判断要做什么操作(加 / 减 / 读内存等)

-

时序控制部件

产生时钟信号,控制指令执行的节奏

-

微操作控制单元 CU

向各部件发控制命令,完成指令执行

口诀:PC 存下址,IR 存现令,译码器解析,控制器发命令。

4. 寄存器分类总结

- 通用寄存器:用户可读写,存数据 / 地址

- 专用寄存器:系统专用,用户不可直接修改(PC、IR、PSW、AR 地址寄存器)

CPU 结构 真题练习题(10 道)

-

下列不属于 CPU 运算器部件的是()

A. ALU B. 累加器 C. 程序计数器 PC D. 状态寄存器

答案:C

解析:PC 属于控制器,运算器包含 ALU、累加器、状态寄存器、通用寄存器。

-

程序计数器 PC 中存放的内容是()

A. 当前指令 B. 下一条指令地址 C. 操作数 D. 运算结果

答案:B

解析:PC 核心功能是存储下一条指令的地址,顺序执行自动 + 1。

-

负责解析指令、确定指令操作类型的部件是()

A. 指令寄存器 B. 指令译码器 C. 累加器 D. 数据寄存器

答案:B

解析:指令译码器对 IR 中的指令进行译码,识别操作类型。

-

存放运算进位、溢出、零标志的寄存器是()

A. PC B. PSW C. IR D. AC

答案:B

解析:PSW 状态条件寄存器,记录运算状态标志。

-

CPU 中速度最快的存储部件是()

A. 主存 B. 寄存器 C. Cache D. 硬盘

答案:B

解析:寄存器在 CPU 内部,速度远高于 Cache、内存、辅存。

-

下列属于控制器核心部件的是()

A. ALU B. 通用寄存器 C. 指令寄存器 IR D. 数据缓冲器

答案:C

解析:IR、PC、译码器均为控制器部件,其余为运算器。

-

累加寄存器 AC 的主要作用是()

A. 存指令地址 B. 暂存运算操作数 / 结果 C. 译码指令 D. 存状态标志

答案:B

解析:AC 为 ALU 运算提供暂存空间,存放操作数和结果。

-

计算机执行指令的过程中,当前指令存放在()

A. PC B. IR C. DR D. AR

答案:B

解析:指令寄存器 IR 存放正在执行的指令。

-

算术逻辑单元 ALU 不能完成的操作是()

A. 加法 B. 逻辑与 C. 指令译码 D. 数值比较

答案:C

解析:指令译码是控制器的译码器完成,ALU 只做算术 + 逻辑运算。

-

顺序执行指令时,程序计数器 PC 的变化规律是()

A. 自动 + 1 B. 自动 - 1 C. 保持不变 D. 随机变化

答案:A

解析:顺序执行时,PC 自动加 1,指向下一条指令。

二、流水线技术(软考重难点:概念 + 计算 + 冲突)

核心知识点精讲

流水线是将指令执行过程拆分,多指令重叠执行 的技术,目的是提高 CPU 指令执行效率。

1. 指令执行的 3 个基础阶段

一条指令的执行分为:

- 取指(FI):从内存取指令

- 译码 / 分析(ID):解析指令、取操作数

- 执行(EX):ALU 运算、写回结果

复杂流水线可拆分为:取指→译码→取数→执行→写回(5 级)

2. 流水线核心指标(软考必考计算)

(1)流水线周期

流水线执行时间由最慢的阶段 决定,这个阶段的时间就是流水线周期 Δt。

(2)单指令执行时间

无流水线:T=t1+t2+...+tn

有流水线:单指令时间不变,多指令重叠执行

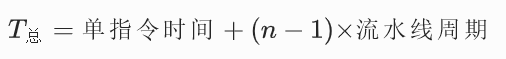

(3)n 条指令总执行时间

公式:

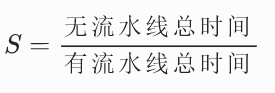

(4)加速比

加速比:

加速比越大,效率提升越明显

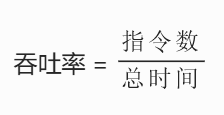

(5)吞吐率

单位时间内执行的指令数,

3. 流水线冲突(3 类,软考常考概念)

- 结构冲突:硬件资源竞争(如同时取指 + 取数抢内存)

- 数据冲突:后续指令用到前序指令未写回的结果

- 控制冲突:跳转 / 分支指令,导致流水线断流

流水线 真题练习题(8 道,含计算)

-

流水线技术的核心目的是()

A. 减少单指令执行时间 B. 提高指令吞吐率 C. 降低硬件成本 D. 减少功耗

答案:B

解析:流水线不缩短单指令时间,而是让多指令重叠,提升单位时间执行指令数。

-

一条指令分为取指 (2ns)、译码 (1ns)、执行 (3ns),流水线周期为()

A. 1ns B. 2ns C. 3ns D. 6ns

答案:C

解析:流水线周期 = 最慢阶段时间,执行阶段 3ns 最大。

-

同上 3 级流水线,执行 100 条指令的总时间为()

A. 300ns B. 303ns C. 600ns D. 103ns

答案:B

解析:总时间 = 单指令时间 +(n-1)× 周期 = (2+1+3) + 99×3 = 6+297=303ns。

-

流水线加速比的含义是()

A. 流水线速度 / 非流水线速度 B. 非流水线总时间 / 流水线总时间

C. 指令数 / 执行时间 D. 执行时间 / 指令数

答案:B

解析:加速比 = 无流水线总耗时 ÷ 有流水线总耗时。

-

下列属于流水线数据冲突的是()

A. 两条指令同时抢用 ALU B. 跳转指令导致断流

C. 后指令用前指令未写回的结果 D. 取指和取数抢内存

答案:C

解析:A/D 是结构冲突,B 是控制冲突,C 是数据冲突。

-

5 级流水线,周期 2ns,执行 50 条指令总时间为()

A. 100ns B. 108ns C. 50ns D. 200ns

答案:B

解析:对于5级流水线,执行n条指令的总时间为:(n + 流水线级数 - 1) × 时钟周期。

代入n=50,流水线级数=5,时钟周期=2ns,得:

(50 + 5 - 1) × 2 = 54 × 2 = 108ns。

因此,正确答案为B. 108ns。

-

无流水线执行 10 条指令需 100ns,流水线执行需 20ns,加速比为()

A. 0.2 B. 5 C. 8 D. 10

答案:B

解析:加速比 = 100/20=5。

-

流水线中,分支跳转指令会引发()

A. 结构冲突 B. 数据冲突 C. 控制冲突 D. 资源冲突

答案:C

解析:跳转 / 分支指令破坏指令顺序,引发控制冲突。

三、存储体系(主存 / 辅存 + 层次结构,软考必背)

核心知识点精讲

计算机存储体系采用层次化结构 ,核心原则:速度越快,容量越小,成本越高;速度越慢,容量越大,成本越低。

1. 存储层次结构(从快到慢)

寄存器(CPU 内)→ Cache(高速缓存)→ 主存(内存)→ 辅存(外存)

- 上层:速度快、容量小、成本高

- 下层:速度慢、容量大、成本低

2. 主存储器(内存,主机内部,CPU 可直接访问)

(1)按读写特性分类

- RAM(随机存取存储器)

- 可读可写,断电数据丢失

- 分为:

SRAM(静态 RAM):速度快,用作 Cache

DRAM(动态 RAM):需定期刷新,用作内存条

- ROM(只读存储器)

- 只读不写,断电数据不丢失

- 存放 BIOS、固件等系统固定程序

(2)主存技术指标

- 存储容量:存储二进制数据的总量,单位 B/KB/MB/GB

- 存取时间:从发出读命令到数据读出的时间

- 存取周期:连续两次访问的最小间隔

3. 辅助存储器(外存,CPU 不能直接访问)

辅存属于外部设备,用于永久存储大量数据,断电不丢失:

- 硬盘(HDD/SSD):最常用辅存,容量大

- U 盘 / 闪存:半导体辅存,便携

- 光盘:只读 / 可擦写,容量较小

核心区别:CPU直接访问主存,访问辅存必须先调入主存。

4. 局部性原理(Cache 存在的基础)

- 时间局部性:刚访问的数据,短期内可能再次访问

- 空间局部性:访问某地址,附近地址大概率也会被访问

存储体系 真题练习题(10 道)

-

计算机存储层次中,速度最快的是()

A. 主存 B. Cache C. 寄存器 D. 硬盘

答案:C

解析:寄存器在 CPU 内部,速度 > Cache > 主存 > 辅存。

-

下列属于主存 RAM 特点的是()

A. 断电不丢失 B. 只读 C. 可读可写,断电丢失 D. 用作 BIOS 存储

答案:C

解析:RAM 随机存取,可读可写,易失性(断电丢数据)。

-

用作高速缓存 Cache 的存储器是()

A. DRAM B. SRAM C. ROM D. 硬盘

答案:B

解析:SRAM 速度快、无需刷新,用作 Cache;DRAM 用作内存条。

-

存放计算机 BIOS 程序的存储器是()

A. RAM B. ROM C. Cache D. U 盘

答案:B

解析:ROM 只读不丢数据,存放固件 / BIOS。

-

CPU 不能直接访问的存储器是()

A. 主存 B. 寄存器 C. 硬盘 D. Cache

答案:C

解析:辅存(硬盘)需调入主存后,CPU 才能访问。

-

下列属于辅助存储器的是()

A. 内存条 B. 寄存器 C. SSD 固态硬盘 D. Cache

答案:C

解析:SSD 是辅存,其余均为主机内部存储。

-

存储体系层次化的核心依据是()

A. 容量、速度、成本的权衡 B. 功耗控制 C. 体积大小 D. 接口类型

答案:A

解析:层次结构平衡速度、容量、成本,提升整体性能。

-

DRAM 需要定期刷新的原因是()

A. 提高速度 B. 防止数据丢失 C. 扩大容量 D. 降低功耗

答案:B

解析:DRAM 靠电容存储电荷,电荷泄漏需刷新保持数据。

-

程序局部性原理是()的设计基础

A. 主存 B. Cache C. 辅存 D. 寄存器

答案:B

解析:Cache 利用时间 / 空间局部性,缓存高频数据。

-

主存与辅存的核心区别是()

A. 容量大小 B. CPU 是否直接访问 C. 读写速度 D. 存储介质

答案:B

解析:CPU 可直接寻址主存,辅存必须调入主存才能访问。

软考备考极简总结

- CPU:运算器管计算(ALU 核心),控制器管指令(PC 存下址、IR 存现令)

- 流水线:周期 = 最慢阶段,总时间 = 单指令 +(n-1)× 周期,分 3 类冲突

- 存储:寄存器→Cache→主存→辅存;RAM 易失、ROM 非易失;CPU 不直接访问辅存