【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

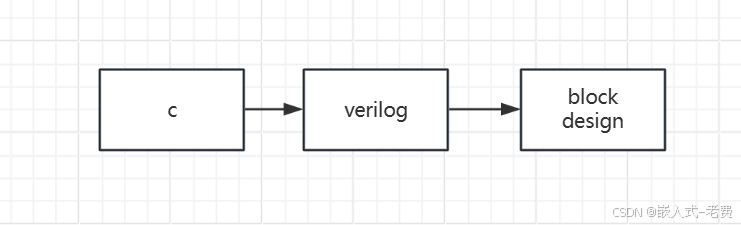

我们都知道,在xlinx的fpga上面,如果需要做硬编码,有两种方式,一种是verilog,一种是hls。两种都是xilinx支持的编码方式。在这两种方式当中,hls虽然是用c或者是c++编写,最终也是要变成verilog,部署在block design之中的。目前hls已经非常好用,但是还是有很多人怀疑hls,那么对于一般的场景,verilog和hls应该怎么使用呢?

1、hls适合算法,verilog更适合接口

如果是基础接口协议,毫无疑问,那就是verilog。但是偏算法类的ip,再用verilog来做,就效率很低了。这个时候,特别适合用hls来进行开发。

2、hls更适合软件专业的同学入手

fpga本身如果只是用于接口,用于ad/da采样,那就大材小用了。其实fpga的并发性,对于算法的优化是非常合适的。加上zynq这种二合一芯片,arm和fpga可以同时访问ddr,两者可以通过dma共享数据的内容,hls就更加适合软件专业的同学入手了。

3、hls设计完了,需要连接到block design当中测试

如果是hls设计完了,建议先本地仿真测试下。**测试没有问题之后,再把hls生成的ip合并到最终的block design当中,这是非常关键的一步。**我们自己设计的ip有没有用,只有放到block design里面去,才能发挥出它应有的作用。

4、用好dma

ip如果要访问ddr,一种方式就是通过m_axi自己去读取ddr,还有一种方式就是通过dma的方式进行处理,比如axis接口。有了dma,就可以通过mm2s获取到数据,然后送给ip。而ip这边处理完数据之后,接着发送给dma,通过s2mm写回ddr。这样就能达到一个高效处理io数据的目的。

5、ddr数据+ip算法是一个标配

很多时候,外设的数据都是通过模块,或者外设芯片,或者是网络协议送到ddr的。这部分数据如果用传统的cpu去处理,很可能效率偏慢,或者处理不及时。这种情况下就可以采用hls ip实现算法的形式,去实现加速处理。

6、pragma关键字是hls实现的关键

我们虽然可以用c编写业务逻辑,但是c只是一层皮。在这层皮之下,哪些是输入,哪些是输出,哪些是寄存器部分,哪些是m_axi,哪些是axis,这些部分都是通过pragma可以设置好的。而pragma关键字的根本目的,就是明确区分,这段代码应该最终综合成什么样的电路,这还是比较重要的。