【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

前面我们也写了两个ip,一个是直接显示led的,另外一个是带axi总线。某种意义上说,这已经是大部分场景下ip的使用方法。但那只是满足非接口类ip需求,算法类ip的话,就还需要了一部分内容,那就是如何从ddr读取数据。

1、设计一个统计类的ip

这个ip的功能非常简单,就是设置好ddr地址、设置好数据的数量之后,然后ip就开始计数。等到所有计数结束之后,就可以触发一个中断给cpu。这就是ip的全部功能。和之前ip相比较,它最大的不同就是它可以访问内存,也就是ddr。就zynq而言,所有访问ddr的操作都是通过hp0接口完成的。

2、准备代码

代码部分其实是比较容易完成的。这里先不考虑ip的效率,暂时只实现功能。所以说要实现这一点,只要对interface做一些改变就可以了。

#include <ap_cint.h>

uint32 result;

uint32 _average_int(uint32* array, int num)

{

uint32 sum = 0;

int i;

for(i = 0; i < num; i++)

{

sum += array[i];

}

return sum / num;

}

uint32 led_control(uint32* array, int num)

{

#pragma HLS INTERFACE s_axilite port=return

#pragma HLS INTERFACE s_axilite port=num

#pragma HLS INTERFACE m_axi depth=1024 offset=slave port=array

result = _average_int(array, num);

return result;

}**大家可以观察一下,这里面最大的区别就是array的设置。**首先,它的类型是m_axi,其次最大depth是1024,最后访问类型是slave,这些都代表说它要访问ddr的。

3、综合、导出rtl

综合是为了确认语法有没有问题,导出rtl则是为了确认c可以转变成verilog。

4、准备vivado工程

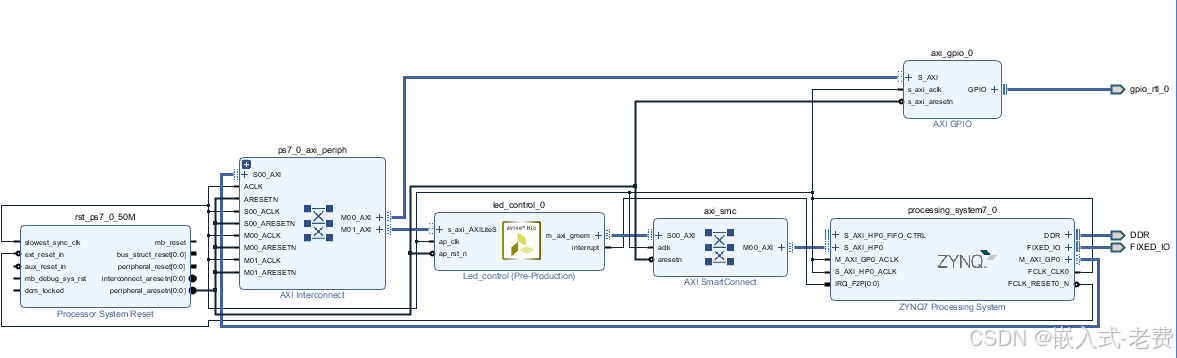

这里的vivado工程就是准备一个cpu,准备一个gpio,其他都使用默认连线就可以了,这就保证了整个最小系统至少是可以运行起来的。

5、导入ip,开始连线

vivado工程都准备好了之后,就可以导入之前生成的ip。当然,ip选择soc类型的时候,要和vivado里面的类型保持一致,不然哪怕是路径都设对了,在添加ip的时候,也会找不到的。添加ip之后,一般还需要补充一个axi smart connect,ip通过smart connect,直连zynq的hp0。ip的中断,也要提前设置好。剩下的部分,就采用默认的方式就可以。不出意外,你就可以看到这样的框图,

6、调整和确认

连线什么都设置好之后,这个时候通常还要double check下,看看有没有连线出错的,有没有没有连上线的。都没有问题之后,就可以继续综合、生成bitfile、生成sdk代码了。