目录

[i.MX6ULL 处理器内核:单核 ARM Cortex-A7 指令集版本:ARMv7-A 架构(32 位)](#i.MX6ULL 处理器内核:单核 ARM Cortex-A7 指令集版本:ARMv7-A 架构(32 位))

[当异常产生时,ARM core:](#当异常产生时,ARM core:)

计算机的指令集就是用指令对计算机实现控制和计算的指令集合

复杂指令集:RISC(reduced instruction set computer)

芯片面积大,加工成本高,复杂,体积大,功耗大

精简指令集:CISC(complex instruction set computer)芯片面积小,加工成本低,简单,体积小,功耗小

计算机系统的硬件组成:输入设备、输出设备、存储器

高速缓存存储器(Cache)

Cache在内核里,CPU直接从Cache中读取数据,提高了CPU访问数据的效率

其中,Cache又分为了:

Icache(instruction cache)指令缓存,专门用来存储指令

dcache(data cache)数据缓存,专门用来存放数据

总线通信

单总线通信:通过一根线/一组线和外设通信,和某个外设通信时,其他外设接不进来

双总线通信:

- AHB总线:先进高速总线(USB、网卡、RAM),连接通信速率快的外设

- APB总线:先进外设总线(GPIO、UART),连接通信速率慢的外设

flash

nor flash : 每个字节可以被寻址,地址总线和数据总线

nand flash : 无法被寻址,以固定块大小写入或读取数据512byte

寄存器

R0 ~R12:内核中的通用寄存器,存放数据,但本身没地址,搭配ALU(算术运算单元)来使用

(R13)SP寄存器:stack(栈) pointer 栈指针寄存器,先进后出,用来管理栈区,且永远指向栈顶

(R14)LR寄存器:link register 链接寄存器,保存函数返回地址

(R15)PC寄存器:program counter 程序计数器,相当于一个指针,指向当前代码正在执行的下一条指令

CPSR寄存器:current program status register 当前程序状态寄存器,保存程序运行到某一步时的状态

SPSR寄存器:save program status register 保存/备份程序状态寄存器,异常发生时,保存CPSR寄存器中的程序状态

MMU:mermory manager unit 内存管理单元,主要针对于虚拟内存,由于管理虚拟内存到物理内存的映射,从而提高物理内存的利用率,在裸机阶段必须关闭MMU

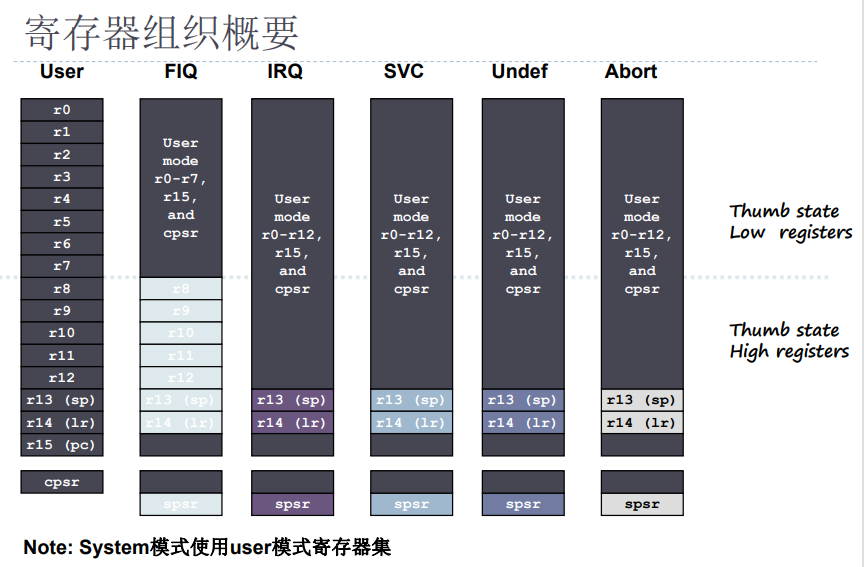

ARM有37个32比特长的寄存器

- 一个用作PC

- 一个用作CPSR

- 5个用作SPSR

- 30个通用寄存器

Cortex体系结构下有40个32比特长的寄存器

Cortex-A多出3个寄存器,Monitor模式 r13_mon , r14_mon , spsr_mon

i.MX6ULL 处理器内核:单核 ARM Cortex-A7 指令集版本:ARMv7-A 架构(32 位)

处理器工作模式:ARM有7个基本的工作模式

USER : 非特权模式,大部份任务执行在这种模式,且时用到的寄存器最少

FIQ:当一个高优先级(fast)中断产生时将会进入这种模式

IRQ:当一个低优先级(normal)中断产生时将会进入这种模式

Supervisor:当复位或软中断指令(SVC)执行时将会进入这种模式

Abort:当存取异常时将会进入这种模式

Undef:当执行未定义指令时将会进入这种模式

System:使用和User模式相同的寄存器集的特权模式

Cortex-A特有模式:Monitor是为了安全而扩展出的用于执行安全监控代码的模式,也是一种特权模式

异常处理

当异常产生时,ARM core:

拷贝CPSR到SPSR_<mode>

设置适当的CPSR位:

- 改变处理器状态进入ARM态

- 改变处理器模式进入相应的异常模式

- 设置中断禁止位禁止相应中断(如果需要)

保存返回地址到LR_<mode>

设置PC为相应的异常向量

返回时,异常处理需要:

从SPSR_<mode>恢复CPSR

从LR_<mode>恢复PC

Note : 这些操作只能在ARM态执行