一、引言

存储体系与系统可靠性是软考网络工程师考试中计算机硬件基础模块的核心内容,在历年选择题中占比约 5-8 分,是考生必须掌握的基础知识点。

(一)核心概念定义

存储体系是计算机系统中由不同速度、容量、成本的存储设备构成的层次化架构,旨在平衡性能与成本的矛盾;系统可靠性是衡量网络设备、服务器、存储系统等核心基础设施连续服务能力的关键指标,是网络架构设计的核心评估维度。

(二)历史发展脉络

存储体系从早期单级主存结构发展为 1960 年代引入 Cache 的两级结构,1970 年代虚拟内存技术成熟后形成三级存储体系,2000 年后固态硬盘普及进一步优化了外存层级的性能。可靠性计算体系起源于 1950 年代的航空航天工业,1980 年代后广泛应用于计算机系统和网络架构设计,形成了标准化的指标体系和计算方法。

(三)知识点覆盖

本文将从多级存储结构原理、主存核心技术、Cache 工作机制、外存分类、系统可靠性指标、串并联系统可靠性计算六个维度展开,涵盖所有高频考点和易混易错点。

二、多级存储结构核心原理

(一)核心矛盾与设计目标

计算机存储系统的核心矛盾是 CPU 运算速度与存储设备访问速度的差距、存储容量需求与单位成本的矛盾。多级存储结构通过金字塔式的层次设计,使整个系统的速度接近最高速存储设备、容量接近最大容量存储设备、单位成本接近最低成本存储设备。

(二)层次结构与性能参数

性能排序:寄存器(纳秒级访问延迟,容量 KB 级)> Cache(1-10 纳秒延迟,容量 MB 级)> 主存(10-100 纳秒延迟,容量 GB 级)> 外存(毫秒级延迟,容量 TB 级)

成本排序 :寄存器单位成本最高,依次向下递减,外存单位成本最低

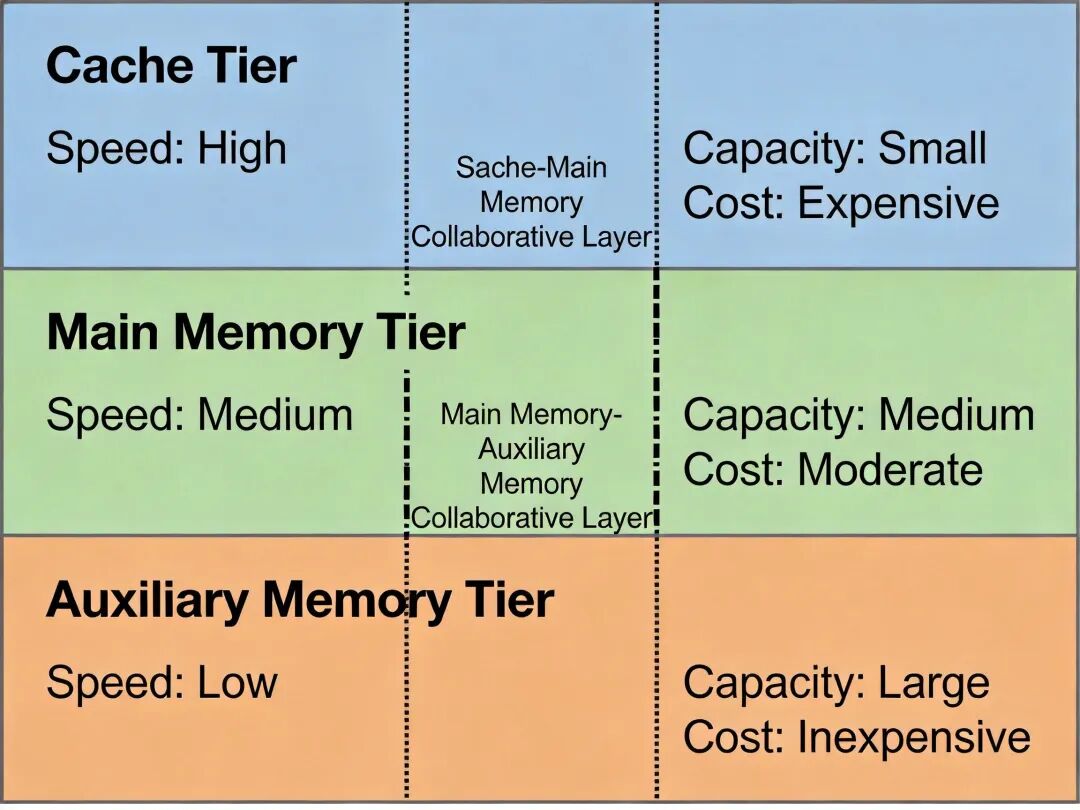

两个核心协作层次

(1)Cache - 主存层次 :完全由硬件逻辑实现,对操作系统和应用程序透明,主要解决 CPU 与主存的速度差距问题,可将存储系统的平均访问速度提升一个数量级

(2)主存 - 辅存层次 :由操作系统的内存管理模块和存储硬件协同实现,形成虚拟内存空间,可使应用程序获得远大于物理主存的寻址空间,解决主存容量不足的问题

(三)技术优势与局限性

优势 :在性能提升 10-100 倍的前提下,系统整体存储成本仅增加 5%-15%,性价比提升显著

局限性 :依赖程序的局部性原理,当程序出现大量随机访问、局部性较差时,会出现 Cache 命中率大幅下降、虚拟内存缺页频繁等问题,反而导致系统性能降低

多级存储结构金字塔示意图,标注各层级的速度、容量、成本参数和两个核心协作层次

三、主存核心技术与容量计算

(一)主存组成与分类

主存由**随机存储器(RAM)和只读存储器(ROM)**两类芯片共同组成,承担系统运行时的指令和数据存储任务。

RAM(随机存取存储器)

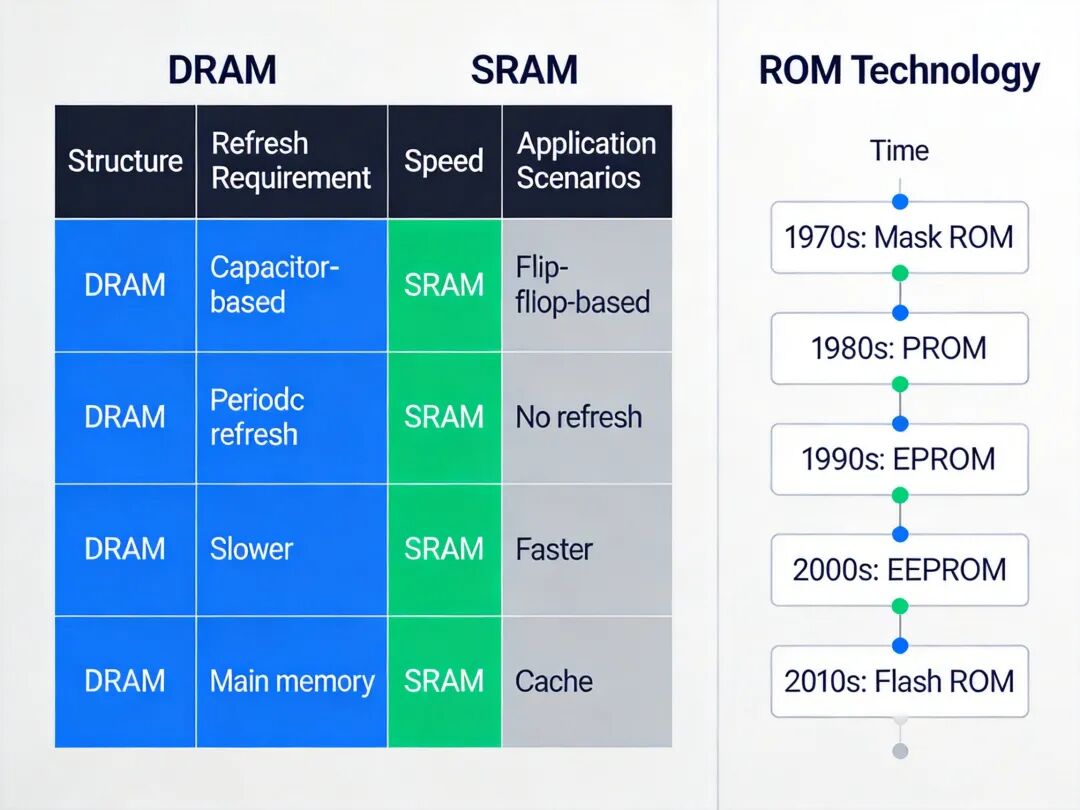

(1)DRAM(动态 RAM) :利用电容存储电荷实现数据存储,需每隔 2-8ms 进行刷新操作防止数据丢失,集成度高、成本低,是当前主存的主流存储介质,DDR5 DRAM 的访问带宽可达 4800MT/s

(2)SRAM(静态 RAM) :利用触发器电路存储数据,无需刷新,访问速度是 DRAM 的 5-10 倍,但集成度低、成本高,仅用于 Cache 等对速度要求极高的场景

ROM(只读存储器)

(1)特点:断电后数据不丢失,主要用于存储 BIOS 等系统启动必需的固件程序

(2)技术演进路线 :掩膜 ROM(出厂固化,不可修改)→ PROM(一次可编程)→ EPROM(紫外光照射擦除,可多次编程)→ EEPROM(电信号擦除,可按字节修改)→ Flash Memory(闪存,按块擦除,集成度更高)

(二)主存容量计算方法

核心公式:主存容量 = 存储单元个数 × 存储单元字长

(1)存储单元个数由地址总线宽度决定,N 位地址总线可寻址 2^N 个存储单元

(2)存储单元字长由数据总线宽度决定,常见为 8 位(1 字节)、16 位、32 位等

地址范围计算方法 :存储单元个数 = 结束地址 - 起始地址 + 1

(1)真题案例:地址范围从 A4000H 到 CBFFFH,按字节编址,单元数 = CBFFFH - A4000H + 1 = 28000H = 2×16^4 + 8×16^3 = 163840 字节 = 160KB

存储芯片扩展计算 :总芯片数 = 主存总容量 / 单片芯片容量

(1)案例:用容量为 16K×8 位的 SRAM 芯片组成 64K×16 位的主存,总芯片数 = (64K×16)/(16K×8) = 8 片

(三)易混点辨析

Flash 闪存属于非易失性存储,可替代 ROM 用于固件存储、U 盘、SSD 等场景,但不能替代 RAM 作为主存,原因是 Flash 按块擦除、写入前需先擦除,写入延迟是 RAM 的 1000 倍以上,且擦写次数有限,无法满足主存随机高速读写的要求。

DRAM 与 SRAM 结构对比表、ROM 技术演进路线图

四、Cache 与外存核心技术

(一)Cache 工作原理

Cache 位于 CPU 与主存之间,全部由 SRAM 芯片构成,基于程序的时间局部性(当前访问的指令或数据短期内可能被再次访问)和空间局部性(当前访问的地址附近的内容可能很快被访问)原理工作。

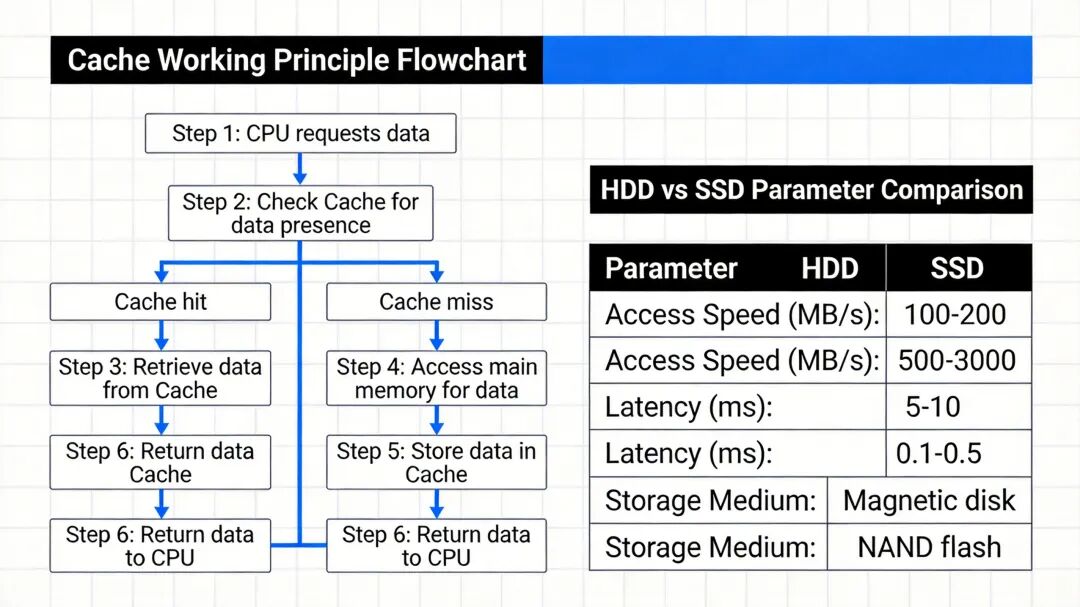

核心机制:CPU 访问内存时,先检查数据是否在 Cache 中,命中则直接从 Cache 读取,缺失则从主存读取并将相邻的一块数据载入 Cache,后续访问即可直接命中

地址映射:主存地址与 Cache 地址的映射完全由硬件自动完成,对软件透明,常见映射方式有直接映射、全相联映射、组相联映射三种

性能指标:Cache 命中率是核心性能参数,普通 CPU 的 L3 Cache 命中率可达 95% 以上,可使存储系统的平均访问延迟接近 Cache 速度

(二)外存分类与技术参数

外存即辅助存储器,用于长期存储系统数据,主要分为机械硬盘(HDD)和固态硬盘(SSD)两类。

HDD(机械硬盘)

(1)结构:由盘片、磁头、主轴电机、控制电路组成,通过磁头读取盘片上的磁信号实现数据存储

(2)参数:7200 转 HDD 的随机访问延迟约 5-10ms,连续读写速度约 100-200MB/s,容量可达 20TB 以上,单位成本约 0.05 元 / GB,平均无故障时间可达 100 万小时

SSD(固态硬盘)

(1)结构:由控制单元、NAND Flash 存储芯片(部分高端产品搭载 DRAM 缓存)组成,无机械部件

(2)接口类型:SATA 3.0 接口最大带宽 6Gbps,连续读写速度约 500MB/s;PCIe 4.0 x4 接口带宽可达 32Gbps,M.2 形态的 NVMe SSD 连续读写速度可达 7GB/s 以上;IDE 为旧式并行接口,已被淘汰,不支持 SSD

(3)对比:SSD 随机访问延迟约 0.1ms,是 HDD 的 1%,但单位成本约 0.5 元 / GB,写入寿命根据颗粒类型从 300 次到 3000 次擦写循环不等

(三)存储存取方式分类

随机存取 :按地址直接访问任意存储单元,访问时间与地址无关,主存采用该方式

相联存取 :按内容进行匹配访问,而非按地址访问,Cache 的标签存储器采用该方式,可实现地址的快速匹配

顺序存取 :访问需按存储介质的物理顺序进行,访问时间与数据位置相关,磁带采用该方式

直接存取 :介于随机和顺序存取之间,先定位到存储区域再顺序查找,HDD 采用该方式

Cache 工作原理流程图、HDD 与 SSD 技术参数对比表

五、系统可靠性核心指标

系统可靠性是网络架构设计、设备选型的核心评估指标,软考中主要考查四个核心指标的定义和计算。

(一)核心指标定义

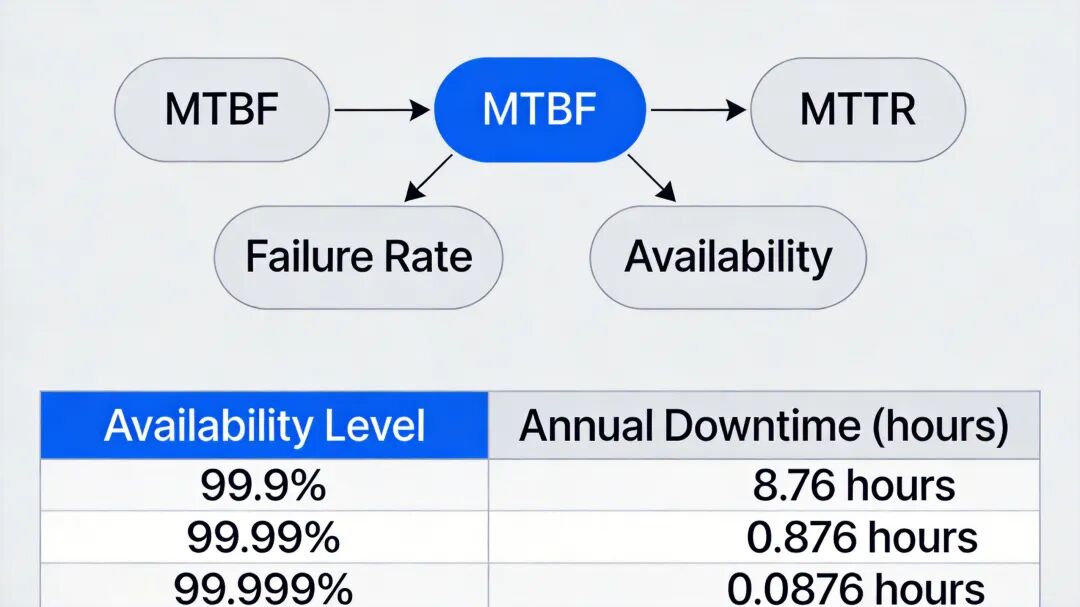

失效率(λ) :单位时间内系统发生故障的概率,单位通常为 Fit(1Fit=10^-9 / 小时),指每 10 亿小时运行发生 1 次故障

平均无故障时间(MTBF) :系统两次相邻故障之间的正常运行时间的平均值,MTBF = 1/λ,该值越高说明系统可靠性越好

平均故障修复时间(MTTR) :系统发生故障后,从故障发生到恢复正常服务所需的平均时间,反映系统的可维护性,该值越低说明系统故障恢复能力越强

可用性(A) :系统能够正常提供服务的时间占总运行时间的比例,计算公式为:A = MTBF / (MTBF + MTTR),通常用百分比或几个 9 表示,如 99.9% 可用性表示年 downtime 约 8.76 小时,99.999% 可用性表示年 downtime 约 5 分钟

(二)指标应用场景

核心路由器、核心交换机等关键网络设备的 MTBF 通常要求大于 100 万小时

电信级网络的可用性要求达到 99.999%,企业核心业务系统可用性要求达到 99.9% 以上

冗余设计、负载均衡等技术主要用于提升 MTBF,快速故障切换、热备份等技术主要用于降低 MTTR,两者共同提升系统可用性

系统可靠性指标关系示意图、不同可用性等级对应的年 downtime 对比表

六、串并联系统可靠性计算

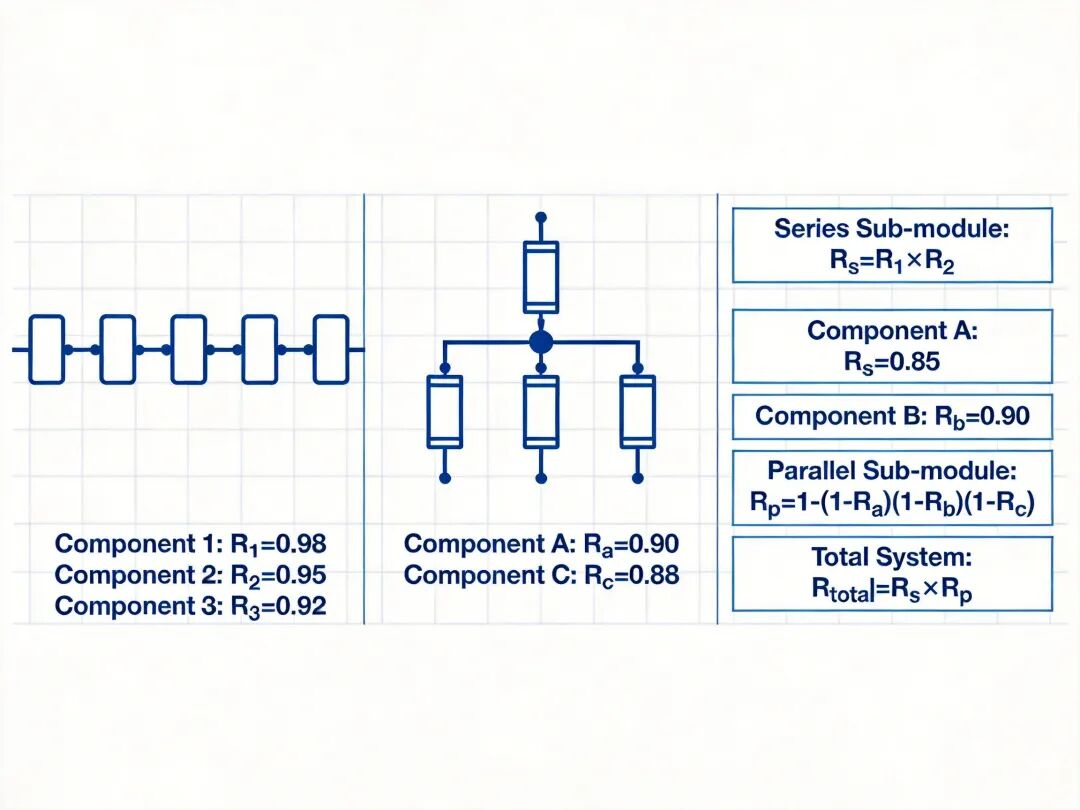

当系统由多个部件组成时,整体可靠性取决于部件的连接方式,是软考每年必考的计算题考点。

(一)串联系统可靠性计算

定义:所有部件都正常工作时,系统才能正常工作,任意一个部件失效都会导致系统整体失效,类似于链路串联、服务链的顺序执行

可靠性公式 :R = R₁ × R₂ × ... × Rₙ,其中 R₁到 Rₙ为各个部件的可靠性

特点 :部件数量越多,系统整体可靠性越低,N 个可靠性为 0.9 的部件串联,整体可靠性为 0.9^N,N=10 时仅为 0.3487

应用场景:网络中的接入层→汇聚层→核心层的串联链路、无冗余的服务调用链都属于串联系统,可靠性逐层降低

(二)并联系统可靠性计算

定义:只要有一个部件正常工作,系统就能正常工作,所有部件都失效时系统才会失效,类似于冗余链路、服务器集群

可靠性公式 :R = 1 - (1-R₁)×(1-R₂)×...×(1-Rₙ),先计算所有部件同时失效的概率,再用 1 减去该值得到系统正常工作的概率

特点 :部件数量越多,系统整体可靠性越高,N 个可靠性为 0.9 的部件并联,整体可靠性为 1 - 0.1^N,N=2 时为 0.99,N=3 时为 0.999

应用场景:核心设备的双电源、链路聚合、VRRP 冗余网关、服务器集群都属于并联系统,可大幅提升系统可靠性

(三)混联系统计算方法

计算原则:先拆分系统为独立的串联或并联子系统,分别计算子系统的可靠性,再将子系统视为整体部件,按连接关系计算整体可靠性

真题案例:某系统由两个串联的子系统 A 和 B 组成,A 由 2 个可靠性 0.9 的部件并联组成,B 由 3 个可靠性 0.9 的部件并联组成,整体可靠性为:(1-0.1²) × (1-0.1³) = 0.99 × 0.999 = 0.98901

串并联系统拓扑示意图、混联系统计算示例图

七、总结与备考建议

(一)核心知识点提炼

多级存储结构通过 Cache - 主存、主存 - 辅存两个层次平衡速度、容量、成本的矛盾,完全硬件实现和软硬件协同实现是两个层次的核心区别

主存容量计算需掌握地址范围的十六进制运算,芯片扩展计算需注意字扩展和位扩展的组合

SRAM 用于 Cache、DRAM 用于主存、Flash 用于外存,三者的特性差异是易混考点

系统可用性公式中 MTBF 与 MTTR 的位置不能混淆,串联可靠性相乘、并联先算全部失效再被 1 减是计算的核心原则

(二)软考考试重点提示

高频考点:主存容量计算、Cache 局部性原理、Flash 的特性、可用性计算、串并联系统可靠性计算,以上考点在近 5 年考试中出现频率超过 80%

易错点:地址计算时遗漏 + 1、并联可靠性公式直接相乘、混淆 SRAM 和 DRAM 的应用场景、Flash 可以替代 RAM 的错误表述

(三)最佳实践与学习建议

备考时需多做历年真题,重点练习十六进制地址计算、混联系统可靠性计算两类计算题,确保计算步骤正确

网络设计实践中,核心层需采用并联冗余设计提升可靠性,接入层可采用串联设计控制成本,存储系统需根据业务性能需求选择合适的存储介质和层次结构。