目录

[3、ARM 通用寄存器(ARM32 位内核)](#3、ARM 通用寄存器(ARM32 位内核))

[7、ARM 最小系统 & 存储芯片](#7、ARM 最小系统 & 存储芯片)

[8、ARM 7 种工作模式(ARM32)](#8、ARM 7 种工作模式(ARM32))

[9、异常向量表 & 异常处理](#9、异常向量表 & 异常处理)

[10、ARM 异常类型(完整答案)](#10、ARM 异常类型(完整答案))

[11、移位操作(ARM 指令)](#11、移位操作(ARM 指令))

1、指令集架构基础

(1)CISC:复杂指令集计算机

代表架构:X86(电脑、服务器 CPU)

核心特点:

- 指令数量多、指令长度不固定、功能复杂

- 芯片面积大、加工成本高、体积大、功耗高

- 2/8 效应:20% 的常用指令完成 80% 的工作,剩余 80% 复杂指令利用率极低

(2)RISC:精简指令集计算机

代表架构:ARM、MIPS、RISC-V

核心特点:

- 指令数量少、指令长度固定、格式统一

- 芯片面积小、加工成本低、功耗极低、体积小(便携式设备首选)

- 精简指令集架构 CPU

(3)基础概念

- 指令(instruction):CPU 能直接识别执行的最小操作命令

- 指令集:CPU 支持的所有指令的集合(硬件核心规范)

2、发展

ARM1 → ARM7 → ARM9 → ARM11→ Cortex 系列(主流)

- Cortex-A:Application 应用级场景:手机、平板、智能设备、应用电子领域、Linux 嵌入式开发(如 IMX6ULL)

- Cortex-R:Real-time 实时级场景:汽车电子、航空航天、工业控制(强实时性)

- Cortex-M:Micro 微控制器场景:MCU 单片机、物联网传感器、低功耗小设备

3、ARM 通用寄存器(ARM32 位内核)

(1)核心寄存器功能

- R0-R12:通用寄存器

用途:存放运算数据,与 ALU(算数逻辑单元)配合完成计算

- R13 (SP):栈指针寄存器

用途:管理栈空间,永远指向当前栈顶

- R14 (LR):链接寄存器

用途:保存子程序 / 函数调用的返回地址,函数执行完后自动跳转回原位置

- R15 (PC) :程序计数器

- 本质:指令地址指针

- ARM 三级流水线:PC取指 → 译码器译码 → kernal执行

- PC 指向正在取指的指令,而非正在执行的指令

- 指向当前代码正在执行的指令的下一条待取指的指令

(2)状态寄存器

- CPSR:当前程序状态寄存器

用途:保存当前 CPU的运行状态(标志位、工作模式、中断使能等)

- SPSR :保存 **/**备份程序状态寄存器

用途:异常 / 中断发生时,备份触发前的 CPSR,便于异常/中断处理结束后异常结束后,恢复原状态,每种异常模式都有独立的 SPSR(SPSR_svc/SPSR_irq 等)

(3)具体分布

-

R0~R7:所有模式共享

-

R8---R12:FIQ 模式有专用 banked(FIQ 下有 R8_fiq---R12_fiq);其他模式(用户、IRQ、SVC、ABT、UND):都用同一组 R8~R12(5个),没有各自的 banked。

-

R13和R14 :每个寄存器对应6个不同的物理寄存器。一个用于用户模式和系统模式 ,另外5个分别用于5种异常模式(fiq、irq、svc、abt、und)。

-

R15(PC):所有模式共享

-

SPSR:除用户模式、系统模式没有外,每种模式有自己的 SPSR

-

CPSR(Current Program Status Register):所有模式共享(1个)

4、核心硬件单元

(1) MMU:内存管理单元

- 全称:Memory Management Unit

- 功能:实现虚拟地址 ↔ 物理地址映射、内存权限管理、提高内存利用率

- 裸机开发必须关闭 MMU(无操作系统,不需要虚拟内存)

(2) Cache:高速缓存

- 作用:解决 CPU 与内存速度不匹配问题,CPU 优先访问 Cache,提高CPU访问数据的效率

- 分类:

- iCache:指令缓存(存放 CPU 要执行的指令)

- DCache:数据缓存(存放 CPU 运算的数据)

- 裸机开发配置:打开 iCache,关闭 DCache

(3) 架构分类

- 冯・诺依曼架构:指令和数据共用同一片内存、同一套总线

- 哈佛架构 :指令存储和数据存储完全独立(双总线),速度更快

- ARM Cortex-M/A 大多采用改进型哈佛架构

5、总线架构

(1)单总线(Single Bus)

定义 :所有外设(CPU、RAM、GPIO、UART 等)共用同一组总线(地址线 + 数据线 + 控制线)。

特点:

- 同一时间只能和一个外设通信

- 和某个外设通信时,其他外设必须断开、不能占用总线

- 结构简单、成本低,但效率低、速度慢

(2)双总线 / ARM 分层总线

-

AHB 总线(Advanced High-performance Bus)

- 全称:先进高性能总线

- 用途:连接高速设备

- 挂载设备:RAM、网卡、USB、LCD、NAND Flash 控制器

-

APB 总线(Advanced Peripheral Bus)

- 全称:先进外设总线

- 用途:连接低速、低带宽外设

- 挂载设备:GPIO、UART、I2C、SPI、定时器

-

桥接(Bridge)

- AHB 和 APB 之间有一个 APB 桥

- 作用:高速总线 ↔ 低速总线 数据转换、速率匹配

6、交叉编译

(1)定义

在一个平台编写编译程序,能够在另外一个平台运行程序(在X86 平台 上编写、编译代码,生成能在ARM 平台运行的程序)

(2)编译器区分

gcc:X86 架构本地编译器(编译电脑程序)arm-linux-gnueabihf-gcc:ARM 架构交叉编译器(编译嵌入式程序)

(3)查看系统架构命令

uname -a 显示系统的详细信息(Linux 系统查看 CPU 架构、内核版本等)

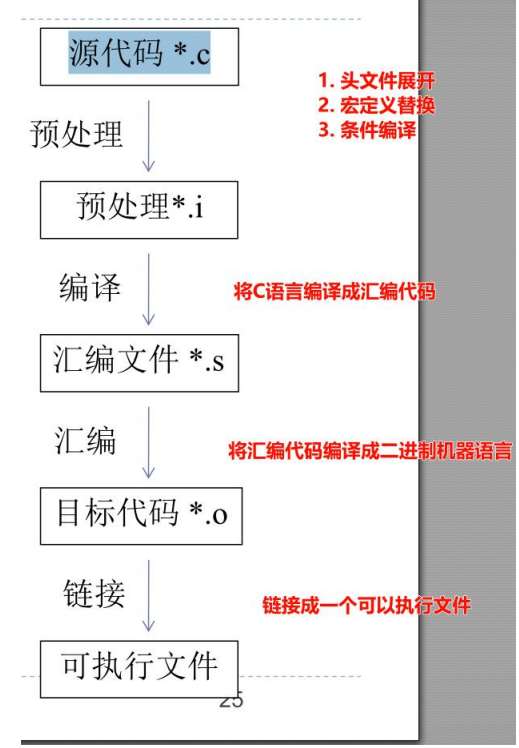

(4)编译器编译流程

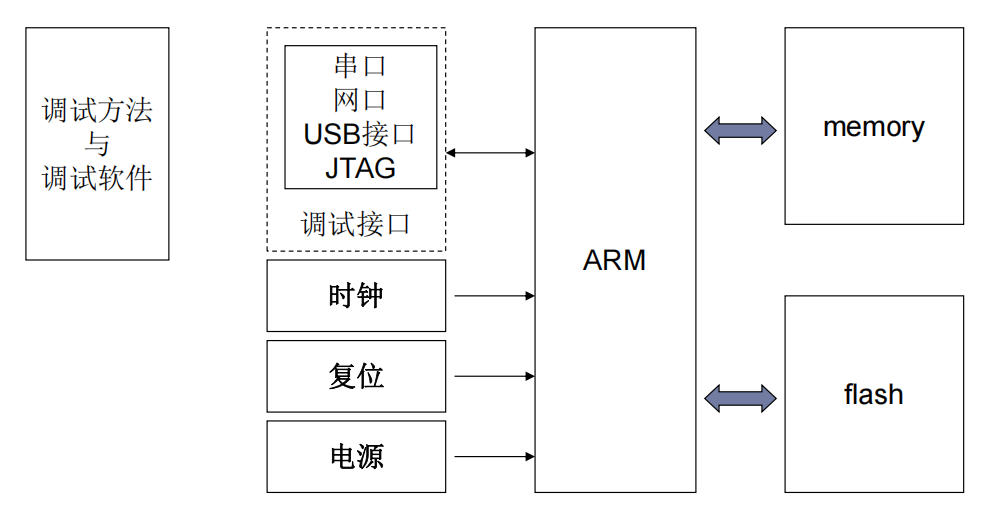

7**、ARM 最小系统 & 存储芯片**

(1)最小系统

定义: 让 CPU 正常启动、运行的最少硬件电路

**核心组成:**电源、时钟、复位、RAM(运行内存)、Flash(程序存储)、下载 / 调试电路(JTAG/SWD/ 串口)、CPU

(2)存储芯片

- NOR Flash

- 支持字节寻址,可直接在芯片内运行代码(XIP)eXecute In Place,代码直接在 Flash 中执行

- 有独立地址总线 + 数据总线

- NAND Flash

- 不支持字节寻址(无法被寻址),按 数据块(512Byte / 块)读写

- 容量大、成本低,不能直接运行代码,需加载到内存执行

(3)常用芯片对应架构

- imx6ull → Cortex-A7 → armv7-a 指令集

- s3c2440 → ARM920T → armv4 指令集

8、ARM 7 种工作模式(ARM32)

-

用户模式(User Mode,USR):

-

普通应用程序运行模式,权限最低

-

只能访问受限资源,不能直接操作硬件或系统关键寄存器。

-

不能执行特权指令。

-

-

快速中断模式(FIQ):

-

用于处理高优先级、快速响应的中断。

-

有专用寄存器,切换速度快,适合实时控制。

-

-

普通中断模式(IRQ):

-

用于处理一般中断请求。

-

比 FIQ 优先级低,寄存器资源有限。

-

-

管理模式(Supervisor Mode,SVC):

-

系统上电默认模式、系统调用、保护模式

-

操作系统或内核代码运行的模式,权限高。

-

可以访问所有资源,处理系统调用。

-

当复位或软中断指令执行时将会进入该模式

-

-

中止模式(Abort Mode,ABT):

- 地址访问异常(内存错误)触发

- 进入该模式后可进行异常处理。

-

未定义指令模式(Undefined Mode,UND):

- 执行 CPU 不识别(未定义)的指令触发

- 进入该模式后可进行异常处理。

-

系统模式(System Mode,SYS):

- 权限最高,和用户模式共用寄存器,用于操作系统内核

- 可访问所有资源

除用户模式外,其余 6 种均为特权模式,可自由切换模式、操作硬件

9、异常向量表 & 异常处理

(1)异常向量表

- 本质:一段固定地址的数组 / 代码段

- 功能:存放跳转到对应异常处理函数的指令

- 地址固定:CPU 触发异常后,自动跳转到对应向量地址

(2)异常触发时(CPU 自动执行)

- 拷贝 CPSR → SPSR_<异常模式>

- 修改 CPSR:切换为 ARM 态、切换到对应异常模式、 设置中断禁止位禁止相应中断 (可选)

- 保存返回地址 → LR_<异常模式>

- 设置 PC = 异常向量地址(跳转到处理函数)

(3)异常返回时(手动执行)

- 从 SPSR_<模式> 恢复 CPSR

- 从 LR_<模式> 恢复 PC

- 以上操作只能在 ARM 状态执行,Thumb 状态不支持

10 、ARM 异常类型(完整答案)

- 复位异常(Reset):CPU 上电 / 复位触发(最高优先级)

- 未定义指令异常(Undefined Instruction)

- 软件中断异常(SWI):用户态调用内核功能

- 指令预取中止异常:取指令失败

- 数据访问中止异常:读写数据地址错误

- 普通中断请求(IRQ)

- 快速中断请求(FIQ)

11、移位操作(ARM 指令)

-

算术移位(有符号数用)

- ASL 算术左移 高位丢弃,低位补 0(和 LSL 完全一样)

- ASR 算术右移 低位丢弃,高位补符号位(正 0、负 1)

-

逻辑移位(无符号数用)

- LSL 逻辑左移 高位丢弃,低位补 0

- LSR 逻辑右移 低位丢弃,高位补 0

-

循环移位(循环绕回)

- ROL 循环左移 移出的最高位 ,补到最低位

- ROR 循环右移 移出的最低位 ,补到最高位