4.4.5 FAN

尽管PODEM将决策从门的数量降低到了primary inputs的数量,但是仍然有些缺点:

- 需要很多多余的decisions

- 每次的只集中于一个目标,缺乏全局性

这就引出这一节的FAN (Fanout-Oriented TG)算法,拓展了PODEM同时克服了以上的缺点。

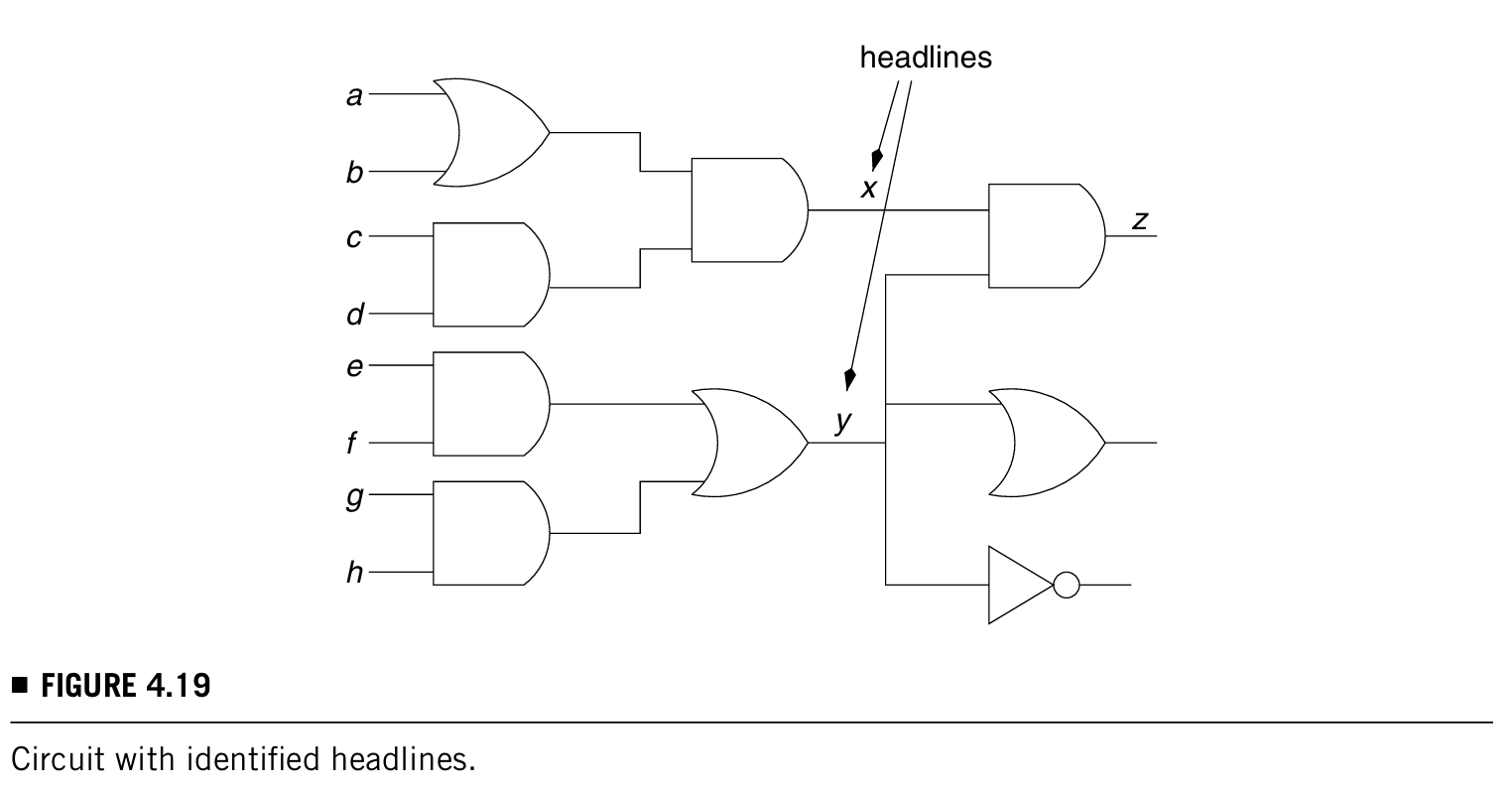

针对PODEM的第一个缺点。 为了减少 decision点,FAN算法的方法就是识别出电路中的headlines,也就是fanout-free区域的输出信号们。以下图为例:

headlines就是x和y两个输出信号。如果目标是让z = 1

- PODEM算法:需要在primary inputs做很多decisions------a = 1, c = 1, d = 1, e = 1, f = 1

- FAN算法:只需要做2个decisions------x = 1 and y = 1

可见FAN的decisions少很多,而且如果涉及到backtrack,FAN需要翻转的节点也少很多。

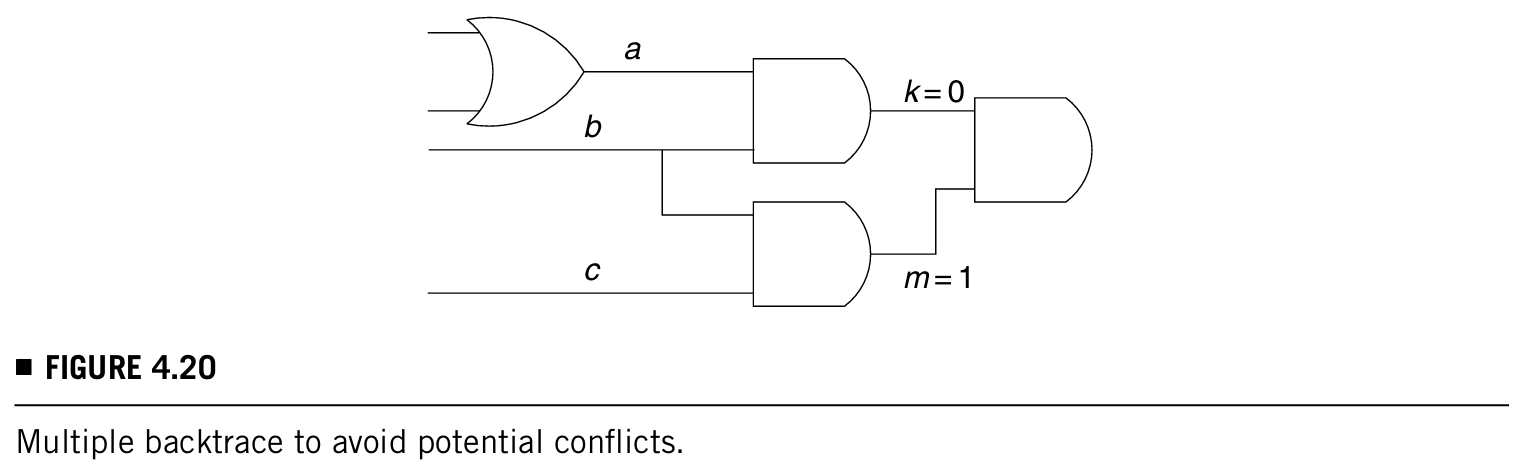

**针对PODEM的第二个缺点。**FAN算法可以同时关注多个目标,以下图例子说明:

同时关注多个目标就可以使backtrace更简便。比如要让k = 0,那么用PODEM就势必要试一下b = 0,但是这个就和m = 1冲突了;如果用FAN,就会考虑多个目标,回溯会评估各个节点,选择最好的一条路,这里就会选a = 0而不是b = 0。

4.4.6 Static Logic Implications(静态逻辑推论)

逻辑推论能捕捉到每个被赋予的逻辑值在电路中带来的影响,它在ATPG中非常有用,可以做出更好的决策,减少backtrack的次数。过去几十年,逻辑推论在测试相关领域展现了它的影响力,包括:

- test-pattern-generation

- logic and fault simulation

- fault diagnosis

- logic verification

- logic optimization

- untestable fault identification

理解逻辑推论需要了解下面的三种术语:

-

N,v,t\]:Assign logic value v to gate N in time frame t.在组合逻辑电路里面t = 0,就可以不出现t,表达式就变成了\[N,v

-

N,v,t1\]→\[M,w,t2\]:这意思够明显了,不说了

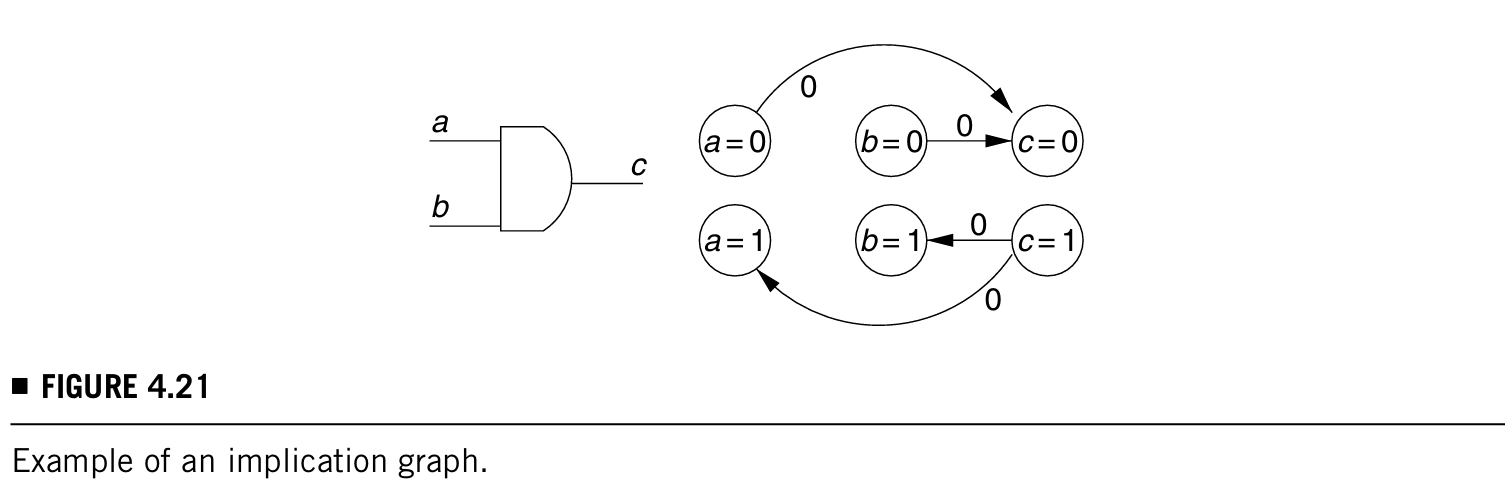

下面用一个与门和一个推论图讲一个例子:

图中有三个信号a、b、c,所以右边推论图有6个节点,例如c = 1可以推出b = 1和a = 1。

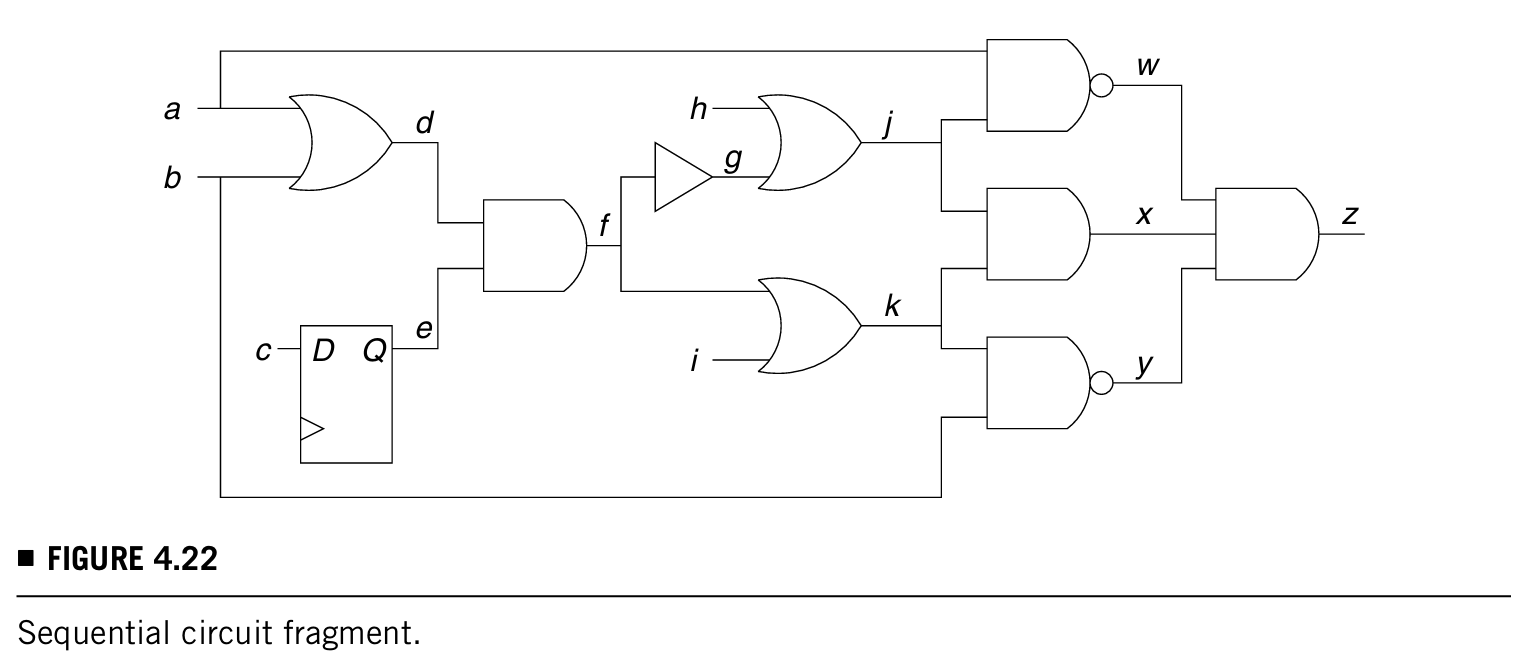

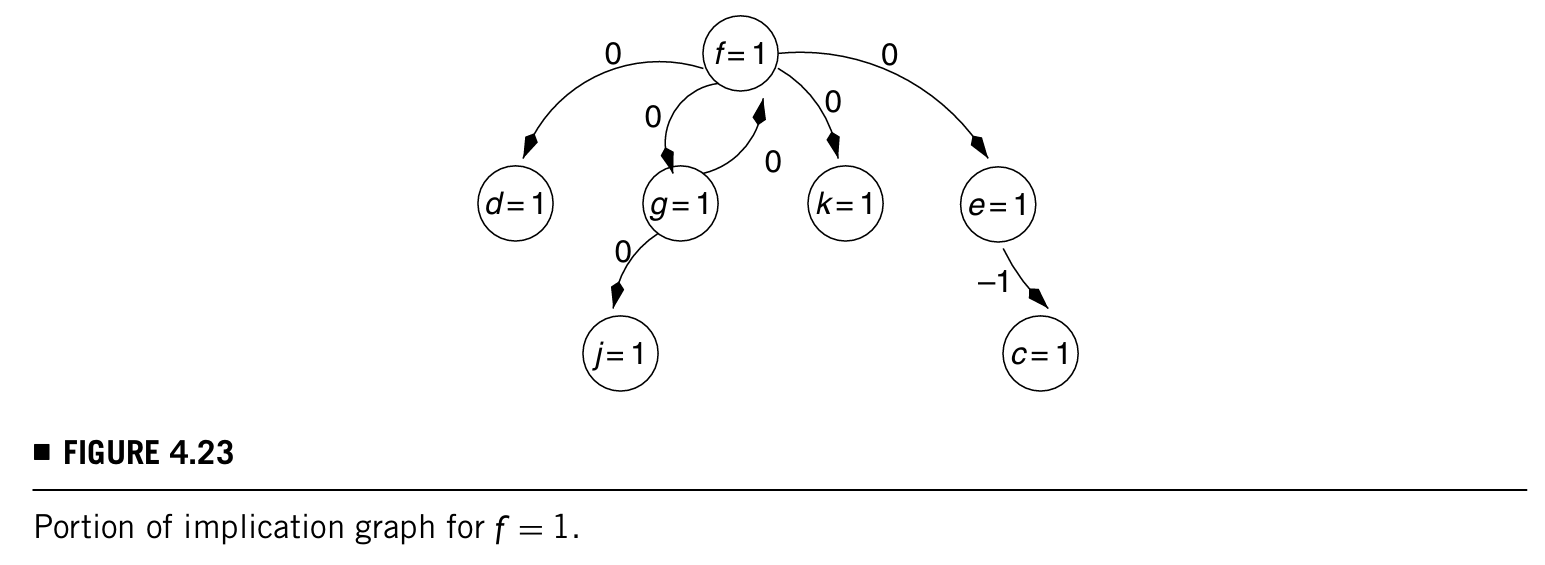

下图这个例子会更进一步解释direct,indirect和extended回推,要知道静态逻辑推论是既适用于组合逻辑电路也适用于时序逻辑电路的,这个例子给出的是一个时序逻辑电路片段,考虑f = 1:

- Direct implications:下图展示的就是direct implications for f = 1的推论图,这个图中就是显示的f = 1的推论集为Impl[f = 1] = {(f,1,0),(d,1,0),(e,1,0),(g,1,0),(k,1,0),(j,1,0),(c,1,−1)}

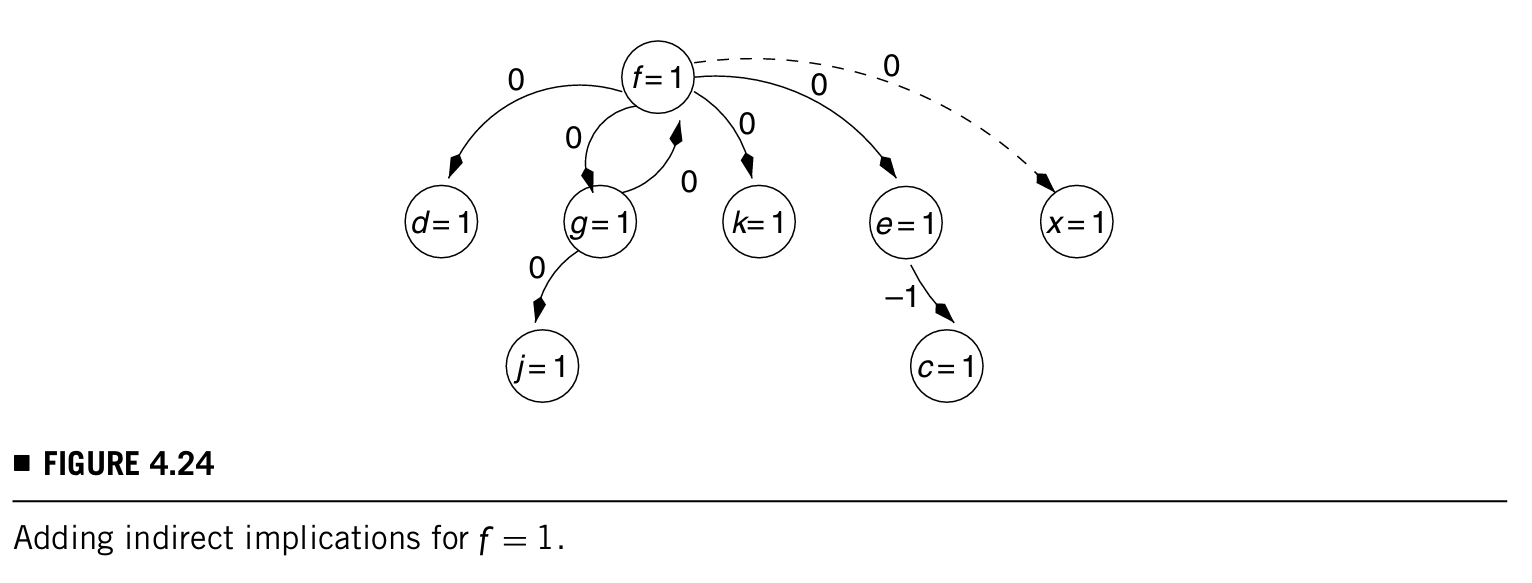

- Indirect implications:举个例子,j = 1和k = 1都单独输入x,如果他们一起都是这个值就会导致x = 1,所以间接的f = 1就能推出x = 1,这就是f = 1的一个间接的推论,这是能够通过逻辑仿真得到的(这个例子里面如果加入了f = 1的条件,逻辑仿真过后就可以得到x = 1),那么推论图就可以变成下面这样:

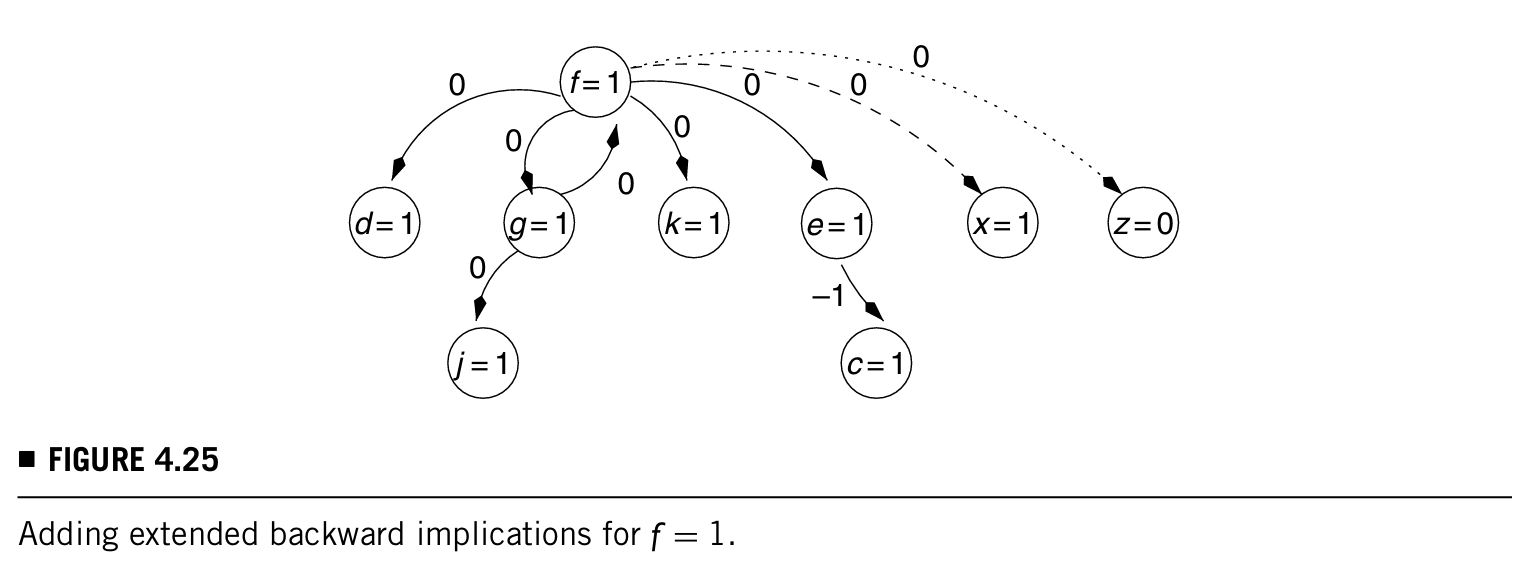

- Extended backward (EB) implications扩展逆向推论:从f = 1能推出d = 1,但是a和b的值是unjustified,所以要模拟两个子集的计算impl[a = 1]和impl[b = 1],impl[a = 1]能推出(w,0,0)和(z,0,0),impl[b = 1]能推出(y,0,0)和(z,0,0),他们的共同点是都能推出(z,0,0),所以推论图又加一个分支:

4.4.7 Dynamic Logic Implications(动态逻辑推论)

静态推论是每次对整个电路进行计算,动态逻辑推论是在ATPG的流程中发生的。

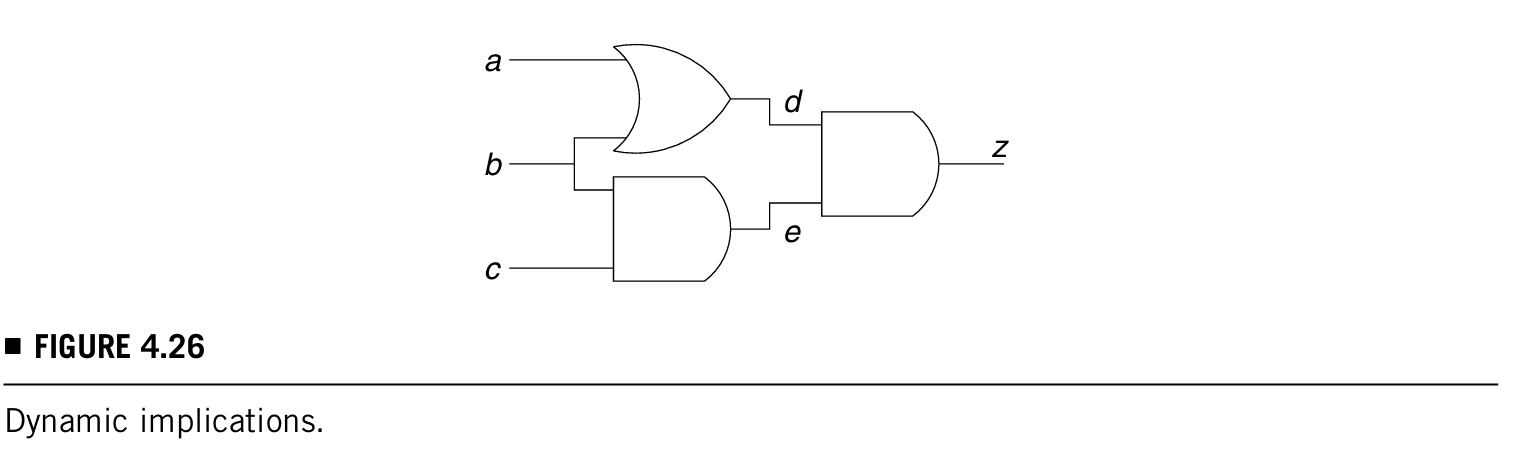

还是,下图这个例子会更进一步解释动态逻辑推论中的direct,indirect和extended回推:

假设c = 1已经定好了,如果让z = 0,就得d和e都是0,让d = 0需要{a = 0,b = 0},让e = 0需要{b = 0},所以综合下来就是让z = 0已知了c = 1就得要求b = 0。

后面的就拓展阅读吧,实在读不动了/(ㄒoㄒ)/~~

4.5 DESIGNING A SEQUENTIAL ATPG

4.5.1 Time Frame Expansion(时间框架扩展)

时序逻辑电路的测试生成和组合逻辑电路有着极大的相似,但是一个向量一般是检查不出来fault的,因为这在时序逻辑电路中需要某些flip-flop保持在某一个特定的值。

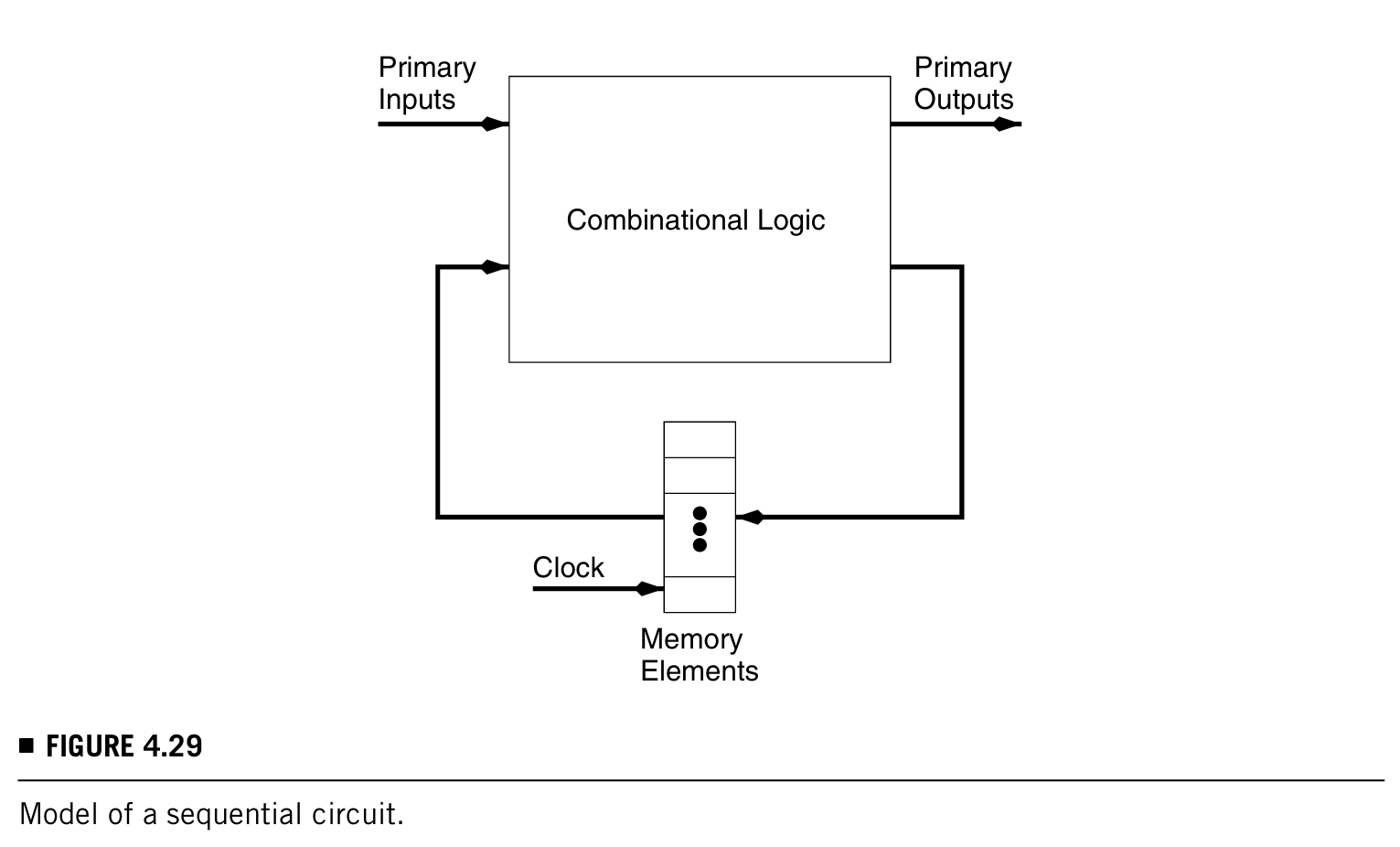

时序逻辑电路通用的一个模型就如下图所示(之前的章节应该也出现过),其中flip-flops组成图中的memory/state elements,图中他们都接收同一个时钟信号:

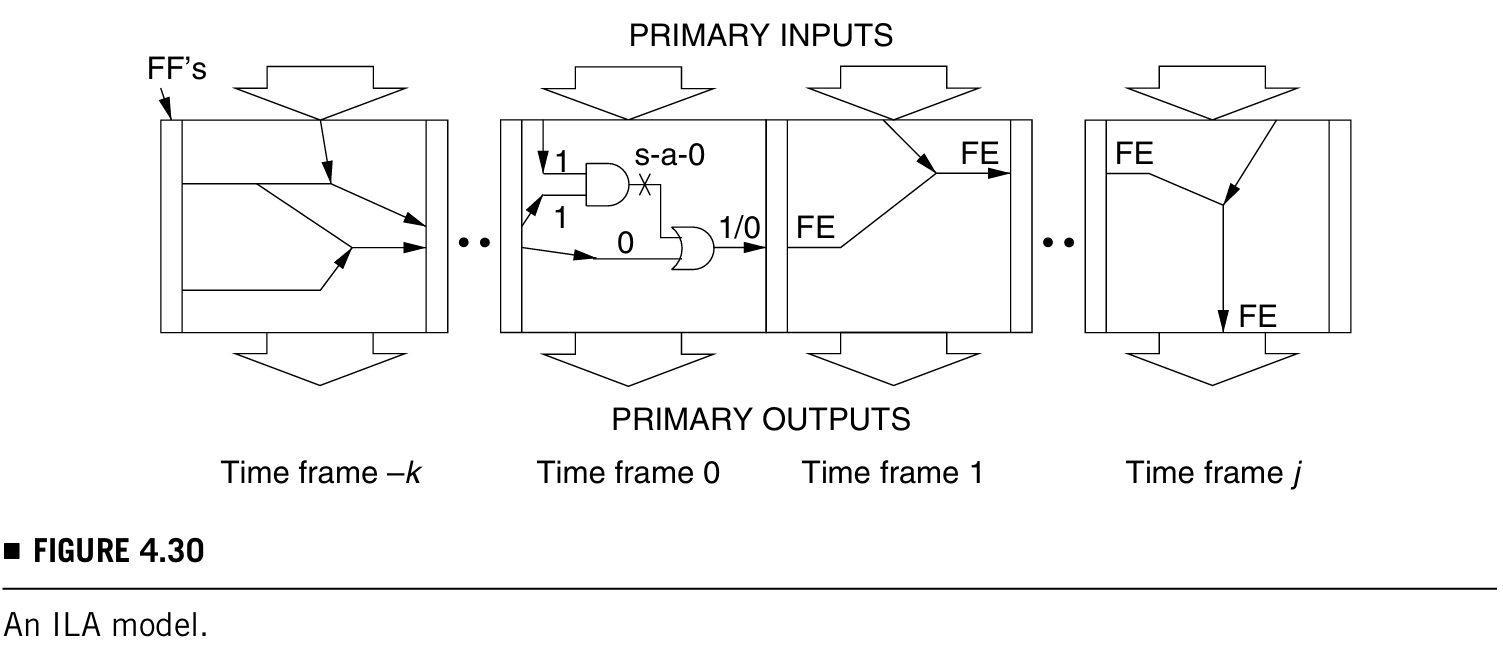

下图展示的是这个时序逻辑电路模型被展开成一系列的time frames,也叫做迭代逻辑阵列iterative logic array(ILA):

对于每一个time frame,前面一个time frame输入进来的信号叫伪原始输入pseudo primary inputs ,它传给下一个time frame的输出叫伪原始输出pseudo primary outputs。注意在展开的每个time frame中,target fault都存在。

后面讲了一些有关ATPG激发故障和传播故障需要做ATPG search的流程,有需要可以原文看。

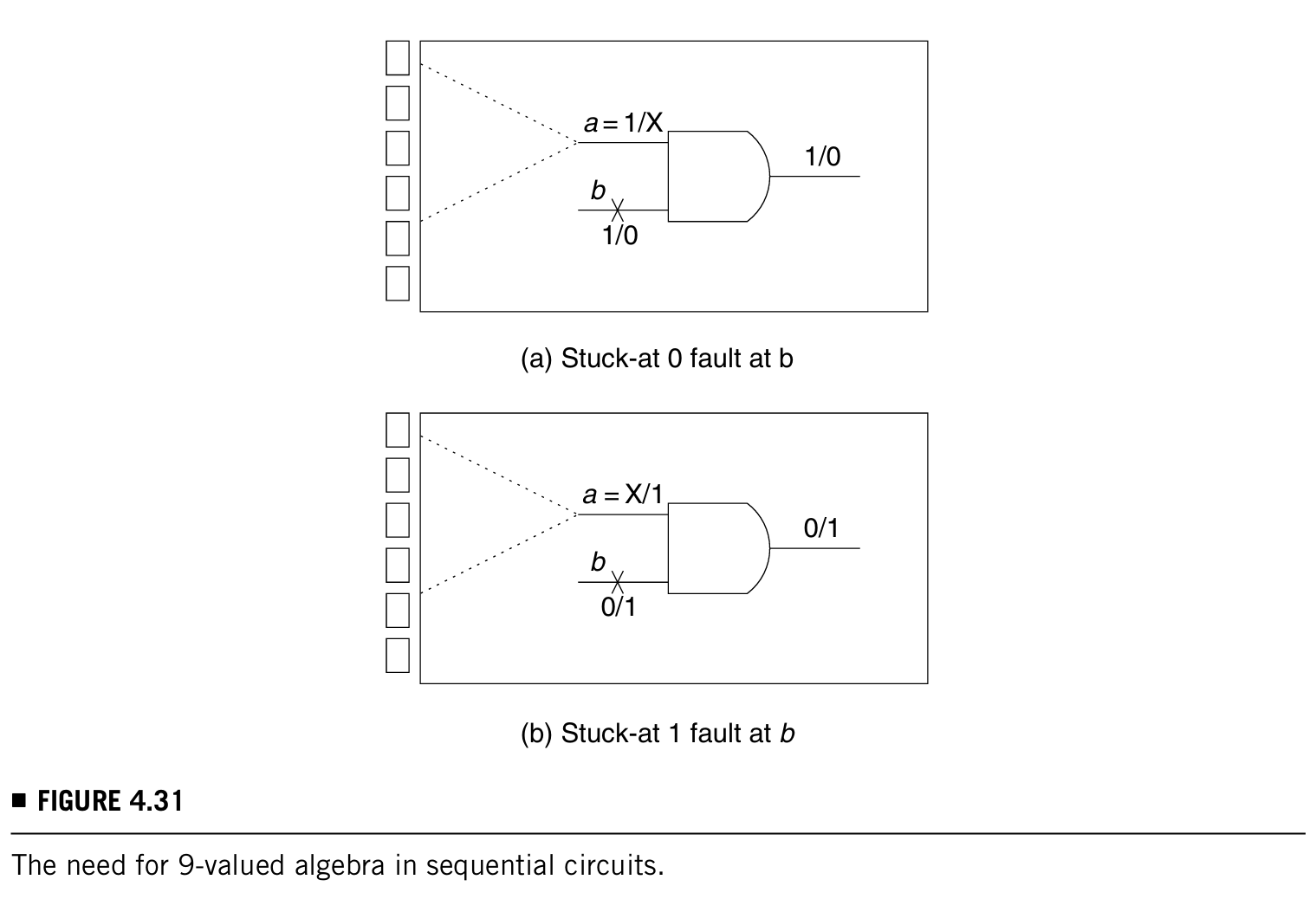

4.5.2 5-Valued Algebra Is Insufficient(五值代数是不够的)

五值参考4.4,0、1、X、D(0/1)和D'(1/0),九值应该就是加上了1/X、X/1、0/X和X/0。举了个例子证明了为啥需要用九值逻辑做时序逻辑电路的ATPG,就是因为如果没有九值就会误杀很多可能性,具体见原文讲解的下图吧:

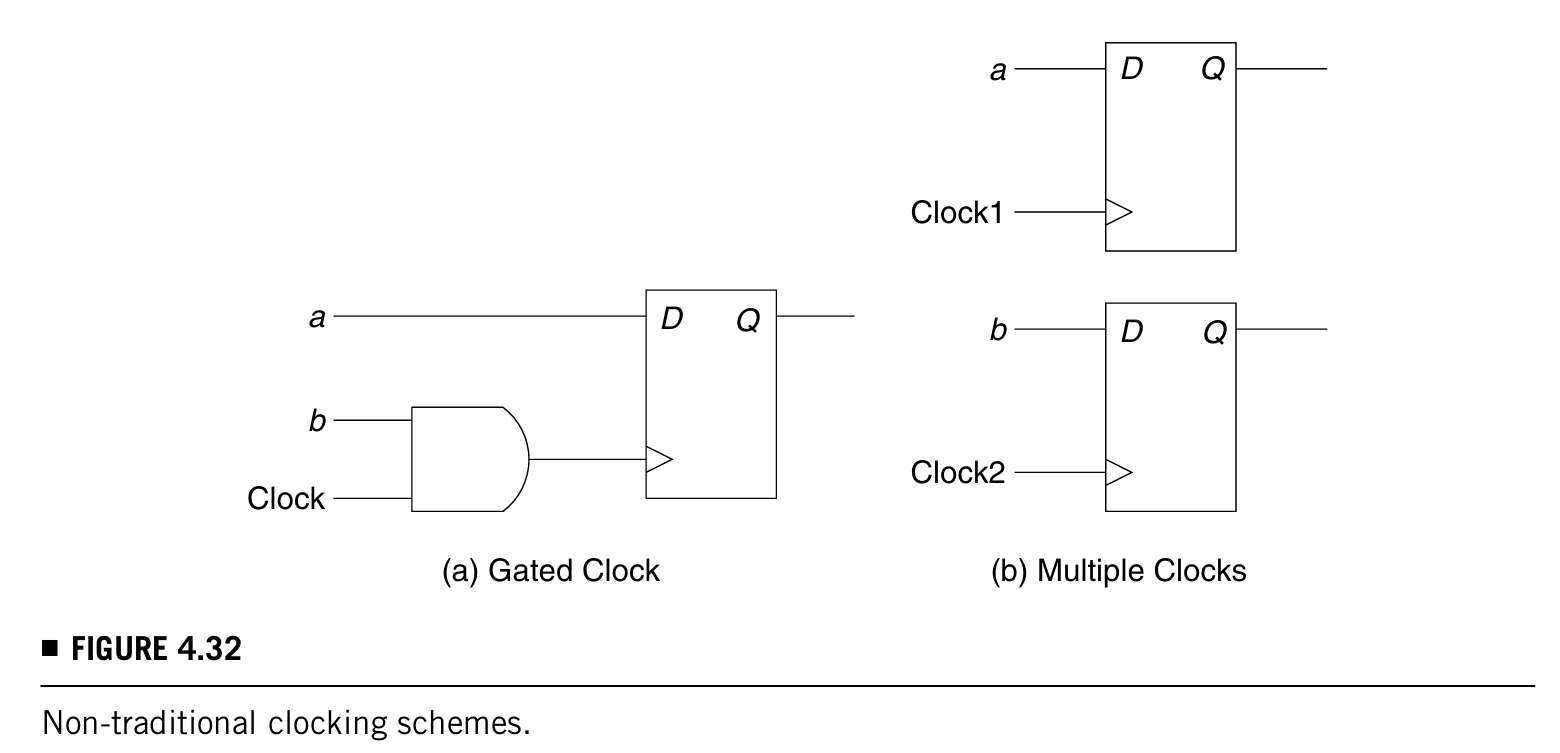

4.5.3 Gated Clocks and Multiple Clocks(门控时钟和多时钟)

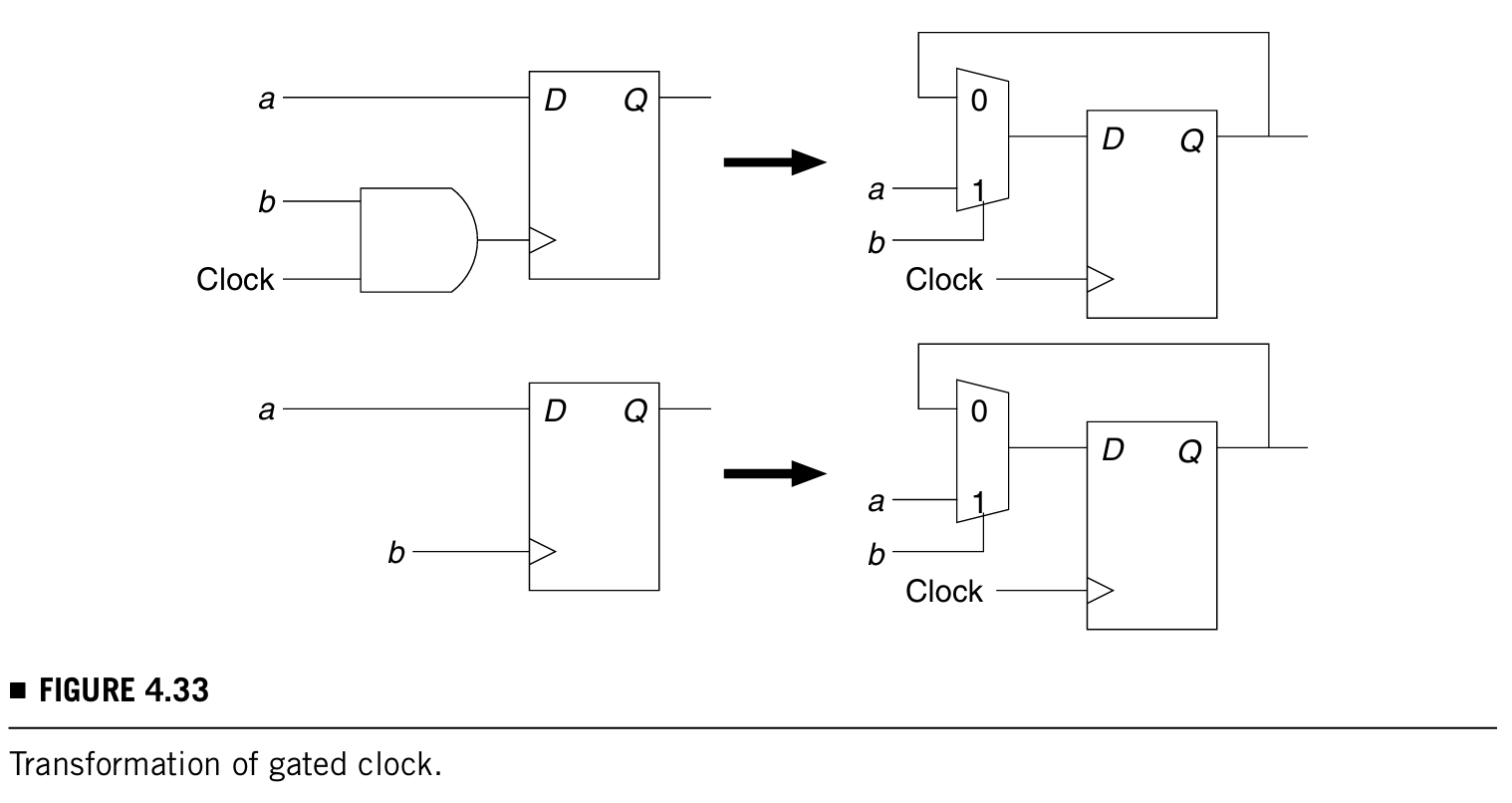

前面都是假设电路中只有一个时钟,但是现在的电路基本都是门控时钟和多时钟,如下图a和b:

- 门控时钟:为了节省功耗,并不是每一个时钟来临每个开关都要翻转

- 多时钟:分不同的时钟域,可以优化每个域的性能、功耗和设计

如果有门控时钟或者多时钟的电路是没法修改的,那么ATPG就得需要一些预处理的电路建模工作,让ATPG更加简单,如今大多数EDA工具都有这个功能。而且这比专门设计一种有门控时钟和多时钟的ATPG算法更加简单。

例如下图的两种情况,将门控时钟电路插入一个multiplexer,上半部分和下半部分的图都是右边微调过的电路和左边原始设计功能相同的:

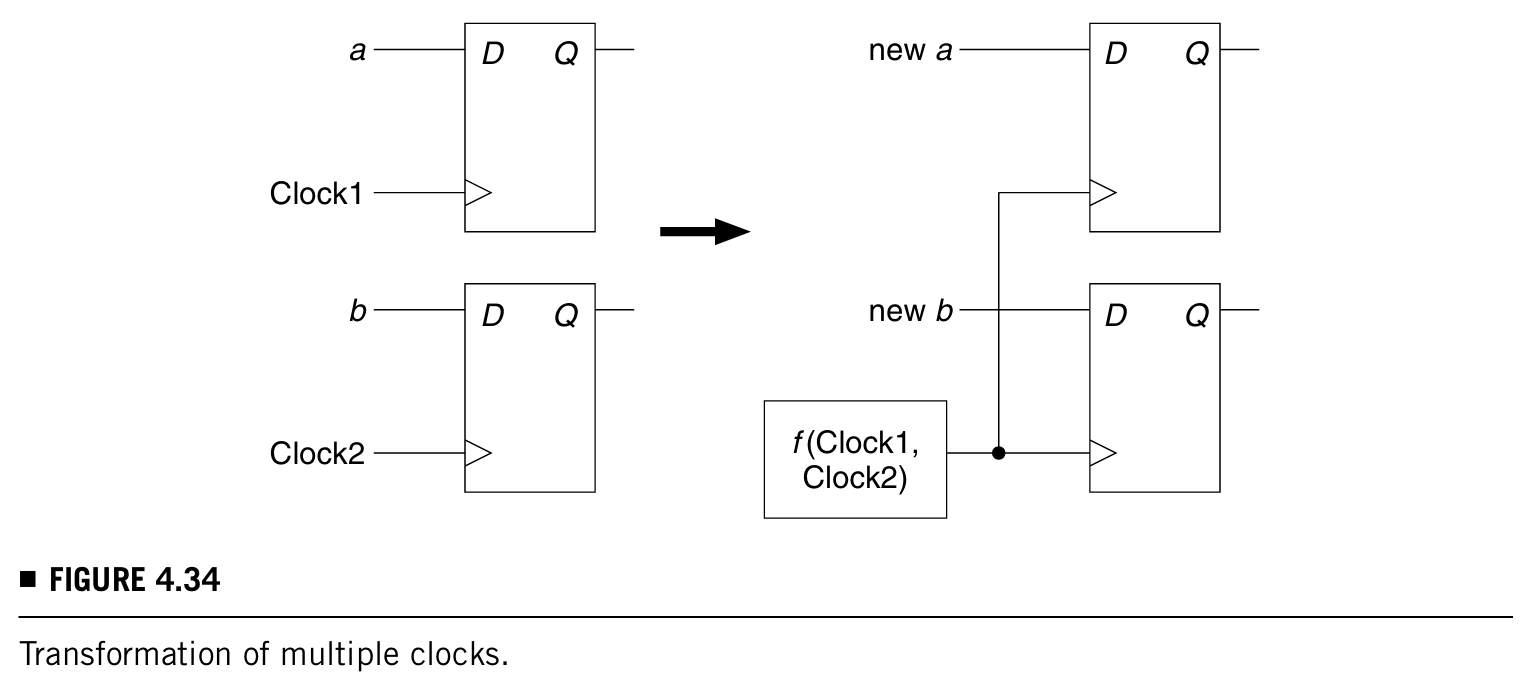

对于多时钟电路也可以进行如下修改:

上面的修改做完,就可以使用stuck-at ATPG algorithms (combinational or sequential)了,而且需要注意的是,上面的修改可能对于stuck-at故障之外的其他故障没啥用。

对于多时钟的电路,除了上面的MUX-based modifications,还有两种方法:

- one-hot:有比较高的故障覆盖率,但是test sets很大。

- staggered clocking:故障覆盖率稍微低,但是通过circuit expansion可以使用组合逻辑电路的ATPG。Sequential ATPG可能也能用,但是应该是需要很长的执行时间。