本文档聚焦 Calibre nmLVS 的核心进阶功能,包括器件过滤 、网络分类与处理 、无效端口 / 引脚 / 网络识别 、逻辑门自动识别 、引脚交换 及器件属性追踪,这些功能旨在优化 LVS 对比效率、处理电路层级复杂性并提升结果准确性。

一、器件过滤(Device Filtering)

Calibre nmLVS 允许在 LVS 运行期间过滤掉无需分析的器件 ,该操作在 LVS 对比的器件归约之后 执行,由 LVS Filter 系列规范语句控制。对于将单元视为器件过滤的场景,LVS Box 语句十分实用 ------ 通过在 LVS Filter 中指定 LVS Box 单元名称,可将其作为器件过滤。

1.1 未使用 MOS 晶体管过滤

Calibre nmLVS 可在内部从源电路和版图电路中过滤未使用的 MOS 晶体管。过滤仅针对正确构造的 MOS 晶体管执行。

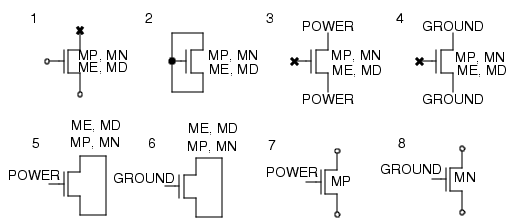

LVS Filter Unused MOS 规格语句控制未使用 MOS 晶体管的过滤功能。当指定为 YES 时,以下配置的晶体管将被过滤掉。具体而言,这些是组件类型为 MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 或 LVS Device Type 语句中指定的等效器件的实例,且至少具有三个标准名称的引脚(如表 1所示)。

-

MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 及等效晶体管,其源极或漏极引脚悬空。

-

MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDD 及等效晶体管,其源极、漏极和栅极引脚短接在一起。

-

MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 及等效晶体管,其栅极引脚悬空,且源极和漏极引脚连接至同一电源网络。

-

MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 及等效晶体管,其栅极引脚悬空,且源极和漏极引脚连接至同一地网络。

-

MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 及等效晶体管,其源极与漏极短接,且栅极引脚连接至电源网络。

-

MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 及等效晶体管,其源极与漏极短接,且栅极连接至地网络。

-

MP、LDDP 及等效晶体管,其栅极引脚连接至电源网络。

-

MN、LDDN 及等效晶体管,其栅极引脚连接至地网络。

控制语句

LVS Filter Unused MOS YES/NO(默认行为由工具定义,需显式启用过滤)

过滤条件

仅对正确配置的 MOS 晶体管 生效,即元件类型为 MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD 或 LVS Device Type 定义的等效类型,且至少具有 3 个标准引脚(G、S、D)。满足以下任一条件的晶体管会被过滤:

- 源极(S)或漏极(D)引脚浮空;

- 源极、漏极、栅极(G)引脚短接在一起;

- 栅极浮空,且源极和漏极连接到同一电源网络;

- 栅极浮空,且源极和漏极连接到同一地网络;

- 源极与漏极短接,且栅极连接到电源网络;

- 源极与漏极短接,且栅极连接到地网络;

MP、LDDP及其等效器件的栅极连接到电源网络;MN、LDDN及其等效器件的栅极连接到地网络。

1.2 未使用双极型晶体管过滤

控制语句

LVS Filter Unused Bipolar YES/NO

过滤条件

仅对正确配置的双极型晶体管 生效,即元件类型为 Q 或 LVS Device Type 定义的等效类型,且至少具有 3 个标准引脚(C、B、E)。满足以下条件的晶体管会被过滤:

- 基极(B)与发射极(E)短接。

二、网络分类与处理(Nets)

LVS 中网络按功能和连接特性分为多种类型,处理逻辑和报告方式各不相同,核心类型包括电源 / 地网络 、隔离网络 、直通网络 、馈通网络。

2.1 电源与地网络(Power and Ground Nets)

定义

满足以下任一条件的网络被视为电源 / 地网络:

-

网络名称出现在

LVS Power Name/LVS Ground Name语句中; -

网络连接到名称匹配

LVS Power Name/LVS Ground Name的端口,且同一设计中无其他网络使用该名称。

用途

用于逻辑门识别 、未使用 MOS 晶体管过滤 等功能,单个设计中允许存在多个电源 / 地网络。

2.2 隔离网络(Isolated Nets)

定义

未连接到任何实例或 LVS 操作单元的端口的网络,版图中的隔离网络本质是 "裸线"。

处理逻辑

-

若隔离网络在两个对比电路中均无用户指定名称,不会产生不一致项;

-

扁平化 LVS(

calibre -lvs无-hier/-flatten)会保留版图隔离图形并对比,层级 LVS(LVS-H)通过*.CALIBRE ISOLATED NETS语句在网表中表示; -

顶层单元中名称匹配源网表 的命名隔离网络不会被删除 ,参与 LVS 对比;底层单元中此类网络被删除时,会在报告中标记为

Matching Deleted Isolated Layout Nets。

报告控制

可通过 LVS Report Option I 禁用所有隔离网络报告。

2.3 直通网络(Passthrough Nets)

定义

仅连接到端口(可能包含一个引脚),无其他连接的网络,常见于版图但极少出现在原理图中。

处理逻辑

-

默认行为:对比时忽略直通网络(类似隔离网络),被删除的直通网络会在报告中统计;

-

层级差异 :底层单元的直通网络若未命名,会被归类为无效端口并删除;若名称匹配源网表,则按直通网络报告;

-

报告选项:

-

LVS REPORT OPTION SP:报告源网表中的直通网络及对应端口; -

LVS REPORT OPTION SPE:若源网表存在未匹配的直通网络,将对比状态设为INCORRECT; -

LVS REPORT OPTION LPE:若版图存在未匹配的直通网络,将对比状态设为INCORRECT。

-

2.4 馈通网络(Feedthrough Nets)

定义

连接单元的两个引脚,从而将引脚上方的两个网络短接的网络(又称 "深度短路")。

处理场景

主要用于电路提取阶段,而非 LVS 对比阶段。

三、无效端口、引脚与网络(Trivial Ports, Pins, and Nets)

3.1 定义

-

无效网络 :仅连接到向上层级的端口 或向下层级的引脚的网络;

-

无效端口 :仅连接到无效网络的端口;

-

无效引脚 :仅连接到无效网络 的引脚,与无效端口的区别是引脚在父单元外部有连接。

3.2 处理逻辑

-

未命名的无效端口 / 引脚 :对比时自动忽略,不会产生不一致项;

-

命名匹配的无效端口 / 引脚 :作为初始对应点参与对比,不会被删除;

-

顶层或名称匹配的无效网络 / 端口 :按直通网络的规则处理;

-

底层命名匹配的无效端口 :默认不会被忽略 ,可通过

LVS Ignore Trivial Named Ports YES启用忽略。

3.3 报告控制

可通过 LVS Report Trivial Ports YES 在电路提取阶段报告版图中的无效端口。

四、逻辑门识别(Logic Gate Recognition)

Calibre nmLVS 可自动识别晶体管级电路中的逻辑门 和半门 (上拉 / 下拉结构、串并联逻辑门),通过虚拟门实例内部表示这些结构,并在晶体管级或门级进行对比,提升对比效率和结果可读性。

4.1 支持的门类型

| 门类型 | 构成器件类型 | 示例 |

|---|---|---|

| 常规 CMOS 门 | MP(上拉)+ MN(下拉) | INV、NANDn、NORn |

| LDD CMOS 门 | LDDP(上拉)+ LDDN(下拉) | AOI、OAI |

| 常规 NMOS 门 | MD(上拉)+ ME(下拉) | SDW、SUP |

| LDD NMOS 门 | LDDD(上拉)+ LDDE(下拉) | SPDW、SPUP |

| 串并联结构 | M、LDD 或等效类型 | SMPn、SPMP(expression) |

4.2 控制语句与关键选项

核心控制语句

LVS Recognize Gates YES/NO/SIMPLE/CELL LIST

YES(默认):识别所有逻辑门;NO:禁用逻辑门识别;SIMPLE:禁止形成复杂 AOI/OAI 门,仅形成 SUP、SDW 等简单结构;CELL LIST:通过LVS Cell List指定仅对特定单元启用门识别。

子选项

MIX SUBTYPES:允许同一半门(如上拉 / 下拉部分)中混合不同晶体管子类型;WITHIN TOLERANCE:启用基于容差的门识别,需配合ALL/SIMPLE使用。

4.3 关键规则

-

器件要求 :仅正确配置的 MOS 晶体管可形成逻辑门(至少 3 个标准引脚 G、S、D);

-

可交换性 :逻辑门的等效输入引脚、并联器件组的顺序可交换(如 NAND 门的两个输入引脚),具体可交换性随门类型定义;

-

X+ 晶体管的影响 :子类型以

X开头的 MOS 晶体管(如M(XP))默认不参与逻辑门形成 ,可通过LVS Recognize Gates XALSO禁用此特殊处理; -

逻辑注入的影响 :默认启用的逻辑注入(LVS-H)会使注入的逻辑结构(如

_inv)不参与门识别,若注入结构未形成,则可参与。

4.4 识别例外情况

-

连接到衬底引脚等非源 / 漏引脚的网络,不会被视为逻辑门的内部网络;

-

作为初始对应点的网络,不会被视为逻辑门的内部网络;

-

当多个晶体管同等符合门形成条件时,工具仅形成半门,避免子类型和属性值导致的虚假不一致。

五、引脚交换(Pin Swapping)

LVS 对比允许版图实例的逻辑等效引脚连接顺序与源网表对应实例不同,即引脚交换,可大幅减少因引脚顺序差异导致的虚假不一致。

5.1 默认引脚交换规则

工具默认将以下引脚视为逻辑等效(可交换):

- 同名引脚:始终可交换;

- 常规 MOS 晶体管 :源极(S)和漏极(D)可交换(

MN、MP、ME、MD、M及等效类型); - 电阻器 :所有引脚可交换(

R及等效类型); - 电容器 :仅当

LVS All Capacitor Pins Swappable YES时,POS 和 NEG 引脚可交换。

控制语句

LVS Builtin Device Pin Swap NO:禁用除电容器外的所有默认引脚交换规则。

5.2 规则文件中的引脚交换列表

通过在 Device 语句中定义引脚交换列表,可指定用户定义器件的可交换引脚:

- 显式定义 :将可交换引脚用括号括起,如

DEV C cap1 poly m1 (POS NEG); - 隐式定义 :同一层的引脚默认可交换,如

DEV F seed m1(p1) m1(p2) poly(p3)中p1和p2可交换。

应用逻辑

工具按以下优先级为实例应用引脚交换规则:

-

匹配元件类型、子类型、引脚数量和名称 的

Device语句; -

匹配元件类型、引脚数量和名称 且无子类型 的

Device语句; -

若实例无子类型,匹配元件类型、引脚数量和名称 的所有

Device语句,且这些语句的引脚交换规则完全一致。

5.3 SPICE 作为版图系统时的处理

当版图为 SPICE 网表(Layout System SPICE)或层级 LVS 以 SPICE 为中间表示时,工具会从 Device 语句中提取引脚交换信息,适用于将用户定义器件以原始子电路形式写入 SPICE 网表的场景。

5.4 报告控制

LVS Report Pinswapped:将器件实例的引脚交换作为错误在 LVS 报告中呈现。

六、器件属性追踪(Device Property Tracing)

Calibre nmLVS 可对比(追踪)版图实例与源网表对应实例的选定属性值 ,当值不同时报告不一致项,由 Trace Property 规范语句控制追踪规则。

6.1 内置属性分类

工具将部分属性名称识别为内置属性,用于器件归约时的有效值计算(如串并联归约),包括:

- 几何属性:

A(面积)、AD(漏极面积)、AS(源极面积)、P(周长)、PD(漏极周长)、PS(源极周长)、L(长度)、W(宽度); - 电气属性:

C(电容)、R(电阻)。

关键注意事项

- 版图和源网表均遵循此命名约定,即使提取的 SPICE 网表使用非标准名称(如二极管面积为

AREA),工具也会自动映射为内置属性名(A); - 可通过

Trace Property为源网表指定非默认属性名,如TRACE PROPERTY MP(X) WIDTH W 0表示源网表中MP(X)器件的宽度属性为WIDTH,版图中为W。

6.2 W/L 伙伴属性(W/L Partner Properties)

W(宽度)和 L(长度)被称为伙伴属性,因为计算其中一个的有效值可能需要另一个的值(如并联 MOS 晶体管的有效宽度计算需考虑长度是否一致)。

自动读取规则

当满足以下条件时,工具会自动读取伙伴属性 ,即使未在 Trace Property 中显式指定:

- 对该器件类型启用了相关归约(如并联 MOS 归约);

- 伙伴属性是计算目标属性有效值必需的;

- 目标属性出现在

Trace Property或归约容差语句中。

控制语句

LVS Spice Strict WL YES:仅将精确匹配 W/L 的参数视为宽度 / 长度属性(默认匹配以 W/L 开头的参数)。

6.3 归约后的器件计数对比

通过追踪 **M 属性 **(乘数因子),可对比归约后器件对应的原始器件数量:

- 内置 SPICE 元件:

M属性为M参数值,默认 1; - 原始 /

LVS Box子电路:M属性始终为 1; - 归约时可通过

LVS Reduce定义M的有效值计算规则,如并联归约时M=SUM(M)(累加所有参与归约器件的M值)。

配置示例

// 定义 M 属性

DEVICE MP PGATE PGATE PSD PSD NWELL [

PROPERTY M

M=1

]

// 并联归约时累加 M 值

LVS REDUCE MP PARALLEL [

EFFECTIVE M

M=SUM(M)

]

// 追踪 M 属性

TRACE PROPERTY MP M M 0关键语句汇总

| 功能分类 | 核心控制语句 | 作用 |

|---|---|---|

| 器件过滤 | LVS Filter Unused MOS YES |

启用未使用 MOS 晶体管过滤 |

LVS Filter Unused Bipolar YES |

启用未使用双极型晶体管过滤 | |

| 网络处理 | LVS Report Option I |

禁用隔离网络报告 |

LVS REPORT OPTION SP/SPE/LPE |

控制直通网络报告及对比状态 | |

| 无效端口处理 | LVS Ignore Trivial Named Ports YES |

忽略底层单元中命名匹配的无效端口 |

| 逻辑门识别 | LVS Recognize Gates SIMPLE |

禁止复杂 AOI/OAI 门识别 |

LVS Recognize Gates XALSO |

允许 X+ 晶体管参与逻辑门形成 | |

| 引脚交换 | LVS Builtin Device Pin Swap NO |

禁用默认引脚交换规则 |

LVS All Capacitor Pins Swappable YES |

启用电容器引脚交换 | |

| 属性追踪 | Trace Property MP W W 0 |

追踪 MP 器件的宽度属性 |

LVS Spice Strict WL YES |

严格匹配 W/L 属性名 |