本博文主要交流设计思路,在本博客已给出相关博文约190篇,希望对初学者有用。 注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP 设计。

这里将在基于 XCZU47DR FPGA 核心的开发板上对 RoCE v2 高速传输系统进行数据吞吐量、包吞吐量及传输延迟性能测试,并对测试结果进行解读与分析。

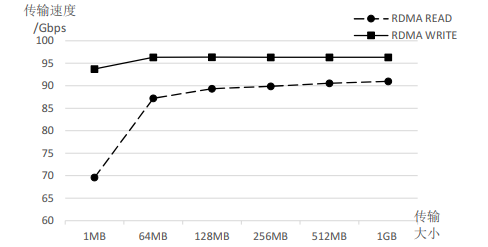

数据吞吐量是评估连续数据传输性能的核心指标,数据吞吐量越高,表明系统面临大量数据传输请求时拥有更强的数据传输能力和更高的速率。由于数据吞吐量受队列数量及队列深度影响较小,故这里使用单队列对不同长度的数据包进行数据吞吐量测试。在进行数据吞吐量测试时由于 SEND 指令为双边语义,不涉及到大量数据的传输,故数据吞吐量测试只对 READ 和 WRITE 指令进行。同时由于远程主机内存限制,进行数据吞吐量测试时的传输长度为 1MB-1GB。数据吞吐量测试结果如图 1所示。

由于 READ 和 WRITE 指令单边语义的特点,在进行数据交互时,并不需要远程主机 CPU 参与,故无法直接使用 CPU 监控的方式进行数据吞吐量测试。在进行 READ指令数据吞吐量测试时,通过在 FPGA 侧对收到的数据字节数进行统计,当收到的数据字节数等于期望的数据量是,则认为数据传输结束,以此时间来计算数据吞吐量。而对于 WRITE 指令,在 FPGA 侧进行数据字节数统计的方式并不严谨,故在远程主机上持续轮询内存数据边界,当内存边界数据与预期相同时,则认为数据传输结束,计算数据吞吐量。

图1 数据吞吐量测试结果图

测试结果图表明,WRITE 指令数据吞吐量一直大于 READ 指令数据吞吐量,原因有以下两点。第一个原因是,READ 指令由远程主机响应并处理数据,其数据吞吐量与远程主机 PCIe 总线性能及 DDR 读取、寻址操作等强相关。其二是 WRITE 指令数据包在 FPGA 上组装,远程主机只负责将数据写入 DDR,而 READ 指令则需要远程主机从 DDR 中读取数据,并组装数据包后在发送给 FPGA。以上两点原因共同作用导致 READ 指令数据吞吐量小于 WRITE 指令数据吞吐量。

当传输长度从 1MB 向 1GB 递增时,READ 指令与 WRITE 指令的传输速度均呈上升趋势,持续逼近理论速率极限,并在传输长度大于 128 MB 后趋于稳定。上图中给出的数据吞吐量为去掉所有头部开销后,净数据的传输速率。如果包含所有头部开销,则 READ 指令数据吞吐量为 92.10 Gbps,WRITE 指令数据吞吐量为 97.49 Gbps,速率接近理论极限且大于项目要求速率 90 Gbps,可以满足项目设计需求,实现了设计目标。此外的,麦洛斯 CX455-A 网卡工作在 Ethernet 物理层模式下时,存在一定程度上的理论速率降低现象,理论极限速率约为 98.5Gbps。故本设计实现的 RoCE v2

高速传输系统数据吞吐量已逼近理论极限速率。