本文档聚焦 Calibre nmLVS 的核心功能 ------ 电路对比,详细阐述其数据流程、对比机制、关键概念(如初始对应点、组件类型、内置器件)及结果分类,是验证版图拓扑与源网表功能一致性的核心参考,对规则文件配置、对比效率优化和差异调试至关重要。

一、LVS 电路对比概述

1. 核心目标与作用

-

目标 :对比版图设计的拓扑结构 与源网表(如 SPICE) ,验证版图是否正确实现了源网表的功能意图。

-

核心动作 :建立版图与源网表中电路元素(实例、网、端口、实例引脚)的一一对应关系;若存在差异,从源正确、版图错误 和版图正确、源错误两个视角生成差异报告。

2. 数据流程

LVS 支持单步流程 和两步流程,核心输入输出如下:

(1)输入文件

Calibre nmLVS 的输入包括:SVRF 规则文件、版图网表或几何数据库、以及原始网表。在层次化 LVS(LVS-H)模式下,还会使用层次化单元(hcell)对应列表,该列表可在独立文件、规则文件中指定,或在版图与原始网表的单元名称匹配时自动生成。

- 规则文件(SVRF);格式为.lvs或者按照对应fab的格式执行即可。

- 版图数据(几何数据库或提取的网表);

- 源网表(SPICE 格式);需要用户自己利用v2lvs 工具将.v网表转换为该格式。

- 分层 LVS(LVS-H)额外需要 hcell 对应列表(可在规则文件、独立文件中指定,或自动基于单元名匹配生成)。

| 输入文件 | 说明 | 格式 / 要求 |

|---|---|---|

| SVRF 规则文件 | 定义器件识别、连接规则、层映射等,是 LVS 运行的核心依据 | .lvs 或 fab 自定义格式 |

| 版图数据 | 提供电路的物理实现信息,可直接用几何数据库,也可使用已抽取的版图网表 | GDSII/OASIS(几何)或 SPICE/CDL(已抽取网表) |

| 源网表 | 来自原理图 / 设计的 "黄金网表",用于与版图网表比对 | SPICE 格式;需用 v2lvs 工具将 Verilog .v 网表转换得到 |

| hcell 对应列表(分层 LVS 专用) | 建立版图单元与原理图单元的层次映射,解决命名不一致问题 | 可在规则文件、独立文件中指定,或自动基于单元名匹配生成 |

(2)流程类型

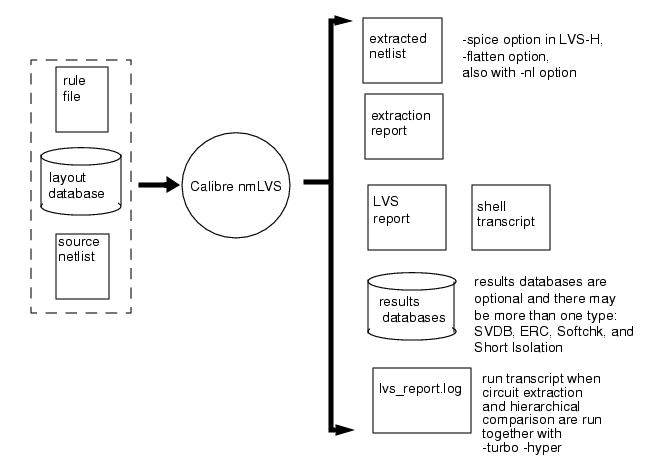

图 1 展示了在单步流程中同时执行电路提取和网表对比的 LVS 数据流程。

若运行 Calibre nmLVS-H 时指定 -spice 选项,工具会输出 SPICE 格式的版图网表及电路提取报告。以下场景也会触发该输出:

- 指定

-hier选项(但未指定-spice选项); - 版图系统为几何数据库;

- 指定了掩模 SVDB 目录(用于 Calibre RVE 中的交互式 LVS 调试)。

-flatten 选项用于提取扁平化的版图网表。

若指定运行 ERC 检查、短路隔离检查或软连接检查,LVS 会在电路提取过程中为这些检查生成 DRC 格式的结果数据库。

执行网表对比(指定 -lvs 选项)时,工具始终会生成 LVS 报告。

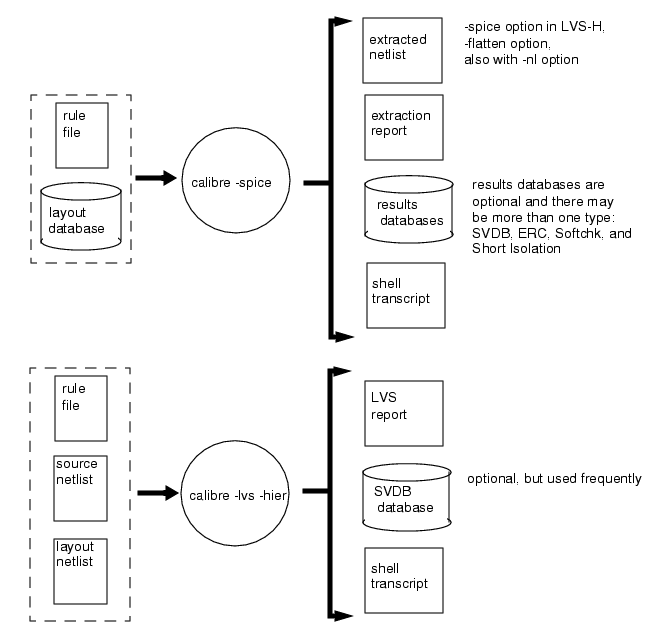

图 2 展示了在两步流程中分别执行电路提取和对比的 Calibre nmLVS-H 数据流程。

-

单步 vs 两步流程:单步流程直接完成 "版图抽取 + 网表比对";两步流程先单独抽取版图网表,再进行网表比对,更便于调试和复用。

-

v2lvs 工具 :用于将 Verilog 网表(

.v)转换为 LVS 可识别的 SPICE 网表,是数字设计流程中的关键转换步骤。 -

几何数据库 vs 已抽取网表:若使用已抽取的版图网表作为输入,可跳过器件识别步骤,直接进行网表比对,提升运行速度。

| 流程类型 | 执行逻辑 | 关键命令示例 |

|---|---|---|

| 单步流程 | 电路提取 + 网表对比一次性完成 | calibre -lvs -hier layout.gds source.spi rules |

| 两步流程 | 先执行电路提取生成版图网表,再执行网表对比 | 1. calibre -spice layout.net -hier layout.gds rules(提取)2. calibre -lvs -hier layout.net source.spi rules(对比) |

典型输入组合

-

基础 LVS 流程:SVRF 规则文件 + GDSII 版图 + SPICE 源网表

-

分层 LVS 流程:SVRF 规则文件 + GDSII 版图 + SPICE 源网表 + hcell 对应列表

-

仅抽取版图网表:SVRF 规则文件 + GDSII 版图(无需源网表)

(3)输出文件

-

提取的版图网表(.net);

-

电路提取报告、LVS 对比报告(核心差异文档);

-

结果数据库(可在 Calibre RVE 中交叉探测);

-

超大规模(hyperscaling)模式下额外生成对比日志(

lvs_report_name.log)。

1. 网表类输出(抽取结果)

| 输出文件 | 说明 | 格式 | 用途 |

|---|---|---|---|

| Extracted Layout Netlist | 从版图几何数据中抽取得到的电路网表,与版图物理实现完全等价 | SPICE / Spectre / CDL | 用于仿真、后仿验证,或作为两步 LVS 的输入 |

| Reduced Netlist | 经过化简(合并串并联电阻 / 电容、移除无效器件)后的精简版图网表 | 同抽取网表格式 | 用于 LVS 比对,减少计算量,提升比对效率 |

| Source Netlist (processed) | 经过格式标准化、层次展开后的源网表(若源网表格式不兼容) | SPICE / CDL | 与抽取网表做拓扑比对 |

2. 报告类输出(比对结果)

| 输出文件 | 说明 | 格式 | 用途 |

|---|---|---|---|

| LVS Report File | 核心比对报告,包含匹配 / 不匹配统计、错误类型与位置 | 文本(.rpt/.report)/ HTML |

调试 LVS 错误,查看器件 / 网络匹配情况 |

| Error Database (SVDB) | 结构化错误数据库,包含所有不匹配项的坐标、层次、网表信息 | 二进制目录(svdb/) |

配合 Calibre RVE 工具可视化定位错误,交叉探查版图与网表 |

| Summary Report | 精简版比对摘要,包含总器件数、匹配数、错误分类统计 | 文本 / CSV | 快速评估 LVS 结果,用于流程自动化判断 |

3. 调试与辅助输出

| 输出文件 | 说明 | 格式 | 用途 |

|---|---|---|---|

| Log File | 运行日志,记录抽取、比对过程中的警告、错误与性能信息 | 文本(.log) |

排查运行崩溃、规则解析错误、性能瓶颈 |

| hcell Mapping File | 层次化单元对应关系表,记录版图单元与原理图单元的映射 | 文本 | 调试层次不匹配问题,确认单元映射是否正确 |

| Netlist Comparison Log | 网表比对的详细日志,记录每一个器件 / 网络的匹配过程 | 文本 | 定位具体的匹配失败原因(如端口顺序错误、器件类型不匹配) |

| Layer Mapping Log | 层映射日志,记录 GDS 层到电学层的转换结果 | 文本 | 排查器件识别失败、层间连接错误 |

二、核心对比机制

LVS 工具对比指定原始网表和版图中的电路连接关系。当对比的电路完全等效时,LVS 会在原始网表的电路元件(实例instance、网络nets、端口port、实例引脚)与版图电路的对应元件之间,建立一一对应的映射关系。

对于存在差异的设计,LVS 报告中会列出两个电路的不一致之处。报告将分别从原始网表视角 和版图视角 呈现差异:首先假设原始网表数据正确、版图数据错误,然后假设版图数据正确、原始网表数据错误。这种呈现方式可帮助用户对比两种可能的数据分析视角。

Calibre nmLVS 会报告与错误电路元件相关的差异,并提供辅助分类和定位错误的附加信息。为确保不同元件的匹配不会产生误导性结果,工具会应用内部启发式算法。这些内部技术会在程序不同阶段,从多种方法生成的结果中选择最优解决方案。

Calibre nmLVS 会尽可能匹配更多元件,包括对比电路中存在差异的元件。例如,若两个网络的大部分连接是等效的,即使部分连接不同,也可进行匹配。元件之间的对应关系可用于 Calibre RVE 中的交叉探测功能。

用户无需强制提供 电路元件之间的初始对应点或 LVS Cpoint 语句),但提供初始对应点通常可以缩短运行时间。对于版图与原始网表中名称不匹配的网络,指定初始对应点(Cpoint)尤为有用。

注意 通常建议在默认配置 下运行 Calibre nmLVS。这意味着,除非有特殊需求必须修改 LVS 默认设置,否则一般无需在规则文件中指定除

LVS Report、LVS Power Name和LVS Ground Name之外的其他 LVS 专用语句。LVS 报告中会列出所有规则文件规范语句的设置,包括保持默认值的选项。

2.1 网表对比的超大规模优化(Hyperscaling)

通过命令行选项 -hyper cmp,可在 Calibre nmLVS-H 中启用超大规模优化(Hyperscaling)。该优化适用于电路提取模块,且会在提取过程中执行部分对比模块任务(如读取原始网表)。仅当同时指定 -turbo 选项时 ,才能使用 -hyper cmp 选项。

启用超大规模优化的命令行示例如下:

# MT 模式

calibre -spice layout.net -turbo -hyper cmp -lvs -hier -hcell hcells rules

# MTflex 模式

calibre -turbo -remotefile config.txt -hyper cmp -lvs -hier -hcell hcells rules当版图系统为几何数据库时,后一条命令行会触发电路提取;否则,仅执行 LVS 对比。

注意

-hyper remote选项会导致 LVS 对比模块不执行cmp选项触发的优化。

启用超大规模优化后,运行过程中对比阶段的记录会写入文件 lvs_report_name.log(其中 lvs_report_name 为 LVS 报告的名称)。重要的对比信息仍会输出到标准输出(stdout),但完整的信息集将写入上述日志文件。详情请参见第 542 页的「带超大规模优化记录的层次化对比」章节。

当启用超大规模优化时,若规则文件中指定了 LVS Abort On ERC Error YES、LVS Abort On Supply Error YES 或 LVS Abort On Softchk YES 语句,LVS 会在读取原始网表后、执行对比前终止运行。

2.2 初始对应点

Calibre nmLVS 将原始网表和版图电路中 具有相同用户定义名称的网络对、实例对和端口对,作为初始对应点。工具不要求必须存在初始对应点,但建议通过在顶层单元的输入引脚上添加文本,为原始网表和版图的端口指定初始对应点。

Calibre nmLVS 会信任初始对应点 ,并强制匹配构成初始对应点的元件,即使这些元件本身存在差异。用户也可在规则文件中通过 LVS Cpoint 规范语句指定对应点。

在 Calibre nmLVS-H 中,若初始对应点出现在底层单元,不会阻止逻辑注入、逻辑门形成、串并联器件归并等转换操作;但在顶层单元 中,初始对应点会阻止此类转换。

2.3 元件类型

LVS 元件类型是一个名称,用于唯一标识 版图或原始网表实例的电气或逻辑功能。Calibre nmLVS 在匹配版图与原始网表实例的过程中会使用元件类型值。实例必须具有相同的元件类型才能被正确匹配。若实例的元件类型不同,但连接关系完全一致,工具有时也会进行匹配,但会在这种情况下报告差异。

1. 掩模版图

提取的版图器件的元件类型,等效于规则文件中对应 Device 操作的 element_name 参数值。例如,语句:

device MP tran poly(g) srcdrn(s) srcdrn(d) bulk(b)指定了一个 MOS 晶体管器件,其元件类型为 MP。

2. SPICE 网表

LVS Compare Case 语句结合 Layout Case 和 Source Case 语句,可控制 LVS 对比网络、实例、端口、元件及模型名称时的大小写敏感性 。LVS 默认不区分大小写。

2.4 元件子类型

LVS 元件子类型(模型)是一个可选名称,与元件类型共同对版图或原始网表实例的电气或逻辑功能进行分类。元件子类型不是匹配原始网表与版图实例的必要条件。仅当两个匹配实例均指定了子类型时,Calibre nmLVS 才会报告其子类型的差异。

以下章节描述了 Calibre nmLVS 用于确定实例元件子类型的规则。

1. 掩模版图

提取的版图器件的元件子类型,等效于对应 Device 操作中可选的 model_name 参数值。例如,操作:

device C(PM) cap poly(pos) metal(neg)指定了一个电容器件,其元件类型为 C,子类型为 PM。若 Device 操作中未指定 model_name,则该器件无子类型。

2. SPICE 网表

LVS Compare Case 语句结合 Layout Case 和 Source Case 语句,可控制 LVS 对比网络、实例、端口、元件及模型名称时的大小写敏感性。LVS 默认不区分大小写。

2.5 必需的器件模型名称

在规则文件的 Device 语句中,器件元件名称 MP、MN、ME、MD、Q 和 D 必须附带与原始网表中使用的模型名称完全一致的模型名。这是网表到网表对比流程的强制要求。

该规则存在两个例外情况:

-

若原始网表中对应的模型名称分别为

P、N、E和D,则可在规则文件中为器件元件名称MP、MN、ME和MD省略模型名。 -

若原始网表中对应的模型名称分别为

Q和D,则可在规则文件中为器件元件名称Q和D省略模型名。

三、命名规范与大小写敏感性

LVS 使用多种命名规则,这些规则会体现在 LVS 报告、运行记录和掩模 SVDB 目录结果中。在调试结果时,熟悉这些规则将有助于提高效率。

LVS 的命名规范直接影响初始对应点的生成和对比结果,需重点关注实例引脚、网 / 实例名、端口名、电源地网络 的定义,以及大小写敏感性的配置。

3.1. 实例引脚与引脚名称

Calibre nmLVS 在连接关系对比过程中,使用实例引脚名称匹配电路元件。引脚及引脚名称通常由实例从规则文件操作和 SPICE 网表元件中继承。

3.1.1 掩模版图

Calibre nmLVS 在规则文件中指定提取的版图器件的引脚名称,或采用默认规则。

-

内置器件 :此类器件具有默认的引脚命名和排序规则,并会被 LVS 进行特殊处理:器件类型

C、D、MD、ME、MN、MP、Q和R对于器件识别和 LVS 对比均为内置类型。每种类型都有一组必须使用的硬编码引脚名称 。若遵循第 395 页「内置器件类型」中指定的引脚名称,器件类型J、L、LDD、LDDD、LDDE、LDDN、LDDP、M和V在 LVS 对比中会被视为内置类型。若使用LVS Device Type规范语句,且遵循标准引脚命名和排序规则,任意命名的器件都可被视为内置类型。 -

用户定义器件 :规则文件中的

Device操作可指定用户定义器件(此处的「用户定义」指针对器件识别的目的)。此类器件具有用户定义的引脚名称,提取网表中的引脚顺序遵循对应Device语句中指定的顺序。若未遵循第 395 页「内置器件类型」中指定的引脚名称,器件类型J、L、LDD、LDDD、LDDE、LDDN、LDDP、M和V会被视为用户定义类型。

3.1.2 SPICE 网表

SPICE 元件的引脚名称描述;

3.1.3 引脚过滤

Calibre nmLVS 仅处理具有名称的实例引脚。在单个设计中,可使用同一元件类型但引脚数量不同的实例。例如,在单个设计中可同时存在双引脚电阻和三引脚电阻。

对于给定的元件类型和引脚数量,对应的版图和原始网表引脚应具有完全相同的名称 。但允许版图元件实例的引脚不存在于对应的原始网表元件中,反之亦然。LVS 对比算法在建立版图与原始网表元件的对应关系时,会过滤掉这些不存在的引脚。

Calibre nmLVS 过滤缺失引脚的目的,是为了允许高层版图元件拥有对应的原理图元件中不存在的引脚(如电源和地引脚)。经过引脚过滤后,实例必须具有相同的引脚数量和引脚名称,才能被正确匹配。若实例的引脚数量或名称不同,但连接关系相似,工具有时也会进行匹配,但会在这种情况下报告差异。

对于每种元件类型,版图中存在但原始网表中缺失的引脚,以及原始网表中存在但版图中缺失的引脚,都会在 LVS 报告中列出。缺失的电源或地引脚会被报告为警告,其他缺失的引脚会被报告为错误。

若在 LVS Power Name 或 LVS Ground Name 规范语句中分别指定了电源或地引脚的名称,Calibre nmLVS 会对这些引脚名称进行分类。

3.2 网络与实例名称

网络和实例名称在几何版图和 SPICE 网表中指定,两种设计类型的名称获取方式不同。

3.2.1 掩模版图

Calibre nmLVS (默认情况下)从顶层单元中版图图形和路径上的文本对象值 获取版图网络名称。这些值在 LVS 触发的电路提取过程中被分配为网络的名称。在掩模 LVS 中,无法为版图实例命名。

3.2.2 SPICE 网表

Calibre nmLVS 从网表中的节点名称 获取网络名称,从网表中的元件名称获取实例名称。

3. 3 端口与端口名称

设计端口和端口名称在几何版图和 SPICE 网表中指定。

3.3.1 掩模版图

Calibre nmLVS 通过规则文件中的 Port Layer Text、Port Layer Polygon 和 Port Layer Merged Polygon 规范语句,指定几何版图的端口。

3.3.2 SPICE 网表

Calibre nmLVS 通过两种方式指定设计端口:

-

若指定了顶层子电路,其子电路的外部节点将作为 LVS 中的设计端口。

-

除非在规则文件中指定

LVS Globals Are Ports NO,否则.GLOBAL语句中指定的所有具有用户定义名称的节点,都将作为 LVS 中的设计端口。

在上述两种情况下,节点名称均作为端口名称。

3. 4. 电源与地网络

Calibre nmLVS 在逻辑门识别、未使用 MOS 晶体管过滤及其他应用中会使用电源和地网络。单个设计中允许存在多个电源网络和多个地网络。

当满足以下任一条件时,一个网络将被视为电源网络(或地网络):

-

网络名称出现在

LVS Power Name或LVS Ground Name规范语句中。 -

网络连接到一个端口,且该端口名称出现在

LVS Power Name或LVS Ground Name规范语句中,同时同一设计中没有其他网络使用该名称。若存在多个具有相同电源(或地)名称的端口连接到不同网络,则仅使用其中一个。

通过 LVS Cell Supply 语句,与 LVS Power Name 和 LVS Ground Name 设置匹配的单元端口名称,可在层次结构中向上和向下传播电源和地网络名称,传递至连接到这些端口的网络。

3. 5. 用户定义名称

版图和原始网表数据库的网络、实例和端口可具有用户定义名称 、系统生成名称,或同时具有两者。Calibre nmLVS 会报告版图和原始网表元件的用户定义名称之间的差异。

匹配的用户定义名称会在 LVS 中建立初始对应点。

Calibre nmLVS 按以下规则判断一个名称是否为用户定义名称:

-

掩模版图 :若一个名称不以

n$、N$、i$或I$开头,且不包含超过一个 斜杠(/)字符(允许一个前导斜杠),则该名称为用户定义名称。若存在前导斜杠,该斜杠将被忽略。例如,版图名称/ABC是用户定义名称,会与原始网表名称ABC形成初始对应点;版图名称ABC也是用户定义名称,同样会与原始网表名称ABC形成初始对应点。 -

SPICE 网表:

-

若一个节点名称至少包含一个非数字字符 (字母),且不包含超过一个斜杠(

/)字符(允许一个前导斜杠),则该节点名称为用户定义名称。若存在前导斜杠,该斜杠将被忽略。 -

若一个元件名称(排除第一个字符)至少包含一个非数字且非等号(

=)的字符 ,则该元件名称为用户定义名称(SPICE 元件名称的第一个字符始终为 SPICE 元件类型)。此外,该名称不得包含任何/字符。例如,C2a、Xabc和M1==A是用户定义元件名称,而C123、X1、Xabc/X2和M1==2不是。请注意,当原始 SPICE 网表的层次结构被展开时,源自层次结构底层的节点和元件名称永远无法 成为用户定义名称,因为这些名称会变成包含/字符的层次化路径名。

-

按照惯例,前缀 n$ 和 i$ 表示 Mentor Graphics 原理图数据库中的系统生成网络和实例名称。/ 用作分隔符以形成层次化路径名。等号(=)被 SPICE 解析器用于为通过 M 参数复制的元件生成名称。

3. 6. 名称的大小写敏感处理

默认情况下,版图和原始网表名称的处理不区分大小写。

网表处理分为两个不同的阶段:读取时的网表解析,以及网表对比。这些阶段由不同的规范语句分别控制。

用户可通过 Layout Case 和 Source Case 规范语句,控制输入网表解析时的大小写敏感性。默认情况下,两者均设置为 NO。当设置为 NO 时,SPICE 解析器会在内部统一网表的大小写格式。若将其中任意一个设置为 YES,则 SPICE 网表解析器会以区分大小写的方式处理对应的网表,名称仅大小写不同的网表元件会被视为不同的元件。

当设计中存在仅大小写不同、且需要被视为不同网络的网络名称时,用户可能需要以区分大小写的方式处理输入网表。例如:

$$ SOURCE

.SUBCKT BLOCK SIG sig Y $$ SIG 和 sig 是有意区分的网络

...

$$ LAYOUT

.SUBCKT BLOCK 1 2 3

...由于 SIG 和 sig 应被视为不同的网络,用户需要在规则文件中指定 Source Case YES,以确保这些网络能够正确对比。

若希望以区分大小写的方式执行 LVS 对比,需要将 LVS Compare Case 指定为 NO 以外的选项。同时,还应将 Layout Case 和 Source Case 设置为 YES;否则,输入网表的文本大小写将无法保留,大小写对比也无法达到预期效果。Layout Case 和 Source Case 语句本身不会触发区分大小写的对比。

下表展示了五种可能有用的大小写敏感性语句组合。未展示的三种组合在大多数设计流程中通常没有实用价值。

| 命名类型 | 版图来源 | 源网表来源 | 关键说明 |

|---|---|---|---|

| 实例引脚 | 内置器件:硬编码引脚名(如 MOS 管的 G/S/D);用户定义器件:DEVICE 语句指定的引脚名 |

SPICE 元素的引脚定义(如电阻的 POS/NEG) |

仅处理有名称的引脚;缺失引脚会被过滤,电源地引脚缺失报警告,其他报错误 |

| 网 / 实例名 | 网名:顶层单元中图形的文本值;实例名:不支持在 Mask LVS 中命名 | 网名:节点名;实例名:元素名(如 M1、R2) |

用户定义名需满足特定格式(不包含 n$/i$、最多一个 /),系统生成名会被自动识别 |

| 端口名 | 由 Port Layer Text/Polygon 语句指定 |

顶层子电路的外部节点;.GLOBAL 语句指定的节点(需 LVS Globals Are Ports YES) |

端口名是重要的初始对应点来源 |

| 电源地网络 | 满足 LVS Power Name/Ground Name 的网名或端口名 |

同上 | 支持多个电源 / 地网络;用于逻辑门识别、未使用器件过滤等 |

3.7 区分大小写语句的不良影响

启用大小写敏感性可能会导致一些不良副作用,例如丢失初始对应点 (详情请参见第 385 页的「初始对应点」)。假设原始网表中有网络 a,版图中有网络 A:在不区分大小写的对比中,这些网络会形成初始对应点;但在启用大小写敏感性后,它们将不会形成初始对应点,从而导致性能下降。

对于给定元件的文本大小写不统一的网表,启用大小写敏感性可能会在解析网表时导致错误。例如,假设原始网表中包含以下内容:

.SUBCKT inst pos neg

.ENDS

...

X3 vss vdd INST若设置 Source Case NO,子电路名称 inst 和 INST 可被正确解析;但若设置 Source Case YES,且原始网表中不存在名为 INST 的子电路,则会导致错误。网表中此类大小写差异在启用大小写敏感性时可能会引发问题。

请注意,当将 Layout Case 或 Source Case 设置为 YES 时,Layout Primary 和 Source Primary 单元名称的处理会区分大小写。若规则文件与网表中的顶层单元名称存在大小写不匹配,将导致错误。

四、内置器件类型与特殊处理

Calibre 对内置器件 提供特殊处理(如器件归约、引脚交换、逻辑门识别),前提是器件满足固定的引脚命名规则 ;若不满足,则视为用户定义器件,无特殊处理。

1. 核心内置器件及引脚要求

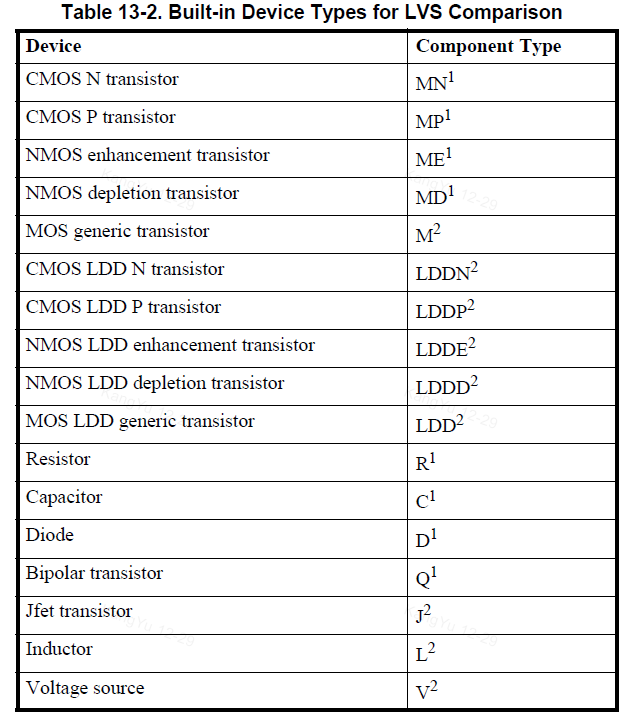

请注意,这些器件类型是相对于 LVS 电路对比子系统的内置类型。其中部分(但非全部)器件类型,对于由 Device 操作管辖的器件识别模块也是内置类型。

表 2 中以上标 ¹ 标记的器件,是对于器件识别和 LVS 对比均为内置的类型。此类器件具有硬编码的引脚名称,无法被覆盖。

对于器件识别非内置的器件,其引脚名称并非硬编码。表 13-2 中以上标 ² 标记的器件,若使用公认的引脚名称,在 LVS 对比中会表现为内置器件;但若指定了用户定义的引脚名称,则这些器件会被视为用户定义类型。此行为的详细描述请参见本节后续内容。

为了执行以下章节中描述的特殊处理,Calibre nmLVS 要求内置器件必须遵循关于引脚数量和引脚名称 的特定规则。对于不遵循这些规则的内置器件,将不会执行任何特殊处理。关于如何确定原始网表电路和版图中的引脚名称,请参见第 388 页的「实例引脚与引脚名称」章节。

用户可通过 LVS Device Type 规范语句,将任意名称的器件指定为内置器件。此类器件必须遵循本节讨论的引脚命名规则,才能参与 LVS 流程(如归并、过滤、引脚交换等)。

1. MOS 晶体管

被识别为内置器件的普通 MOS 晶体管,会被 Calibre nmLVS 进行以下特殊处理:逻辑门识别、并联晶体管归并、分裂栅归并、未使用晶体管过滤、默认启用源 / 漏引脚交换 、软衬底引脚处理,且引脚名称始终不区分大小写。

为了表现为内置器件,MOS 晶体管(元件类型 MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD,以及通过 LVS Device Type 规范语句指定的等效类型)必须至少具有三个引脚 ------ 栅极(Gate)、源极(Source)和漏极(Drain),如表 13-3 所示。此外,它们可具有任意数量的附加引脚,名称不限。第四个引脚通常代表衬底连接,按照惯例命名为 B。规则文件的 Device 语句语法会强制遵循此惯例,但 LVS 电路对比模块不强制。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

表 3 MOS 晶体管的必需引脚名称

| 引脚 | 引脚名称 |

|---|---|

| MOS 晶体管栅极 | G 或 GATE |

| MOS 晶体管源极 | S 或 SOURCE |

| MOS 晶体管漏极 | D 或 DRAIN |

| 可选引脚 | 任意名称(第四个引脚若要通过 Device M* 或 LDD* 语法检查,必须为 B) |

LDD 器件是源极和漏极引脚不可交换 的 MOS 晶体管。五种 LDD 晶体管类型 LDDN、LDDP、LDDE、LDDD 和 LDD 分别对应五种普通晶体管类型 MN、MP、ME、MD 和 M。LDD 是轻掺杂漏极(Lightly Doped Drain)的缩写。

若 MOS LDD 晶体管遵循表 13-3 的引脚规则,会被进行以下处理:逻辑门识别、并联晶体管归并、分裂栅归并、未使用晶体管过滤、软衬底引脚处理,且引脚名称始终不区分大小写。

若 MOS 器件 M、LDDN、LDDP、LDDE、LDDD 和 LDD 不具有表 13-3 所示的必需引脚名称,将不会 得到任何特殊的 LVS 对比处理,会被视为用户定义类型。请注意,用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

以下规范语句控制 Calibre nmLVS 用于 MOS 晶体管的特殊处理功能:

LVS Builtin Device Pin SwapLVS Builtin MOS NRD_NRSLVS Device TypeLVS Discard Pins By DeviceLVS Ignore Device PinLVS FilterLVS Filter Unused MOSLVS Map DeviceLVS MOS Swappable PropertiesLVS Property MapLVS Recognize GatesLVS ReduceLVS Reduce Parallel MOSLVS Reduce Semi Series MOSLVS Reduce Series MOSLVS Reduce Split GatesLVS Spice Rename ParameterLVS Short Equivalent Nodes

2. 电容器

Calibre nmLVS 对内置电容器进行以下处理:串联电容器归并、并联电容器归并、按需启用引脚交换、软衬底引脚处理,且引脚名称始终不区分大小写。

为了表现为内置器件,电容器(元件类型 C,以及通过 LVS Device Type 规范语句指定的等效类型)必须至少具有两个引脚 ,且符合表 4 的引脚名称。此外,它们可具有任意数量的附加引脚,名称不限。第三个引脚通常代表衬底连接,器件提取器默认将其命名为 SUB,但在 Device 语句中可使用任意名称。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

若在 Device 语句中指定的电容器器件与表 4 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

表 4 电容器的必需引脚名称

| 引脚 | 引脚名称 |

|---|---|

| 电容器正极引脚 | POS 或 P |

| 电容器负极引脚 | NEG 或 N |

| 可选引脚 | 任意名称 |

以下规范语句控制 Calibre nmLVS 用于电容器的特殊处理功能:

LVS Device TypeLVS Discard Pins By DeviceLVS Map DeviceLVS Netlist Comment Coded PropertiesLVS Property MapLVS ReduceLVS Reduce Parallel CapacitorsLVS Reduce Series CapacitorsLVS Spice Rename Parameter

3. 电阻器

Calibre nmLVS 对电阻器进行以下处理:串联电阻器归并、并联电阻器归并、默认启用引脚交换、软衬底引脚处理,且引脚名称始终不区分大小写。

为了表现为内置器件,电阻器(元件类型 R,以及通过 LVS Device Type 规范语句指定的等效类型)必须至少具有两个引脚 ,且符合表 5 的引脚名称。此外,它们可具有任意数量的附加引脚,名称不限。第三个引脚通常代表衬底连接,器件提取器默认将其命名为 SUB,但在 Device 语句中可使用任意名称。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

若在 Device 语句中指定的电阻器器件与表 5 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

表 5 电阻器的必需引脚名称

| 引脚 | 引脚名称 |

|---|---|

| 电阻器正极引脚 | POS 或 P |

| 电阻器负极引脚 | NEG 或 N |

| 可选引脚 | 任意名称 |

以下规范语句控制 Calibre nmLVS 用于电阻器的特殊处理功能:

LVS Builtin Device Pin SwapLVS Device TypeLVS Discard Pins By DeviceLVS Ignore Device PinLVS Map DeviceLVS Property MapLVS ReduceLVS Reduce Parallel ResistorsLVS Reduce Series ResistorsLVS Spice Rename Parameter

4. 二极管

Calibre nmLVS 对二极管进行以下处理:并联二极管归并、软衬底引脚处理,且引脚名称始终不区分大小写。

为了表现为内置器件,二极管(元件类型 D,以及通过 LVS Device Type 规范语句指定的等效类型)必须至少具有两个引脚 ,且符合表 6 的规则。此外,它们可具有任意数量的附加引脚,名称不限。第三个引脚通常代表衬底连接,器件提取器默认将其命名为 SUB,但在 Device 语句中可使用任意名称。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

若在 Device 语句中指定的二极管器件与表 6 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

表 6 二极管的必需引脚名称

| 引脚 | 引脚名称 |

|---|---|

| 二极管正极引脚 | POS 或 P |

| 二极管负极引脚 | NEG 或 N |

| 可选引脚 | 任意名称 |

以下规范语句控制 Calibre nmLVS 用于二极管的特殊处理功能:

LVS Device TypeLVS Discard Pins By DeviceLVS FilterLVS Filter Unused DiodesLVS Ignore Device PinLVS Map DeviceLVS Property MapLVS ReduceLVS Reduce Parallel DiodesLVS Spice Rename Parameter

5. 双极晶体管

Calibre nmLVS 对双极器件进行以下处理:并联双极晶体管归并、未使用双极晶体管过滤、软衬底引脚处理,且引脚名称始终不区分大小写。

为了表现为内置器件,双极器件(元件类型 Q,以及通过 LVS Device Type 规范语句指定的等效类型)必须至少具有三个引脚 ------ 集电极(Collector)、基极(Base)和发射极(Emitter)。此外,它们可具有任意数量的附加引脚,名称不限。第四个引脚通常代表衬底连接,按照惯例命名为 S。规则文件的 Device 定义语法会强制遵循此惯例,但 LVS 电路对比模块不强制。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。表 7 列出了引脚名称:

表 7 双极晶体管的必需引脚名称

| 引脚 | 引脚名称 |

|---|---|

| Q 晶体管集电极 | C |

| Q 晶体管基极 | B |

| Q 晶体管发射极 | E |

| 其他引脚 | 任意名称(第四个引脚若要通过 Device Q 语句语法检查,必须为 S) |

若在 Device 语句中指定的双极器件与表7 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

以下规范语句控制 Calibre nmLVS 用于双极晶体管的特殊处理功能:

LVS Device TypeLVS Discard Pins By DeviceLVS FilterLVS Filter Unused BipolarLVS Ignore Device PinLVS Map DeviceLVS Netlist Comment Coded PropertiesLVS Property MapLVS ReduceLVS Reduce Parallel BipolarLVS Spice Rename Parameter

6. JFET 晶体管

JFET 晶体管器件(元件类型 J)必须至少具有三个引脚------ 栅极、源极和漏极。此外,它们可具有任意数量的附加引脚,名称不限。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

若 JFET 符合表 8 的规则,Calibre nmLVS 会对其进行以下处理:软衬底引脚处理;引脚名称始终不区分大小写。

表 8 JFET 晶体管的公认引脚名称

| 引脚 | 引脚名称 |

|---|---|

| J 晶体管栅极 | G 或 GATE |

| J 晶体管源极 | S 或 SOURCE |

| J 晶体管漏极 | D 或 DRAIN |

| 其他引脚 | 任意名称 |

若在 Device 语句中指定的 J 器件与表 8 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

以下规范语句控制 Calibre nmLVS 用于 JFET 晶体管的特殊处理功能:

LVS Discard Pins By DeviceLVS FilterLVS Ignore Device PinLVS Map DeviceLVS Property MapLVS ReduceLVS Spice Rename Parameter

7. 电感器

电感器件(元件类型 L)必须至少具有两个引脚------ 正极和负极。此外,它们可具有任意数量的附加引脚,名称不限。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

若电感器符合表 9 的规则,Calibre nmLVS 会对其进行以下处理:软衬底引脚处理;引脚名称始终不区分大小写。

表 9 电感器的公认引脚名称

| 引脚 | 引脚名称 |

|---|---|

| 电感器正极引脚 | POS 或 P |

| 电感器负极引脚 | NEG 或 N |

| 可选引脚 | 任意名称 |

若在 Device 语句中指定的 L 器件与表 9 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

以下规范语句控制 Calibre nmLVS 用于电感器的特殊处理功能:

LVS Discard Pins By DeviceLVS FilterLVS Ignore Device PinLVS Map DeviceLVS Property MapLVS ReduceLVS Spice Rename Parameter

8. 电压源

电压源器件(元件类型 V)必须至少具有两个引脚------ 正极和负极。此外,它们可具有任意数量的附加引脚,名称不限。可选引脚可代表一个或多个衬底连接,或用于其他任何目的。

若电压源符合表 10 的规则,Calibre nmLVS 会对其进行以下处理:软衬底引脚处理;引脚名称始终不区分大小写。

表 10 电压源的公认引脚名称

| 引脚 | 引脚名称 |

|---|---|

| 电压源正极引脚 | POS 或 P |

| 电压源负极引脚 | NEG 或 N |

| 可选引脚 | 任意名称 |

若在 Device 语句中指定的 V 器件与表10 所示不同,这些器件会被视为用户定义类型 ,不会得到 LVS 的任何特殊对比处理。用户定义器件的引脚顺序取自规则文件中对应的 Device 语句。

以下规范语句控制 Calibre nmLVS 用于电压源的特殊处理功能:

LVS Discard Pins By DeviceLVS FilterLVS Ignore Device PinLVS Map DeviceLVS Property MapLVS ReduceLVS Spice Rename Parameter

9. X+ 器件

X+ 器件是子类型以字母 X 开头且至少包含一个其他字符的 MOS 晶体管。

规则文件示例:

DEVICE M(XP) gate poly sd sd well // X+ 器件

DEVICE M(XABC) gate poly sd sd well // X+ 器件

DEVICE M(X) gate poly sd sd well // 普通 MOS 器件SPICE 网表示例:

M1 1 2 3 4 XP $ X+ 器件

M2 1 2 3 4 XABC $ X+ 器件

M3 1 2 3 4 X $ 普通 MOS 器件X+ 器件会阻止逻辑门的形成 ,并对分裂栅归并(参见第 418 页的「分裂栅归并」)产生限制作用。在其他方面,它们的行为与普通 MOS 晶体管一致;例如,它们会受 LVS Reduce Parallel MOS、LVS Reduce Series MOS 等语句的管辖。

10. MS 和 MF 原理图器件

MS 和 MF 是 LVS 支持的特殊器件类型。它们是三引脚原理图符号 ,代表四引脚 CMOS 晶体管。第四个衬底引脚由器件类型隐含定义:

- MS 器件的衬底引脚隐含连接到源极;

- MF 器件的衬底引脚浮空。

Calibre nmLVS 会在内部为原理图中的所有 MS 实例添加一个虚拟衬底引脚 ,该引脚在内部连接到实例的源极网络,引脚名称为 B。

Calibre nmLVS 会在内部为原理图中的所有 MF 实例添加一个虚拟衬底引脚 ,并为每个实例在内部创建一个虚拟网络以表示浮空的衬底节点,实例的衬底引脚在内部连接到该虚拟网络,引脚名称为 B。

要触发此特殊处理,实例的 LVS 元件类型必须为 MN、MP、LDDN 或 LDDP,且实例必须恰好具有三个引脚 ,并使用第 395 页「内置器件类型」中指定的标准引脚名称。这意味着,必须使用除元件或 SPICE 模型以外的其他属性(建议选择 phy_comp 属性),为这些实例指定 LVS 元件类型。

2. 电路元件匹配方法

Calibre nmLVS 在两种元件匹配方法之间迭代:基于特征的哈希方法 和追踪方法。

1. 基于特征的方法

Calibre nmLVS 根据网络和实例的类型 及连接关系,为两个电路中的网络和实例分配特征(Signature)。然后,工具会根据以下因素对电路元件进行哈希处理:

- 元件的特征

- 邻近环境中元件的特征

- 环境中是否存在先前匹配的元件

环境规模会不断增大,直到找到至少一对唯一匹配的元件。工具会为所有找到的唯一匹配元件建立对应关系。

2. 追踪方法

Calibre nmLVS 将先前匹配的元件 作为初始对应点,从这些对应点开始,逐步追踪两个电路。工具会在每一步为可唯一匹配的元件建立对应关系。追踪过程会持续进行,直到发生以下情况之一:

- 所有元件均被匹配

- 检测到阻止进一步追踪的差异

- 检测到阻止进一步追踪的电路可互换部分

Calibre nmLVS 会重复上述两种方法,直到所有元件均被匹配,或无法再匹配更多元件。在后一种情况下,工具会在内部尝试修正部分错误。若错误可被修正,则会匹配更多元件,并重复该过程。

3. 电路对比结果

Calibre nmLVS 将两个对比电路的元件(网络、实例、端口)分为以下三类:

1. 正确(Correct)

这些元件属于电路中实现正确的部分。它们是与相同元件唯一匹配的元件,且在另一个电路中始终具有对应的正确元件。

2. 错误(Incorrect)

这些元件确定存在错误。它们是在另一个电路中没有相同元件的元件。错误元件可能会与另一个电路中的不同元件匹配,或保持未匹配状态(工具会给出建议匹配)。尽管原始网表电路被视为参考,但从版图视角来看,其元件也可能被分类为错误。

3. 未匹配(Unmatched)

这些元件无法唯一匹配到另一个电路中的元件,也无法被分类为错误。这可能是由附近的错误元件导致的。

Calibre nmLVS 区分错误元件和未匹配元件,以帮助用户分析错误。在大多数情况下,只需修复被分类为错误的元件,而忽略未匹配元件列表即可。当错误元件被修复后,未匹配元件在大多数情况下会被重新分类为正确。(更多信息请参见第 547 页的「LVS 报告」章节。)

4. 歧义解决(Ambiguity Resolution)

歧义通常出现在高度并行和对称的电路中。在这些电路中,部分电路可以互换而不影响连接关系,因此无法区分这些可互换部分。

Calibre nmLVS 使用命名的网络、实例和端口 作为初始对应点,以解决歧义情况。此外,工具还会使用元件子类型 解决歧义,并通过检查 Trace Property 规范语句追踪的属性来解决歧义。后一种技术仅适用于每组包含不超过一定数量元件的歧义元件组,该数量由规则文件中的 LVS Property Resolution Maximum 规范语句指定,默认值为 32。

Calibre nmLVS 会为哈希电路元件所用的环境规模设置最大限制 。环境规模由多种因素决定,包括电路大小。若超过环境限制且无法找到唯一匹配,LVS 会进入歧义解决阶段 。在该阶段,工具会对无法通过其他方式解决的部分元件进行任意匹配。工具仅允许进行最少量的任意匹配,任意匹配的元件会在 LVS 报告中列出。若任意匹配不正确,Calibre nmLVS 会在后续阶段产生差异。在这种情况下,用户应为任意匹配的元件或其附近的其他元件分配版图文本名称。

为避免任意匹配,用户应为电路可互换部分的网络命名 。可为每个可互换部分命名一个元件。对于对称电路的外部端口,应始终进行命名。

| 器件类型 | 组件类型 | 必需引脚名 | 特殊处理 |

|---|---|---|---|

| MOS 管(含 LDD 型) | MN/MP/ME/MD/M/LDDN/LDDP |

G/GATE、S/SOURCE、D/DRAIN |

并行 / 串联归约、分裂栅归约、S/D 引脚交换、逻辑门识别、未使用器件过滤 |

| 电阻 | R |

POS/P、NEG/N |

并行 / 串联归约、引脚交换 |

| 电容 | C |

POS/P、NEG/N |

并行 / 串联归约、可选引脚交换 |

| 二极管 | D |

POS/P、NEG/N |

并行归约 |

| 双极晶体管 | Q |

C(集电极)、B(基极)、E(发射极) |

并行归约、未使用器件过滤 |

七、关键注意事项

-

默认配置优先:除非有特殊需求,否则无需修改 LVS 的默认配置,仅需指定报告、电源地网络即可;

-

初始对应点的重要性:顶层端口的命名是最有效的初始对应点,能大幅提升对比效率;

-

内置器件的引脚规则:严格遵循内置器件的引脚命名要求,才能获得归约、引脚交换等特殊处理,减少差异报告的数量;

-

大小写敏感的副作用:开启前需确保网表中名称的大小写一致性,避免丢失初始对应点或解析错误。