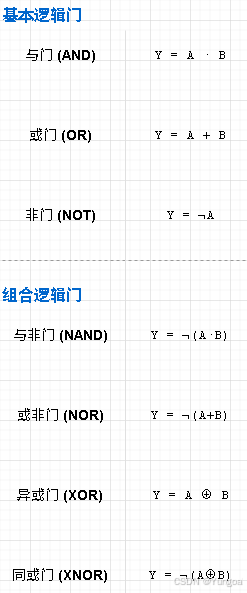

四个基本逻辑门

四个基本逻辑门,它们用电路物理实现了最基本的布尔运算。所有复杂的处理器和数字系统,归根结底都是由这四种基本门组合而成。

与:全1为1

或:全0为0

以下是它们的详细介绍:

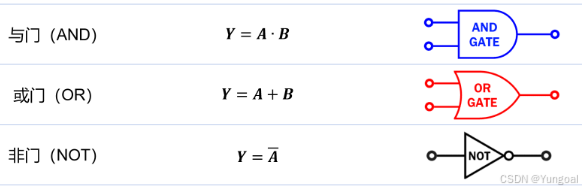

1. 与门

-

逻辑功能 :执行"逻辑与"操作。只有当所有输入都为真时,输出才为真。它实现的是"全有则然,缺一则否"。

-

布尔表达式 :

Y = A · B或Y = A AND B -

真值表:

A B Y 0 0 0 0 1 0 1 0 0 1 1 1 -

电路符号:通常是一个类似"D"形的形状,输入端在左侧平边,输出端在右侧弧边。

-

通俗比喻:串联开关。只有所有开关都闭合(1),灯才会亮(1)。

2. 或门

-

逻辑功能 :执行"逻辑或"操作。只要至少有一个输入为真,输出就为真。它实现的是"有一则然,全无则否"。

-

布尔表达式 :

Y = A + B或Y = A OR B -

真值表:

A B Y 0 0 0 0 1 1 1 0 1 1 1 1 -

电路符号:类似一个弧形朝向输入端的形状。

-

通俗比喻:并联开关。任意一个开关闭合(1),灯就会亮(1)。

3. 非门

-

逻辑功能 :执行"逻辑非"操作。它进行取反,输出总是与输入相反。它实现的是"是则非,非则是"。

-

布尔表达式 :

Y = Ā或Y = NOT A -

真值表:

A Y 0 1 1 0 -

电路符号:一个三角形前端加一个小圆圈。圆圈代表取反。

-

通俗比喻:一个常闭开关。输入为"开"(1)时,输出反而"关"(0)。

4. 与非门

-

逻辑功能 :"与"和"非"的组合 。先进行"与"操作,然后对结果取反。只有当所有输入都为真时,输出才为假。

-

布尔表达式 :

Y = A · B(上划线表示取反) -

真值表:

A B Y 0 0 1 0 1 1 1 0 1 1 1 0 -

电路符号:与门的符号输出端加一个小圆圈。

-

特殊地位 :与非门被称为"通用逻辑门"。理论上,仅用足够多的与非门就可以组合出与、或、非等所有其他逻辑功能,从而构建任何数字系统。这在集成电路制造中极具价值。

8位加法器

核心工作原理概述

8位二进制加法器的核心功能是计算两个8位二进制数的和,并产生一个8位的结果以及一个可能的进位输出。

8位二进制加法器的工作原理,就是通过8个相同的1位全加器单元级联,将低位的进位输出作为高位的进位输入,从而实现两个8位二进制数的并行相加。

**其核心在于"全加器"的逻辑和"进位链"的传递。**

第一层:基本单元 ------ 1位全加器

8位加法器由8个相同的"1位全加器"连接而成。理解全加器是关键。

一个1位全加器有三个输入、两个输出:

-

输入:

-

A:被加数的某一位。 -

B:加数的某一位。 -

Cin:来自低一位的进位输入。

-

-

输出:

-

S:本位和。 -

Cout:向高一位的进位输出。

-

其逻辑功能由以下真值表定义,并可以用与门、或门、异或门组合实现:

| A | B | Cin | **S (和)** | **Cout (进位)** |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

逻辑表达式(可由真值表推导):

-

本位和 S :

S = A ⊕ B ⊕ Cin(⊕ 表示异或运算)。这表示当输入中1的个数为奇数时,和为1。 -

进位 Cout :

Cout = (A AND B) OR (Cin AND (A ⊕ B))。这表示产生进位的两种情况:A和B都为1;或者A和B中有一个为1且低位有进位。

第二层:整体结构 ------ 级联与进位链

将8个1位全加器按位顺序连接,就构成了一个8位行波进位加法器。

-

连接方式:

-

最低位(第0位,LSB)全加器的

Cin通常接地(0),或者作为整个加法器的进位输入。 -

第

i位全加器的Cout直接连接到第i+1位全加器的Cin。 -

所有8对

A[i]和B[i]并行输入。

-

-

工作过程(以计算

0110 1101 + 1001 0101为例):-

第0位(最低位) :

A0=1, B0=1, Cin=0。根据全加器逻辑:S0=0, Cout=1。这个Cout=1成为第1位的Cin。 -

第1位 :

A1=0, B1=0, Cin=1。计算得:S1=1, Cout=0。进位0传向第2位。 -

第2位 :

A2=1, B2=1, Cin=0。计算得:S2=0, Cout=1。进位1传向第3位。 -

**以此类推...** 进位信号像波浪一样从最低位向最高位"行波"传递。

-

第7位(最高位,MSB) :计算完成后,产生最终的和位

S7以及整个8位加法器的最终进位输出Cout。这个Cout在计算机中会被存入状态寄存器(如进位标志位CF),用于判断无符号数是否发生了溢出。

-

-

关键特点与局限:

-

优点:结构简单,易于理解,是加法器的基础形式。

-

缺点 :速度受限于进位链 。最高位必须等待最低位的进位信号逐级传递上来才能得到正确结果,这称为"行波进位延迟"。对于32位或64位的现代CPU,这种延迟是不可接受的。

-

解决方案 :现代CPU使用超前进位加法器 等更先进的结构,通过并行计算提前预测所有位的进位,从而极大提升运算速度。但8位行波进位加法器是其最直观的原理模型。

-

计算机用二进制表示负数:

计算机主要使用 **"补码"** 来表示和存储负数。这种方案完美地将加法和减法统一为同一套硬件运算,是现代计算机设计的基石。

为了理解为什么选择补码,我们先看两种更直观但已被淘汰的方案:

1. 原码(直观但被淘汰)

-

方法 :最高位作为符号位(0正1负),其余位表示绝对值。

-

示例 (8位):

+5=0000 0101,-5=1000 0101 -

致命缺陷:

-

存在

+0和-0:0000 0000和1000 0000,这会导致比较和运算复杂化。 -

加减法电路不统一:做加法需要一套逻辑,做减法(本质是加负数)需要另一套判断符号、比较绝对值大小的复杂逻辑,硬件设计低效。

-

2. 反码(过渡方案)

-

方法 :正数不变。负数在其正数原码基础上,所有位取反。

-

示例 :

+5=0000 0101,-5=1111 1010 -

进步与遗留问题:

- 它向"统一运算"迈进了一步,但仍未解决

+0和-0的问题 (0000 0000和1111 1111)。

- 它向"统一运算"迈进了一步,但仍未解决

3. 补码(现行标准)

补码彻底解决了以上所有问题。其定义和优势如下:

定义

最高位仍作为符号位(0正1负)

-

正数的补码 :与其原码相同。

-

负数的补码 :在其正数原码基础上,所有位取反(得到反码),然后加1 。这个"取反加一"是计算补码的快捷方法。

-

示例(8位):

-

+5=0000 0101 -

-5的计算:+5(0000 0101) → 取反 (1111 1010) → 加1 (1111 1011)。所以-5=1111 1011。

-

原理:

-

统一加减法 :在固定位数的系统中(如8位),存在一个"模"(这里是2⁸=256)。补码的本质是 "用模减去该数的绝对值"。

-

对于 -5,就是 +251-256。

251=1111 1011256=1 0000 0000

+5=0000 0101-5=251-256=1111 1011-1 0000 0000=

1111 1011(补码) -

示例:计算

7 - 5(即7 + (-5))0000 0111 (7的补码) + 1111 1011 (-5的补码) -------------------- 0000 0010 (结果为2,最高位进位1被丢弃,相当于-1 0000 0000)硬件只需一个标准的加法器,无需任何特殊判断。

-

-

解决零的唯一性 :在补码中,

0只有一种表示0000 0000。计算-0(即对0000 0000取反加1)会得到10000 0000(9位),在8位系统中,最高位1被丢弃,结果仍是0000 0000。 -

表示范围对称 :对于n位补码,可表示的范围是 [-2ⁿ⁻¹, 2ⁿ⁻¹ - 1] 。

因为最高位是符号位(0正1负),所以8位实际表示位数是7位-

8位:[-128, +127]

-

16位:[-32768, +32767]

-

这种不对称性(负数比正数多一个)是因为 0占用了正数区间的一个编码。

正数不是从0000 0000开始的,0被单独归类

正数从0000 0001开始到0111 1111为2^7-1=127个

负数从-1=1111 1111到-128=(+128)1000 0000取反0111 1111+1=1 1000 0000无法表示。-128是特殊的直接定义的,定义为1000 0000.

负数从1111 1111到1000 0000为2^7=128个

-

计算机使用补码表示负数,让CPU的算术逻辑单元只需一套加法电路,就能处理所有有符号整数的加减运算,这是现代计算机高性能设计的关键之一。

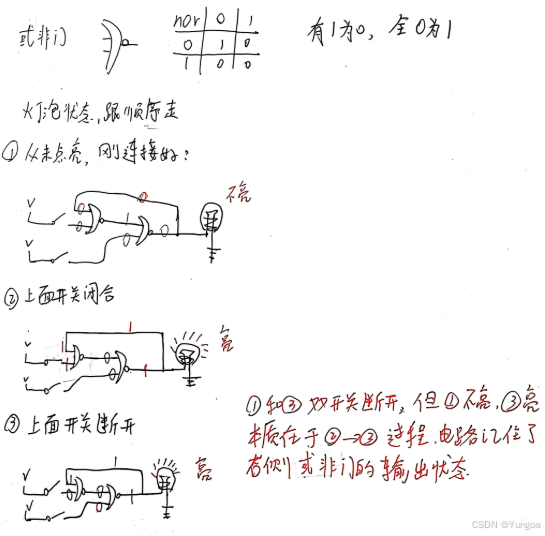

R-S触发器

触发器的记忆性:

触发器具有记忆性,指的是它能存储并保持一位二进制信息(0或1),即使触发信号消失后,其输出状态也能保持不变,直到下一次有效触发信号到来。这使其成为数字电路中的基本记忆单元。

一个电路可称作触发器,通常需要具备以下核心特征:

-

具有两个稳定的输出状态:代表逻辑0和逻辑1。

-

具备锁存或存储机制:通过内部反馈结构(如两个交叉耦合的门电路)来维持当前状态,这是实现记忆功能的关键。

-

受触发信号控制:具有一个或多个控制输入端(如时钟、置位、复位端),能在特定条件下改变其存储的状态。

因此,触发器本质上是一种具有记忆功能、能够存储一位二进制数据的基本时序逻辑电路单元。

R-S触发器是最基本、最核心的触发器类型,它清晰地展示了触发器如何通过反馈回路实现"记忆"功能。它主要分为两种:基本R-S触发器 和钟控R-S触发器 。下面以最基础的用与非门构成的基本R-S触发器为例进行详细讲解。

一、电路构成

它由两个与非门(NAND Gate)交叉耦合而成。

-

输入端 :有两个,分别是

S(Set,置位端) 和R(Reset,复位端) 。输入信号为低电平有效 (即逻辑0时起作用,通常在符号上用小圆圈或上划线表示,如S̅和R̅)。 -

输出端 :有两个,分别是

Q 和Q̅(Q非) 。这两个输出端的状态始终相反,这是电路结构决定的。我们定义Q端的状态为触发器的状态。

二、工作原理(低电平有效)

电路的状态变化完全由 R和 S端的输入组合决定。其工作原理(真值表)如下:

| R (复位) | S (置位) | Q (状态) | Q̅ (反相) | 功能说明 |

|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 置位 (Set) :S=0有效,无论触发器原来是什么状态,都会被强制设置为 Q=1。 |

| 0 | 1 | 0 | 1 | 复位 (Reset) :R=0有效,无论触发器原来是什么状态,都会被强制清零为 Q=0。 |

| 1 | 1 | 保持 | 保持 | 保持 (Hold) :当两个输入端都无效(为高电平1)时,两个与非门相当于被"锁住",通过交叉反馈维持原来的输出状态不变。**这是实现"记忆"功能的关键状态。** |

| 0 | 0 | **不稳定 (禁止)** | 不稳定 | 禁止 (Invalid) :两个输入端同时有效(为低电平0)是不允许的。这会强制使 Q和 Q̅都输出1,破坏了二者互反的逻辑关系。当输入信号同时撤消(回到1)后,最终状态是随机的、不可预测的。因此这种输入组合被禁止使用。 |

理解置位、复位、保持 这三个状态,是掌握其工作原理的核心。你可以把它们想象成一个具有记忆功能的电子开关。

简单来说:

-

置位 (Set) :就是把开关打开 (让输出Q变为1)。

-

复位 (Reset) :就是把开关关闭 (让输出Q变为0)。

-

保持 (Hold) :就是让开关保持它当前的状态,记住之前是开还是关。

下面用最常用的低电平有效型基本R-S触发器(由两个与非门构成)来详细解释:

1. 置位 (Set) - 让Q变成"1"

-

操作 :在置位端

S̅输入一个低电平(0) ,同时保证复位端R̅为高电平(1)。 -

结果 :无论触发器原来是什么状态,它都会被强制设置 为

Q=1(Q̅=0)。 -

类比:就像按下了电灯的"开"按钮,灯一定会亮起来。

-

记忆口诀 :"S for Set, Set to 1"。

2. 复位 (Reset) - 让Q变成"0"

-

操作 :在复位端

R̅输入一个低电平(0) ,同时保证置位端S̅为高电平(1)。 -

结果 :无论触发器原来是什么状态,它都会被强制清零 为

Q=0(Q̅=1)。 -

类比:就像按下了电灯的"关"按钮,灯一定会熄灭。

-

记忆口诀 :"R for Reset, Reset to 0"。

3. 保持 (Hold) - 记住当前状态

-

操作 :在两个控制端

S̅和R̅都输入高电平(1),即两个按钮都"没被按下"。 -

结果 :触发器的输出状态完全不变,会一直维持上一次被置位或复位后的结果。

-

关键意义 :这是触发器实现"记忆"功能的根本所在。它不需要外部持续输入信号,仅靠内部两个门电路的交叉反馈,就能"锁住"并记住之前的状态。

-

类比:电灯的开关既没被按到"开",也没被按到"关",它就保持当前的亮或灭的状态。

三者关系总结与核心要点

| 状态 | 输入 (S̅, R̅) | 输出 Q | 功能本质 |

|---|---|---|---|

| 置位 | (0, 1) | 1 | **写入数据"1"** |

| 复位 | (1, 0) | 0 | **写入数据"0"** |

| 保持 | (1, 1) | 不变 | 存储/记忆数据 |

重要提示:

还存在第四种禁止状态 (S̅=0, R̅=0),它会导致输出不确定,在实际电路中必须避免。

总结理解:

你可以把R-S触发器看作一个最简单的1位数据存储器:

-

置位和复位是"写操作"(写入1或0)。

-

保持是"读操作"的基础,它让已经写入的数据能够被保存下来,供后续电路使用。正是"保持"状态的存在,才使得触发器超越了简单的组合逻辑,成为了具有记忆功能的时序逻辑基石。

三、保持位

"保持位"并不是后来"增加"到R-S触发器中的一个独立部件,而是其电路结构(两个门交叉耦合)所固有的、最核心的功能状态。

**"保持"状态,是R-S触发器相对于简单组合逻辑电路的根本性优化和质变。**

它解决了组合逻辑无法解决的"记忆"问题。

表(低电平有效型)

| 状态分类 | 输入条件 (S̅, R̅) | 输出 Q | 输出 Q̅ | 功能解释 |

|---|---|---|---|---|

| **置位 (Set)** | **(0, 1)** | 1 | 0 | 强制将触发器"打开",记住 1 |

| **复位 (Reset)** | **(1, 0)** | 0 | 1 | 强制将触发器"关闭",记住 0 |

| **保持 (Hold)** | **(1, 1)** | 不变 | 不变 | 记忆关键:锁存之前的状态 |

| **禁止 (Invalid)** | **(0, 0)** | **不定 (X)** | **不定 (X)** | 非法状态,必须避免 |

注 :

S̅和R̅上的横线代表"低电平有效",即输入0才表示有动作。