AD9361简介

AD9361是一款高性能、高度集成的射频捷变收发器™,专为3G和4G基站应用而设计。其可编程性和宽带特性使其成为广泛收发器应用的理想选择。该器件将射频前端与灵活的混合信号基带部分及集成频率合成器相结合,通过提供可配置的数字处理器接口简化了设计流程。AD9361接收器本地振荡器工作频率范围为70 MHz至6.0 GHz,发射器本地振荡器工作范围为47 MHz至6.0 GHz,覆盖了大多数许可和非许可频段。支持从小于200 kHz到56 MHz的信道带宽。

两个独立的直接变频接收器具有业界领先的噪声系数和线性度。每个接收(RX)子系统都包含独立的自动增益控制(AGC)、直流偏移校正、正交校正和数字滤波功能,从而无需在数字基带中实现这些功能。AD9361还具备灵活的手动增益模式,可通过外部进行控制。每个通道配备两个高动态范围模数转换器(ADC),用于将接收到的I/Q信号数字化,并通过可配置的抽取滤波器和128抽头有限脉冲响应(FIR)滤波器进行处理,最终以适当的采样率输出12位数字信号。

该发射器采用直接转换架构,在超低噪声条件下实现高调制精度。这种发射器设计可产生业界领先的<−40 dB的发射误差矢量幅度(EVM),为外部功率放大器(PA)的选择提供了显著的系统裕量。板载发射(TX)功率监测器可用作功率检测器,实现高精度的发射功率测量。

全集成的锁相环(PLL)为所有接收和发送通道提供低功耗分数N频率合成。频分双工(FDD)系统所要求的通道隔离功能已集成到设计中。所有压控振荡器(VCO)和环路滤波器组件均为内置式。

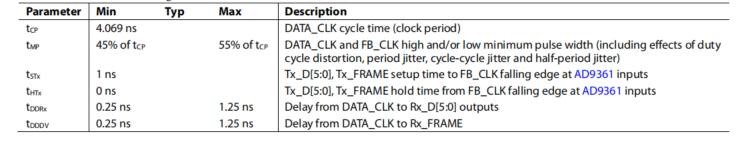

如下是AD9361框图:

RX1、RX2通道分有A.B.C三种输入选择,其中A是最优选择,BC在3G以下频段使用。

TX1、TX2只能选择A输出。

AD9361数字接口

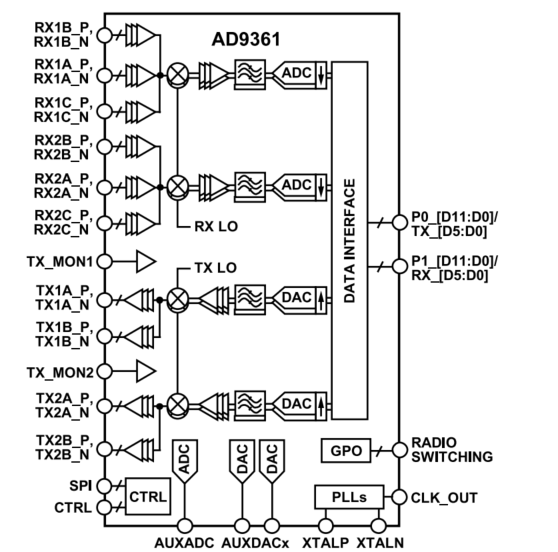

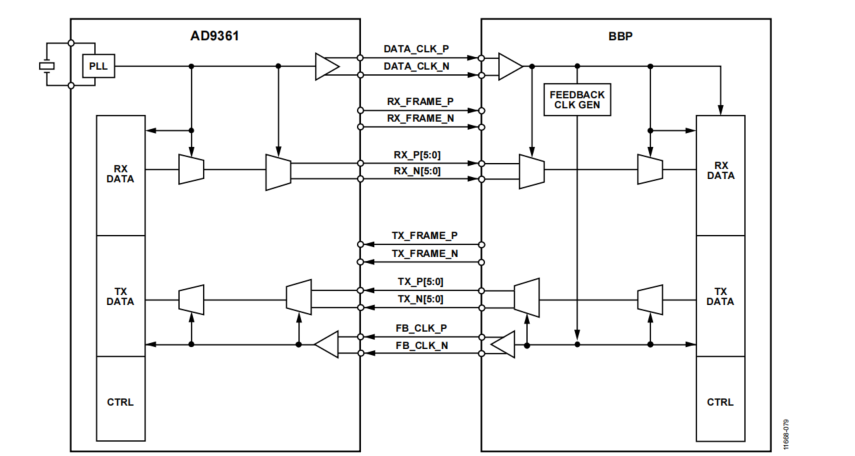

AD9361数字接口如下所示:

数字接口主要包含3部分:

- SPI控制接口,由SPI_ENB、SPI_CLK、SPI_DI、SPI_DO组成。

- 控制IO信号,由TXNRX、ENABLE、EN_AGC、CTRL_OUT、CTRL_IN、SYNC_IN、RESETB组成。

- 数据传输接口,由P0_D[11:0]和P1_D[11:0]、DATA_CLK、FB_CLK、RX_FRAME、TX_FRAME组成。

SPI控制接口

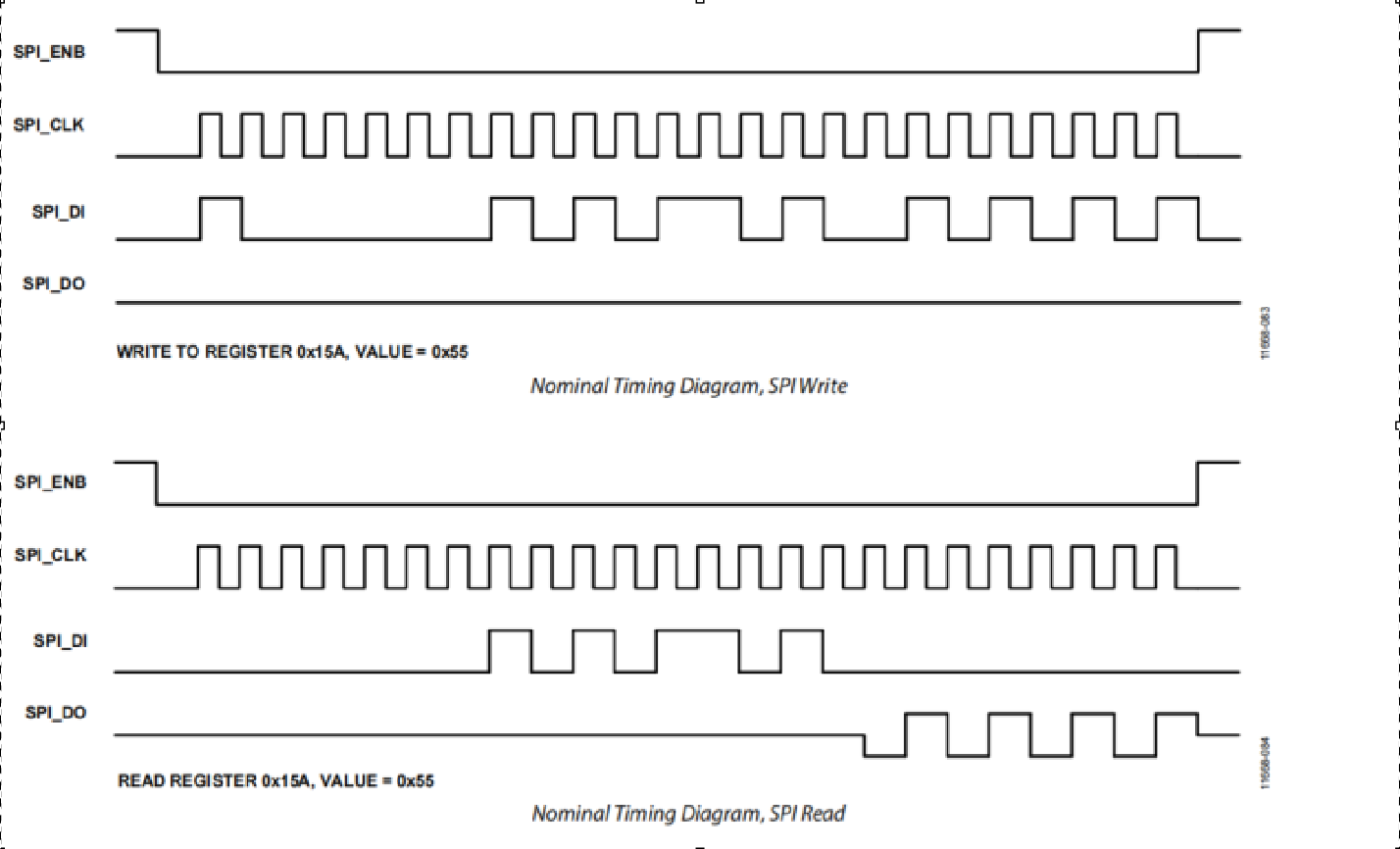

基带通过SPI总线对AD9361进行配置,如下分别是单寄存器写入操作与单寄存器读取操作的时序图:

在实际使用中通常使用ADI提供的程序驱动基带芯片(如ZYNQ7000)的SPI接口控制AD9361。

控制IO信号

- TXNRX、ENABLE

AD9361收发器配备有使能状态机(ENSM),可实时控制设备当前状态。该 ENSM 支持两种控制方式:

- SPI控制:ENSM 通过异步写入SPI寄存器实现状态切换,使当前状态逐步过渡至下一状态,SPI控制功能默认处于禁用状态,如果基带具备实时控制SPI写入的能力或者对控制的实时性要求不高时便可以使用SPI进行控制。

- 引脚控制:ENABLE引脚与 TXNRX 引脚可实时调控设备状态,若基带具备实时控制GPIO输出的能力建议使用ENABLE引脚与 TXNRX 引脚控制

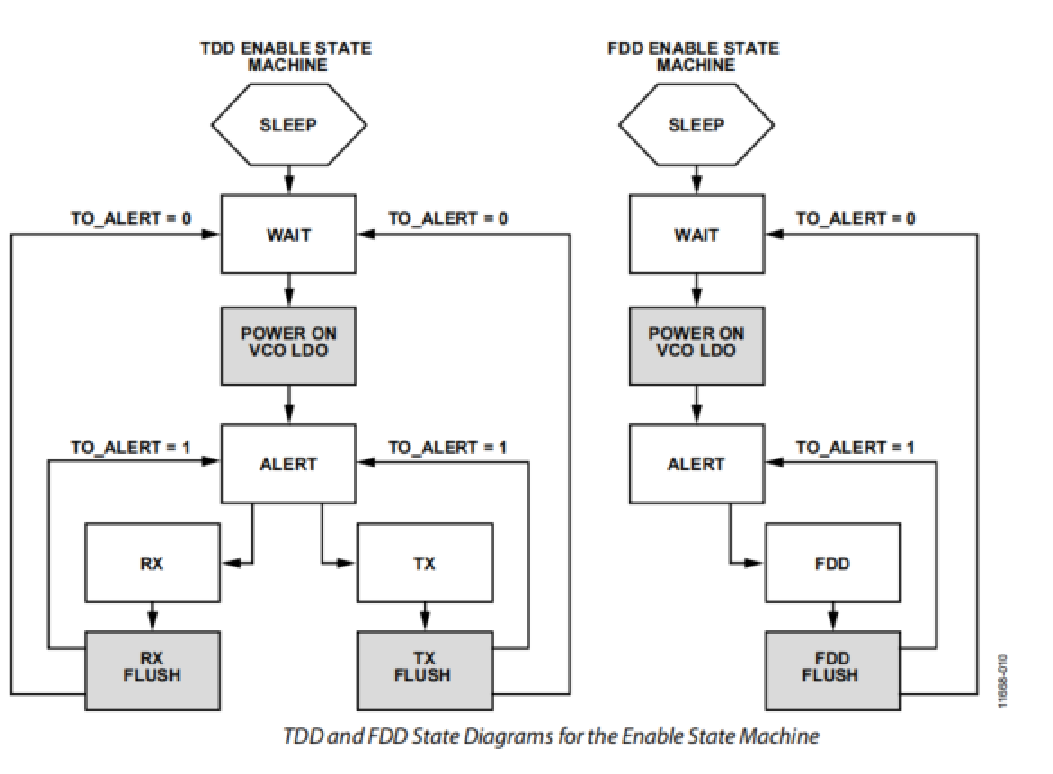

ENSM 支持 TDD 或 FDD 操作模式,如下是ENSM在TDD模式和FDD模式的状态图,其中灰色部分用户不可干预:

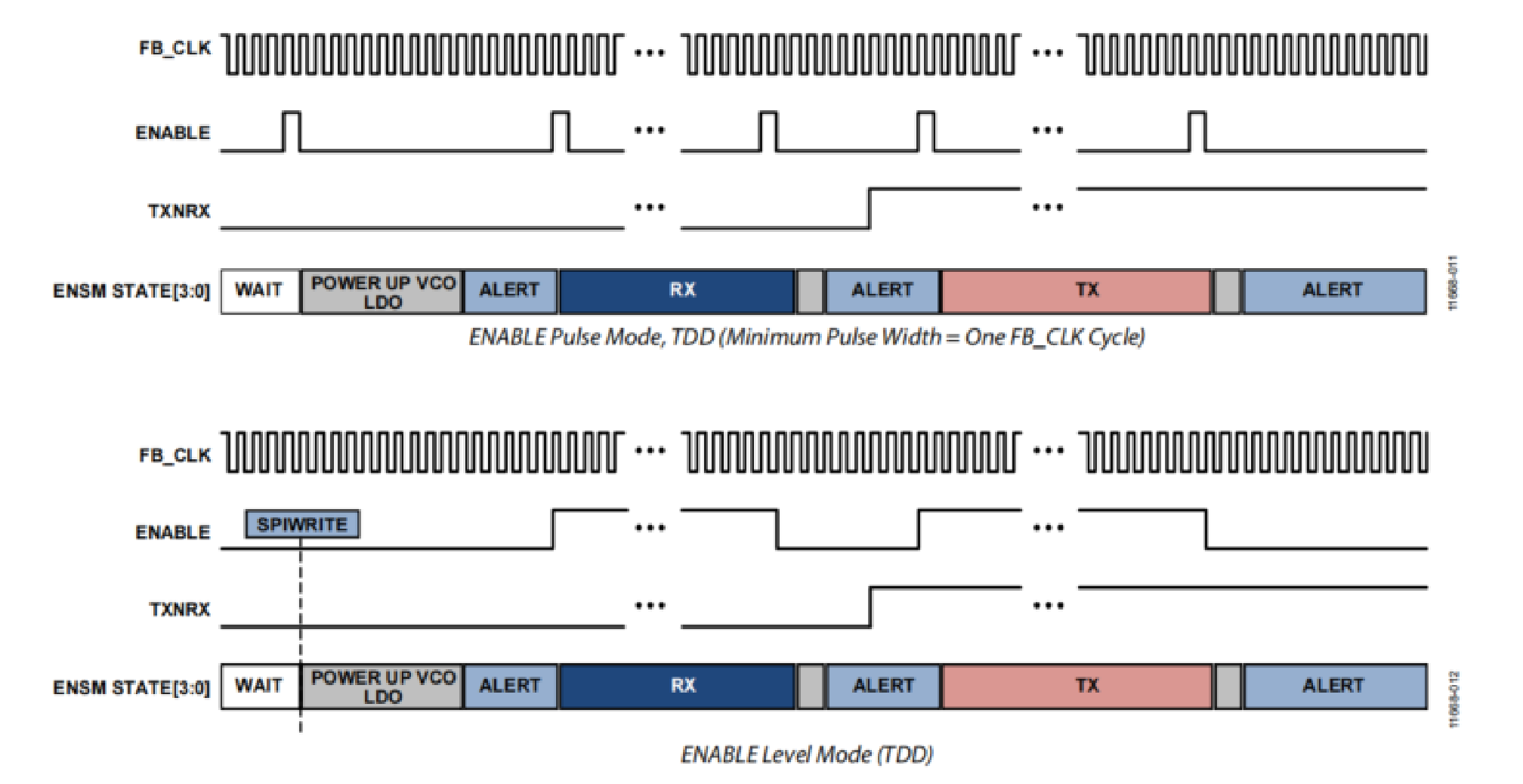

- TDD模式下TXNRX、ENABLE与收发状态的时序图

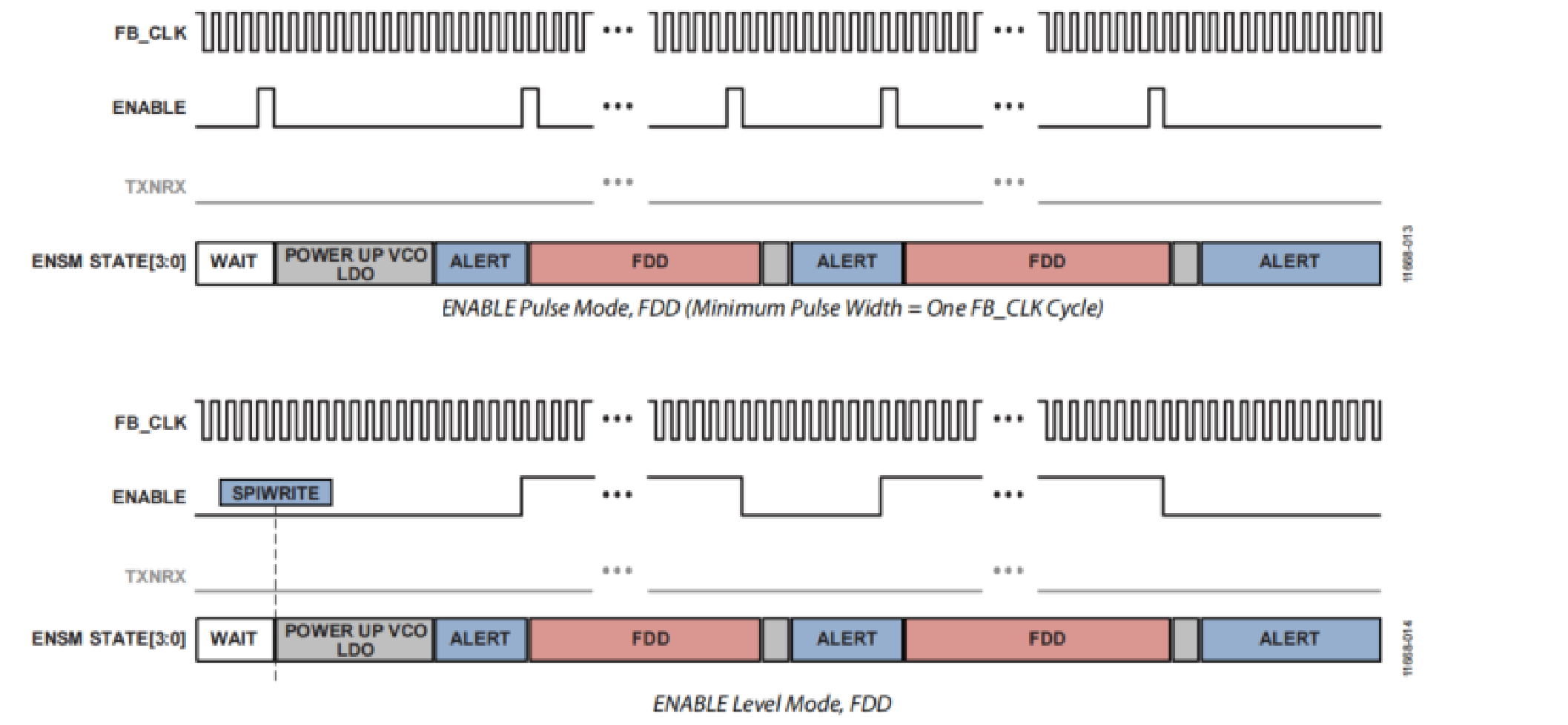

- FDD模式下TXNRX、ENABLE与收发状态的时序图

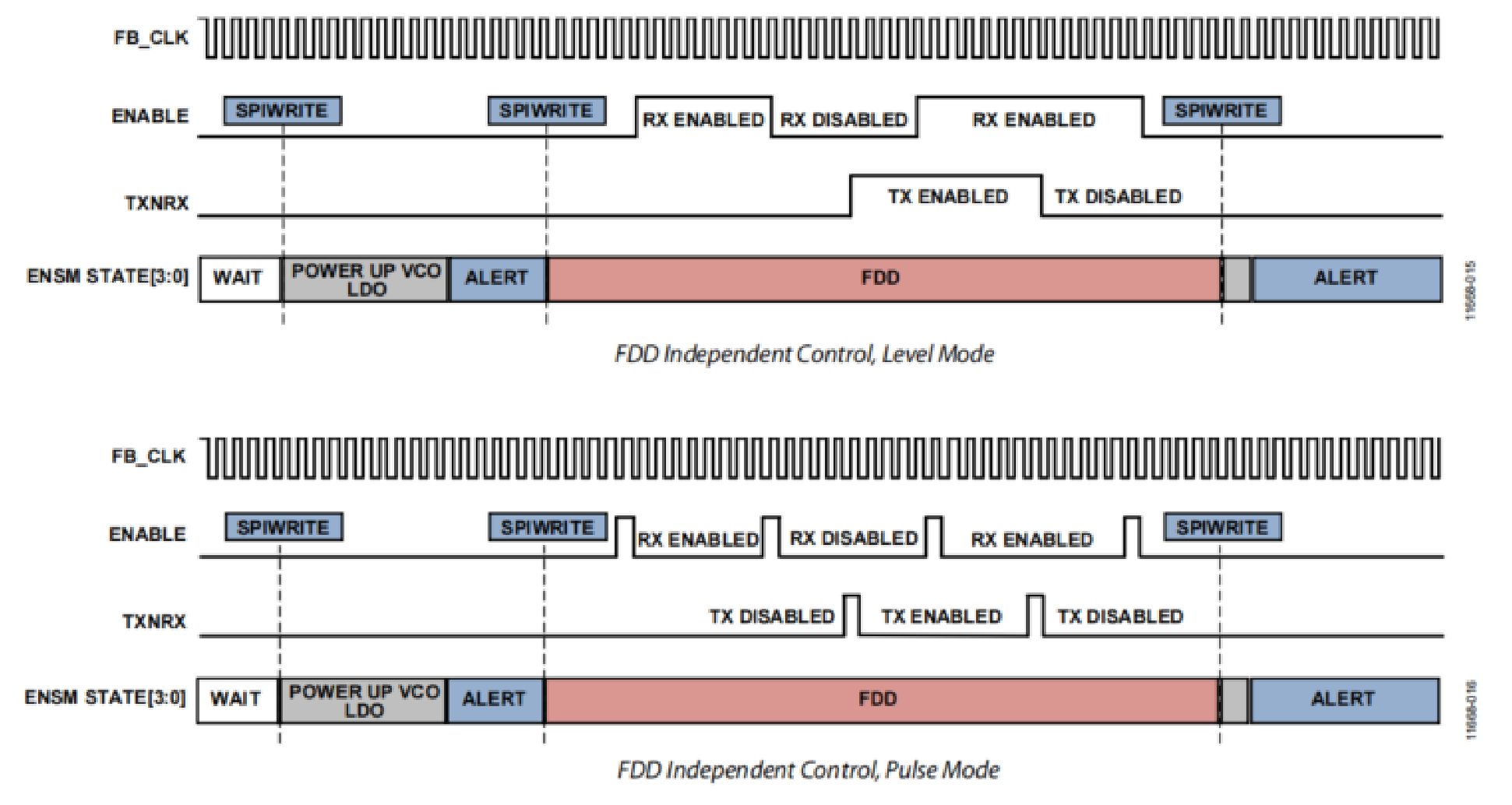

- FDD独立控制模式下TXNRX、ENABLE与收发状态的时序图

有关工作模式的内容参考《AD9361 Reference Manual UG-570》的"ENABLE STATE MACHINE GUIDE"章节。

- EN_AGC

AD9361收发器具备多种增益控制模式,可适用于多种应用场景。该器件提供全自动增益控制(AGC)模式,可同时支持时分双工(TDD)和频分双工(FDD)工作模式。此外,AD9361还支持手动增益控制(MGC)功能,使基带能够自主调节接收器增益。

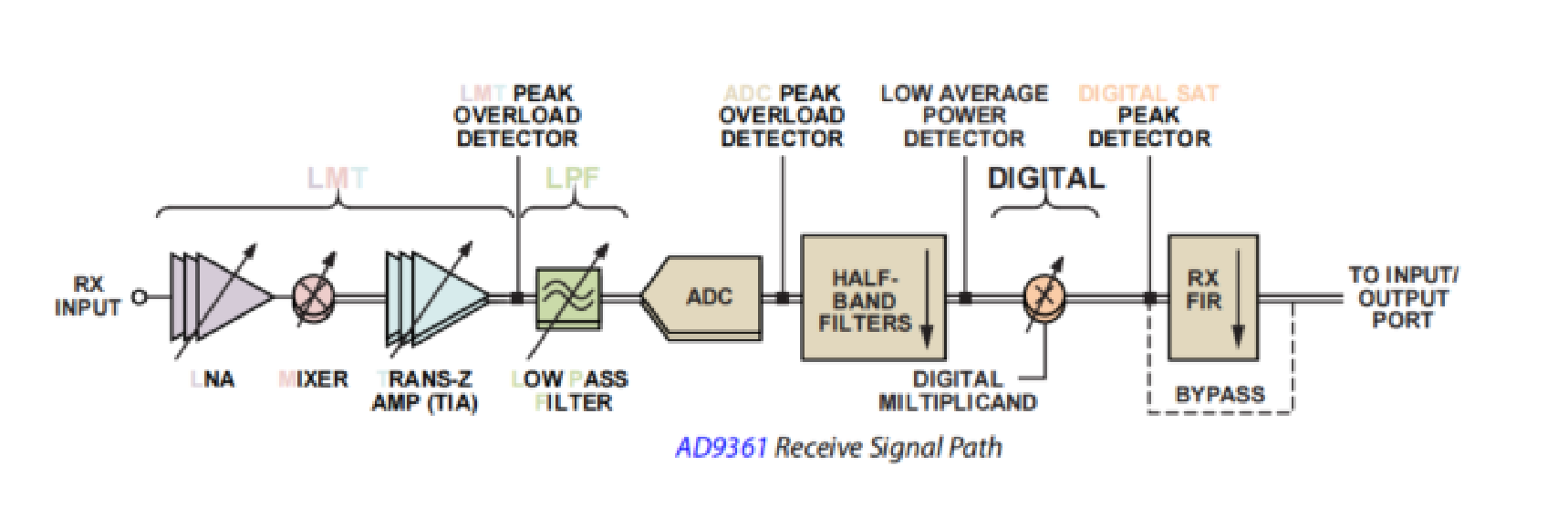

AD9361接收信号路径可划分为多个模块,几乎所有模块都具备调节增益的功能。

在全自动增益控制(AGC)模式下EN_AGC拉高时增益解锁,此时AD9361会检测接收信号功率和自动增益控制相关配置自动调节增益。

有关增益控制的内容参考《AD9361 Reference Manual UG-570》的"GAIN CONTROL"章节 - CTRL_OUT

八个可编程数字输出信号,用于实时处理。这些输出信号包含内部生成的功能和状态位,例如PLL锁定、校准完成等。 - CTRL_IN

CTRL_IN引脚为四个可编程输入信号,可用于实时控制接收机。 - SYNC_IN

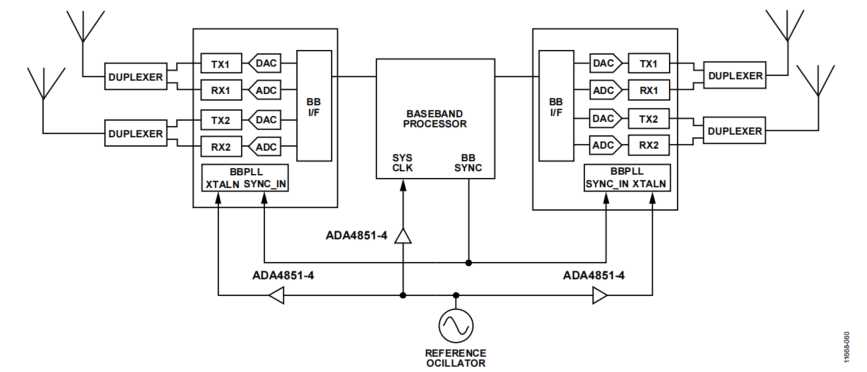

AD9361支持多个芯片同步工作,如下是一个2片AD9361同步工作的示意图:

在配置多芯片同步工作的过程中需要使用SYNC_IN信号触发AD9361内部的同步操作。

有关多芯片同步的内容参考《AD9361 Reference Manual UG-570》的"BASEBAND SYNCHRONIZATION"章节 - RESETB

AD9361进行异步硬件复位的输入信号。向该引脚施加低电平逻辑信号可复位设备。

数据传输接口

数据传输接口支持两种工作模式:标准CMOS兼容模式与低压差分信号(LVDS)兼容模式,这里介绍LVDS模式,相应的引脚功能定义如下图:

- DATA_CLK

DATA_CLK是由AD9361生成的差分LVDS信号,作为主时钟提供给基带处理器(BBP),用于接收数据路径。 - FB_CLK

FB_CLK是由基带处理器(BBP)驱动的差分LVDS信号,是DATA_CLK的反馈(回环)版本。 - Rx_FRAME

Rx Frame是源自AD9361并传输至 BBP 的差分 LVDS 信号,用于对AD9361提供的数据样本进行帧同步。 - Rx_D[5:0]

Rx_D[5:0]是一个由六对差分线组成的差分 LVDS 数据总线,数据从AD9361驱动至 BBP - Tx_FRAME

Tx Frame是源自 BBP 并传输至AD9361的差分 LVDS 信号,用于对 BBP 提供的数据样本进行帧同步。 - Tx_D[5:0]

Tx_D[5:0]是一个由六对差分线组成的差分 LVDS 数据总线。该总线从 BBP 驱动至AD9361,

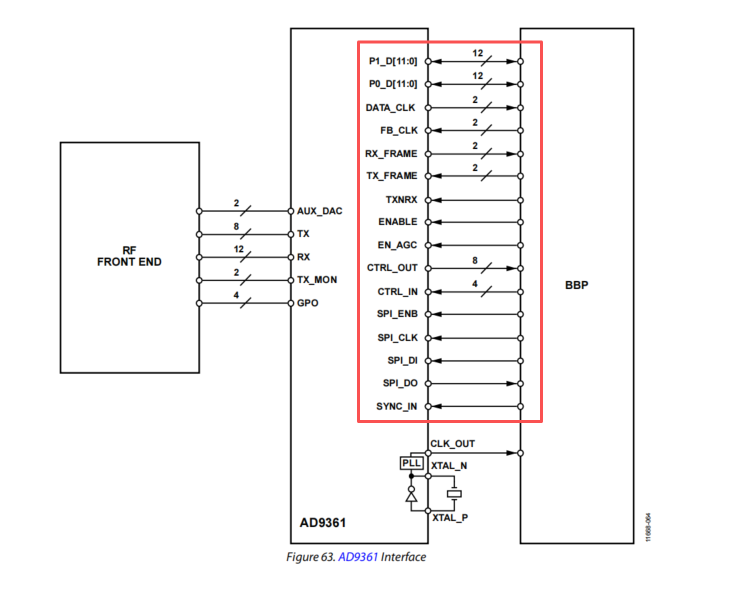

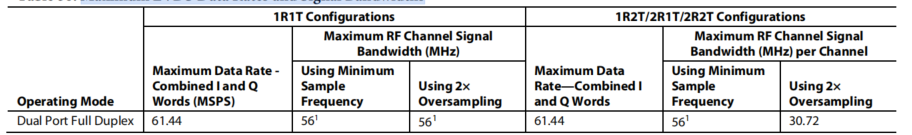

最大 LVDS 数据速率与信号带宽:

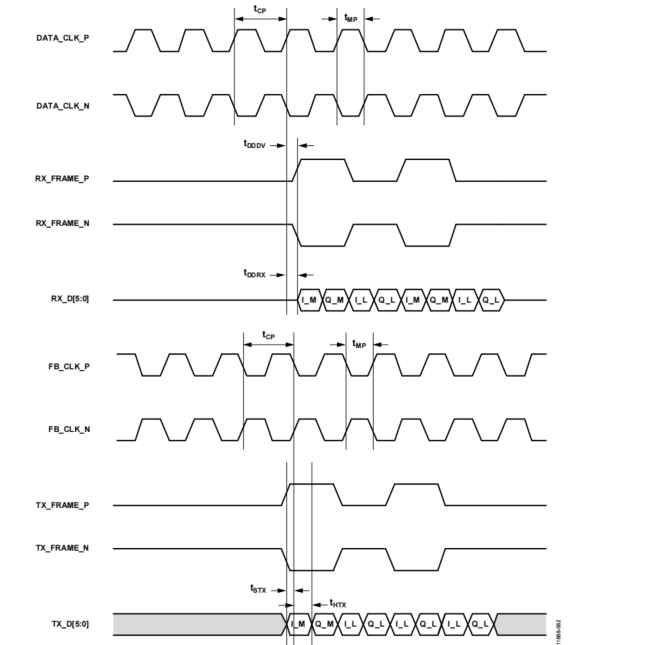

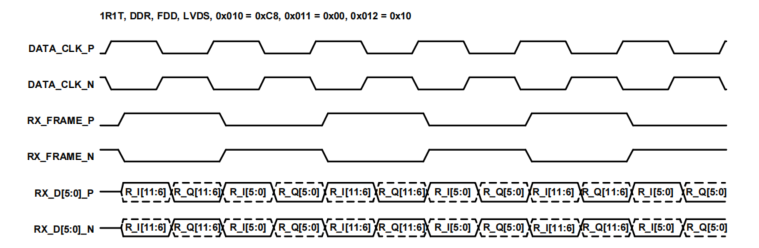

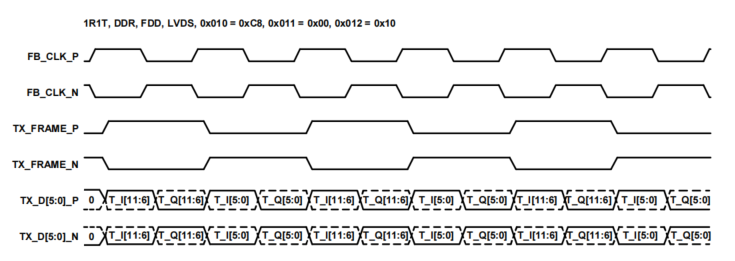

LVDS模式下1T1R时序如下图所示:

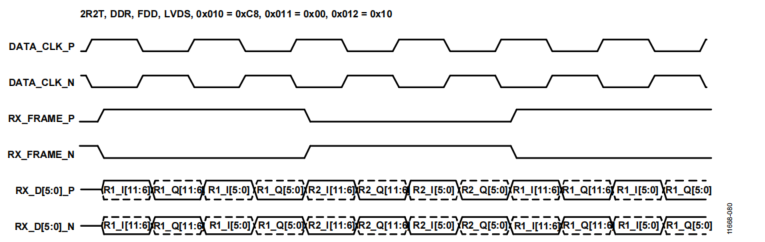

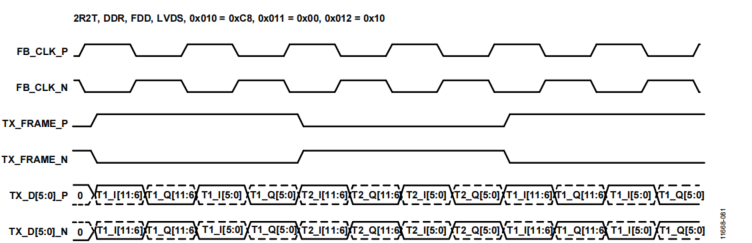

LVDS模式下2T2R的时序如下图所示:

LVDS时序参数: