给出部分对逻辑系统设计质量有影响的主要实际工程技术,包括逻辑系统稳 定性认识、逻辑系统中的竞争和冒险(俗称"毛刺问题")、程序的可读性和可扩展性设计、 Vivado工具常用辅助功能等内容进行介绍

目录

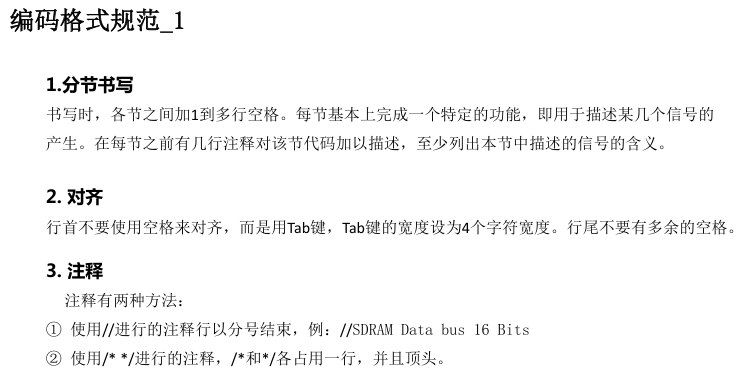

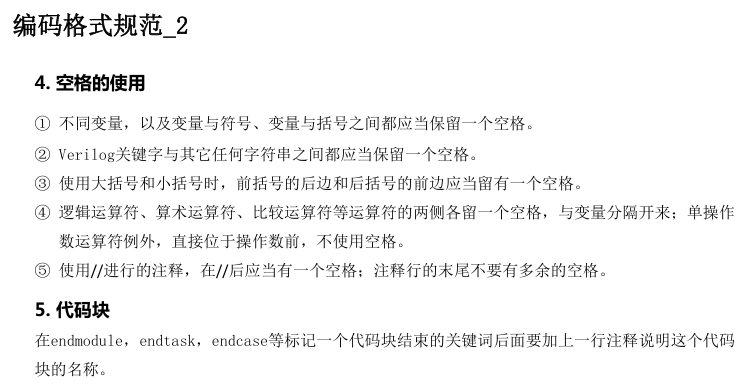

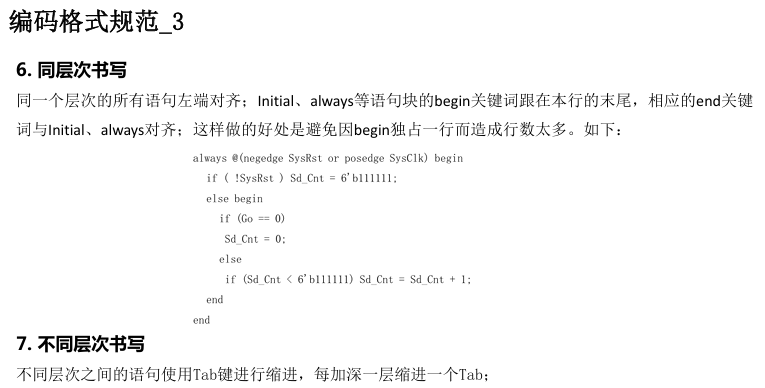

[Verilog HDL设计中的编码风格](#Verilog HDL设计中的编码风格)

数字电路稳定性

数字电路稳定性定义

系统稳定性:指当去掉系统干扰后,系统能以足够的精度恢复到初始平衡状态

系统可靠性:需要系统正常工作时候它能正常工作,可表达为时间的数字函数:R(t)=系统在时刻仍能正常工作的概率

数字系统的稳定性有很多影响因素。有时候,即使设计正确,该系统仍不能正常工作

影响因素:数字电路中的竞争与冒险、时间抖动(jitter)、亚稳态等因素都会影响数字系统的稳定性和可靠性

竞争与冒险

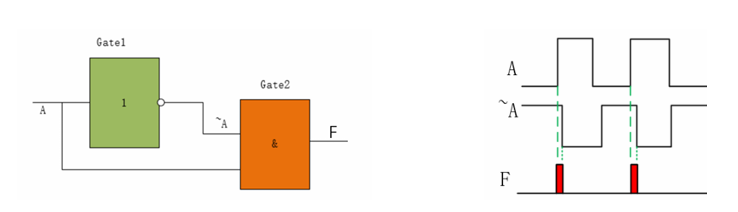

在逻辑电路中,某个输入变量或不同信号通过两条或两条以上的途径传到输出端,由于途径上的延迟时间不同,到达输出门的时间就有先有后,这种现象称为竞争,因此而导致输出干扰脉冲险象的现象称为冒险,如上图F产生"毛刺"

非临界竞争:不会产生错误输出的竞争现象;

临界竞争:产生暂时性的或永久性错误输出的竞争现象

时间抖动

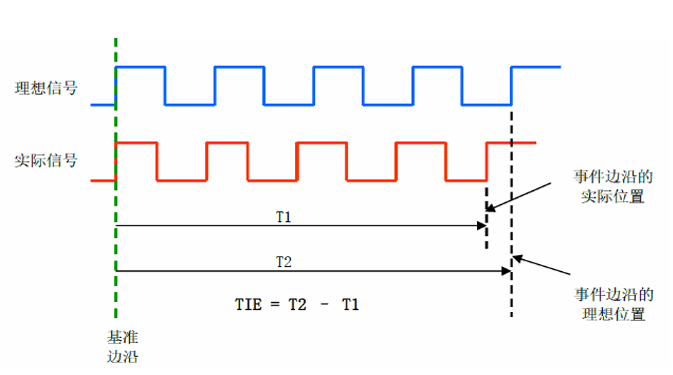

抖动:信号的定时事件与其理想位置之间的偏差

在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但是这种理想信号并不存在

实际的信号周期长度总会有一定差异,从而导致下一个沿的到来时间不确定,这种不确定就是抖动(jitter)

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少

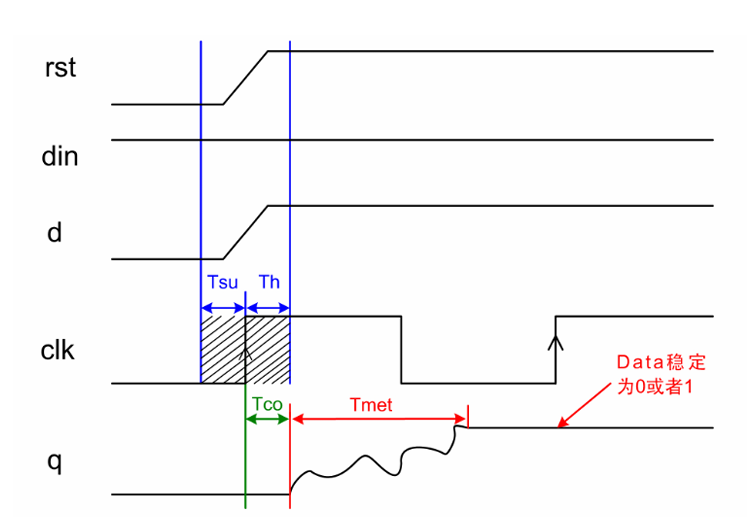

数字系统亚稳态

亚稳定状态:在同步系统中,如果触发器的建立时间和保持时间不满足,就可能进入亚稳态,此时触发器输出端Q在有效时钟沿之后比较长的一段时间处于状态1和状态0之间的不确定状态,即亚稳定状态

当其他门电路或触发器接收到亚稳定的输入信号之后,有些不见会把这个信号当成0,而另一些则把它当成1,还有一些部件本身也可能产生亚稳定的输出信号,从而导致电路工作出现稳定性错误

组合逻辑与毛刺

毛刺的产生

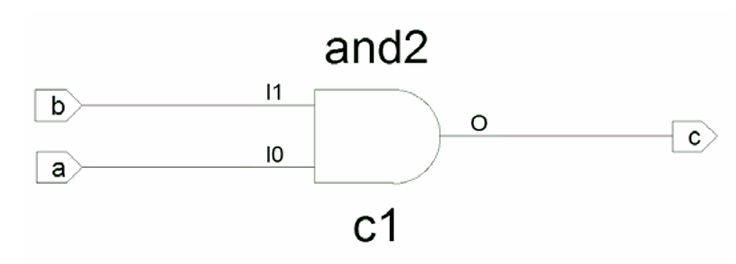

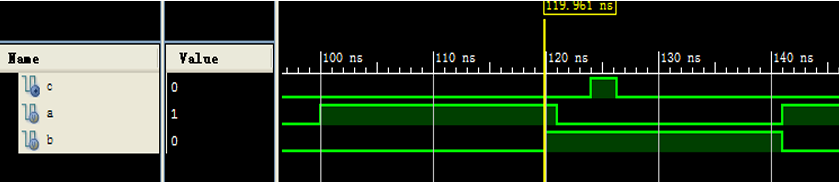

延时:信号在器件内部通过逻辑单元和连线时,都有一定的延时,分别称为器件延时和路径延时

用软件预估除a、b到c的两条最差路径的延时分别是7.567ns和5.436ns,这个总延时等于互连线路径延时加上与门的延时

由于延时的影响,加之高低电平转换也需要一定的过渡时间,在信号变化的瞬间,组合逻辑的输入信号并不是同时变化,由此往往会使得组合逻辑的输出出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"

a和b两条路径存在时间差,b比a提前2ns左右,因此虽然a、b两个信号只在1ns内为同高,但是c输出的高电平持续时间达到了2.2ns左右

毛刺的分类

按输出信号是否应该变化可分为静态险象和动态险象

静态险象:如果在输入变化而输出不应发生变化的情况下,输出端产生了短暂的错误输出,则称为静态险象

动态险象:如果在输入变化而输出应该发生变化的情况下,输出在比那花过程中产生了短暂的输出错误,则称为动态险象

按错误输出脉冲信号的极性可分为"0"型险象与"1"型险象"0"型险象:错误输出信号为负脉冲

"1"型险象:错误输出信号为正脉冲

按险象出现的原因可分为逻辑险象与功能险象逻辑险象:由于某个变量与其反变量作用时间不一致,出现瞬时同态造成的险象

功能险象:由于两个或两个以上输入信号同时变化时出现的险象

毛刺的处理

增加冗余项

增加冗余项的方法是:

1."或"上冗余的"与"项

2."与"上冗余的"或"项

可以消除可能产生的险象,但是此法只能用于消除逻辑险象,功能险象无法消除

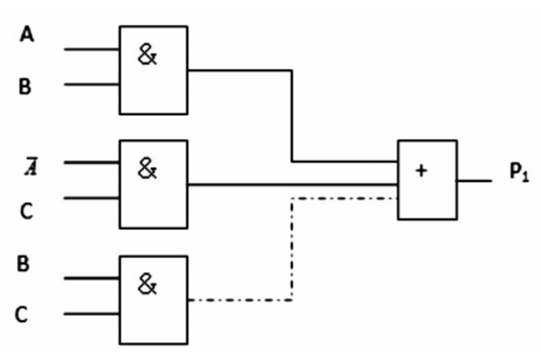

如图,在原来表达式基础上加上"B*C"项,可消除B=C=1所产生的冒险

module hazard_redundant(

input a, b, c,

output f

);

// 原逻辑:f = a&b + ~b&c

// 存在险象,增加冗余项 b&c

assign f = (a & b) | (~b & c) | (b & c);

endmodule增加小电容

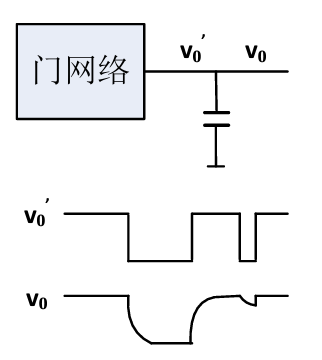

在组合逻辑芯片的管脚输出端增加小电容

由于竞争引起的险象都是一些频率很高的尖脉冲信号,在电路的输出端加一个小电容,如图所示,利用电容对电压变化延迟的特性来过滤掉宽度极窄的毛刺信号

但由于电容将使得输出波形的边沿加宽,降低了电路的速度

输出加小电容滤窄脉冲,FPGA 中用延迟 + 寄存器模拟

module hazard_cap_filter(

input clk,

input din,

output reg dout

);

reg din_r;

always @(posedge clk) begin

din_r <= din;

dout <= din_r; // 两级寄存器 = 等效滤波

end

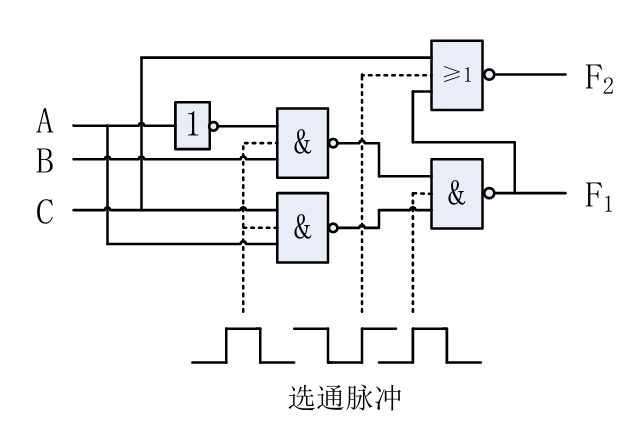

endmodule选通法

真正在设计中对于消除毛刺常用的是这个选通法。通过选通脉冲对电路的输出门加以控制,令选通脉冲在电路稳定后出现,可使输出避开险象脉冲,送出稳定输出信号

分类:对输入信号选通、对输出信号选通

采用此方法后,门网络的输出不再是连续的,它只在选通信号作用器件有效

如果选通信号采用系统全局的时钟,能够使得系统各部分同步工作

用时钟选通脉冲,只在稳定后输出

module hazard_gate(

input clk,

input din,

output reg dout

);

reg [1:0] sync;

always @(posedge clk) begin

sync <= {sync[0], din};

dout <= sync[1];

end

endmodule异步设计与毛刺

异步时序电路中的毛刺现象

当异步时序电路在态度瞬变期间,若存在多于一个的状态变量同时发生改变,则说此电路处于竞争之中

临界竞争:若电路所趋向的最终稳态与状态变量的变化次序有关,则此电路的竞争使临界的

非临界竞争:若电路所趋向的最终稳态与状态变量的变化次序无关,此电路的竞争是非临界的

如果异步时序电路存在临界竞争,输出状态会出现"毛刺"现象,影响电路的稳定性

异步时序电路中的毛刺的处理

延迟元件法(插入延迟避免竞争)

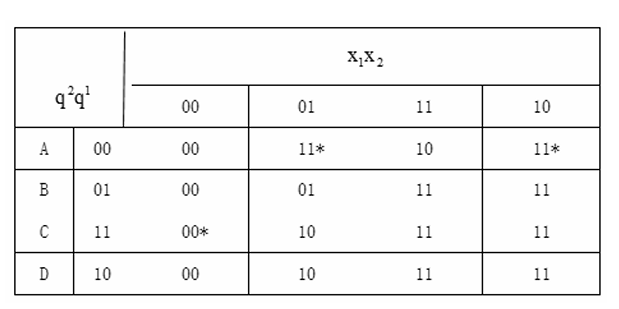

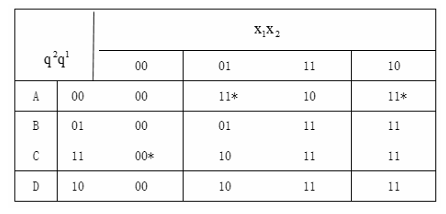

在输入信号(x1 x2)=(01)情况下,电路的状态从(q1 q2)=(00)到(11)的转换中含有临界竞争

通过对组合电路插入一个适当量的延迟,使q2值从0到1的变化总比q1从0到1的变化快,这样临界竞争就变成非临界竞争,从而得到正确的结果

module hazard_delay(

input x1, x2,

output q1, q2

);

assign #1 q1 = x1; // 延迟 1 单位

assign q2 = x2;

endmodule多次转换法(状态跳转避免竞争)

假定 (A→C)含有一个临界竞争,如果可以找到一个多次转换(A→D→C),那么,若能使D和A相邻,则用状 态D代替C后, 将消除转换中的临界竞争,并且维持"外部性能不变"

例如表中在(01)输入下,(11)与(10)有相同的次态且(11)与(10)相邻,则可用(10)代替(11),并不影响外 部性能,从而使存在临界竞争的转换(00) → (11) 变为无竞争的转换(00) →(10)

module hazard_safe_fsm(

input clk, rst_n,

input x1, x2,

output reg out

);

localparam A=2'b00, B=2'b01, C=2'b10, D=2'b11;

reg [1:0] curr, next;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) curr <= A;

else curr <= next;

end

always @(*) begin

case(curr)

A: next = (x1==0&&x2==1) ? D : A;

D: next = C;

C: next = C;

default: next = A;

endcase

end

assign out = (curr == C);

endmodule非临界竞争赋值法(状态编码安全)

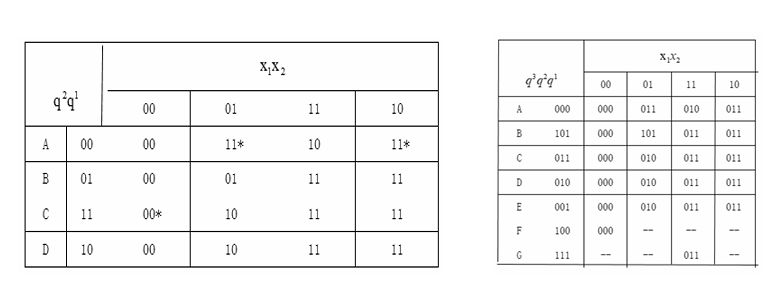

即允许状态编码有非临界竞争出现。例如左边表格中给定的四个状态, 利用临界竞争编码得到的编码表 如右边表格。当增加E、G、F三个新状态后,就可以使它们之间的竞争全部化为非临界竞争

module hazard_safe_code(

input clk, rst_n,

output reg [1:0] q

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

q <= 2'b00;

else

q <= q + 1'b1; // 顺序编码无竞争

end

endmodule同步电路改造法

同步电路优点:

a. 能够有效地避免毛刺的产生,提高设计的稳定性

b. 能够简化时序分析过程。同步电路便于电路错误分析,加快设计进度

c. 可以减少工作环境对设计的影响。同步电路受工作温度、电压等影响,器件时延变化小。对于时钟 和数据沿相对稳定的电路,时序要求较为宽松,因此对环境的依赖性较小

同步设计时钟信号的质量和稳定性决定了同步时序电路的性能,而在FPGA内部有专用的时钟资源,如全 局时钟布线资源、专用的时钟管理模块DUL、PLL等

同步设计时钟信号的质量和稳定性决定了同步时序电路的性能,而在FPGA内部有专用的时钟资源,如全 局时钟布线资源、专用的时钟管理模块DUL、PLL等

Verilog HDL设计中的编码风格

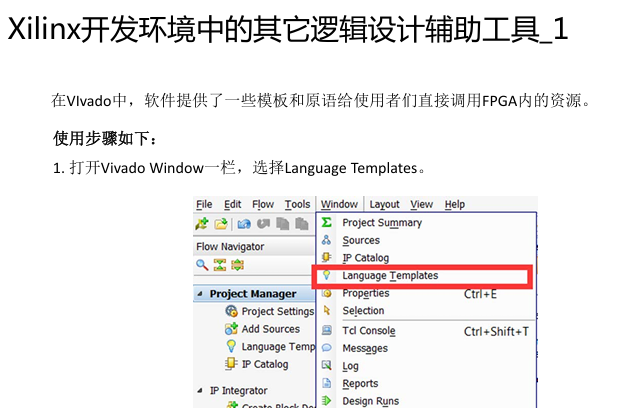

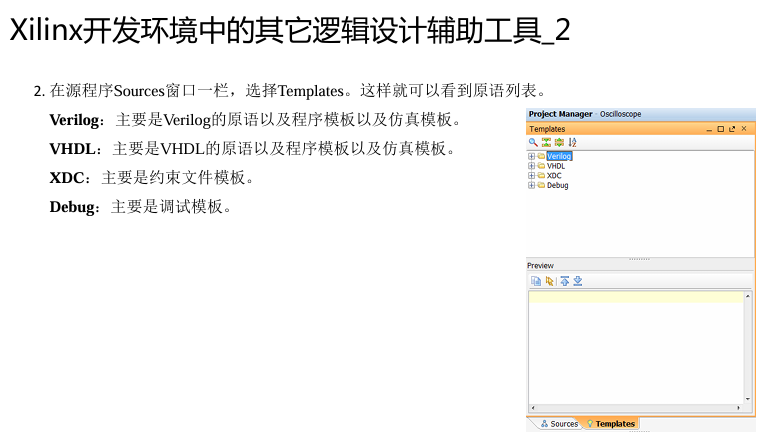

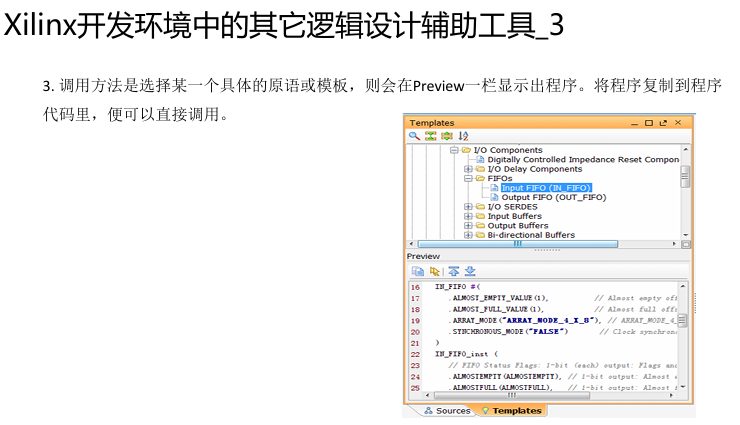

Xilinx开发环境中的其它逻辑设计辅助工具