目录

前言

一、底层架构类芯片

[1.1 ASIC(全定制专用芯片)](#1.1 ASIC(全定制专用芯片))

[1.2 ASSP(通用标准专用芯片)](#1.2 ASSP(通用标准专用芯片))

[1.3 FPGA(可编程逻辑芯片)](#1.3 FPGA(可编程逻辑芯片))

二、功能成品类芯片

[2.1 SoC(系统级芯片)](#2.1 SoC(系统级芯片))

[2.2 CPU(中央处理器)](#2.2 CPU(中央处理器))

[2.3 GPU(图形/并行处理器)](#2.3 GPU(图形/并行处理器))

[2.4 DPU(数据处理器)](#2.4 DPU(数据处理器))

[2.5 MCU(单片机/微控制器)](#2.5 MCU(单片机/微控制器))

三、核心芯片关键区分

[3.1 SoC与其他芯片的从属关系(结合Mac设备&传统电脑)](#3.1 SoC与其他芯片的从属关系(结合Mac设备&传统电脑))

[3.2 MCU与FPGA可编程的核心区别(重点,结合实际应用)](#3.2 MCU与FPGA可编程的核心区别(重点,结合实际应用))

[3.3 高端SoC内嵌eFPGA的详细说明(重点,结合行业案例)](#3.3 高端SoC内嵌eFPGA的详细说明(重点,结合行业案例))

[3.4 统一内存架构 vs 传统电脑架构(理解性能差异的关键)](#3.4 统一内存架构 vs 传统电脑架构(理解性能差异的关键))

四、本文结尾

五、更多操作

[📌 FPGA 与系统级开发](#📌 FPGA 与系统级开发)

[📌 前端工程化与可视化实践](#📌 前端工程化与可视化实践)

前言

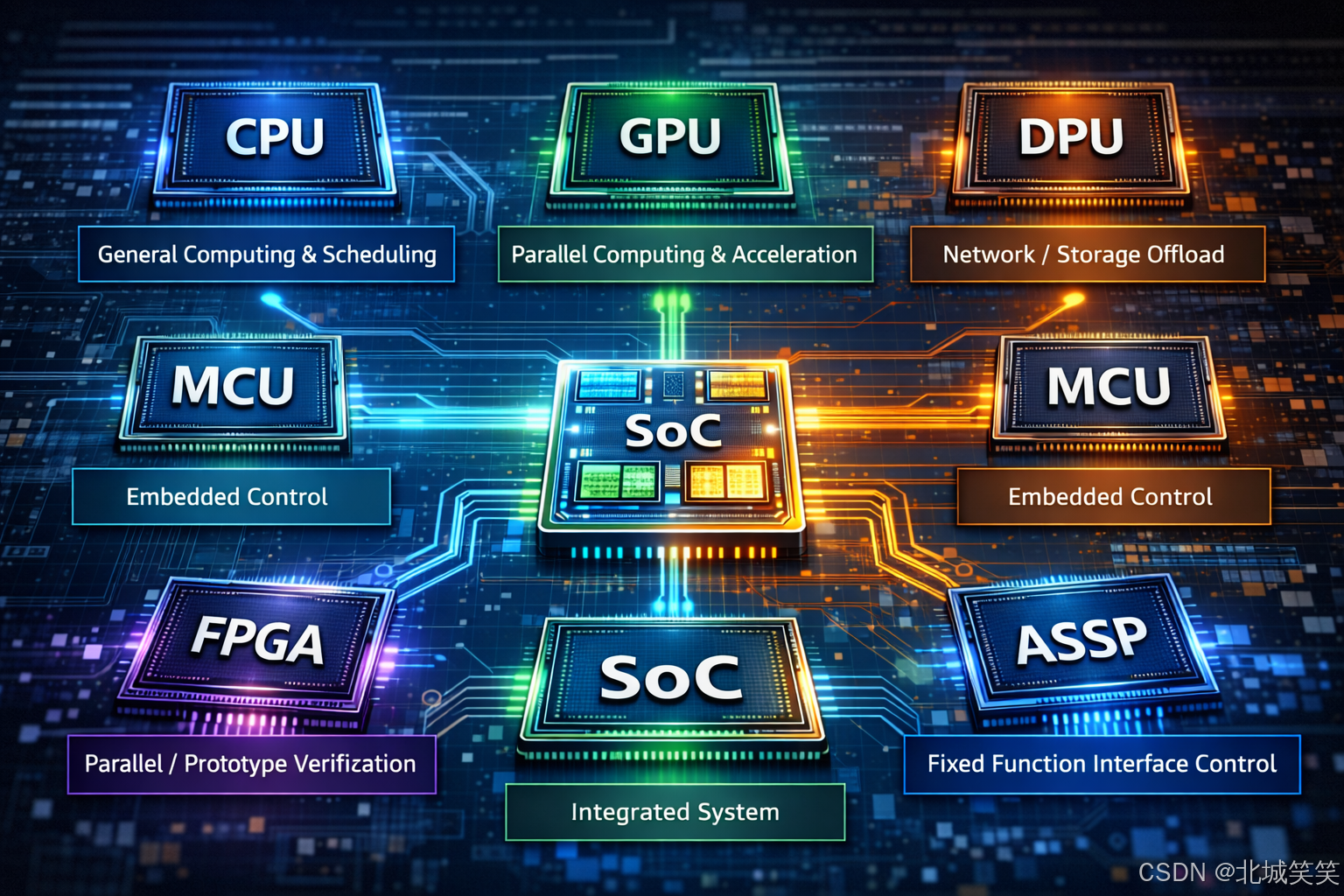

作为嵌入式或芯片研发从业者,日常工作中难免会接触到SoC、CPU、GPU、DPU、MCU、FPGA 等各类芯片,很多人容易混淆不同芯片的定位、特性及应用场景,尤其是MCU与FPGA的可编程差异 、高端SoC内嵌FPGA 的具体情况,更是高频疑问点。

而我们日常接触的消费级设备,比如苹果Mac mini 和Mac Studio ,其核心性能完全由SoC系统级芯片 (M4/M4 Pro/M4 Max/M4 Ultra)决定,这几款芯片不仅是SoC高度集成化 的典型代表,其研发过程更离不开FPGA 的原型验证支持。

本文将对主流芯片进行系统分类,详解各类芯片的核心特性与落地场景,

重点拆解MCU与FPGA的可编程区别 、高端SoC内嵌FPGA 的应用细节,同时融入Mac mini、Mac Studio 的实际案例,对比统一内存架构 与传统电脑 的差异,全程自然衔接FPGA 相关知识点,

内容精炼不啰嗦、兼顾专业性与实用性,助力大家快速理清芯片体系,提升选型与研发效率,避开常见认知误区。

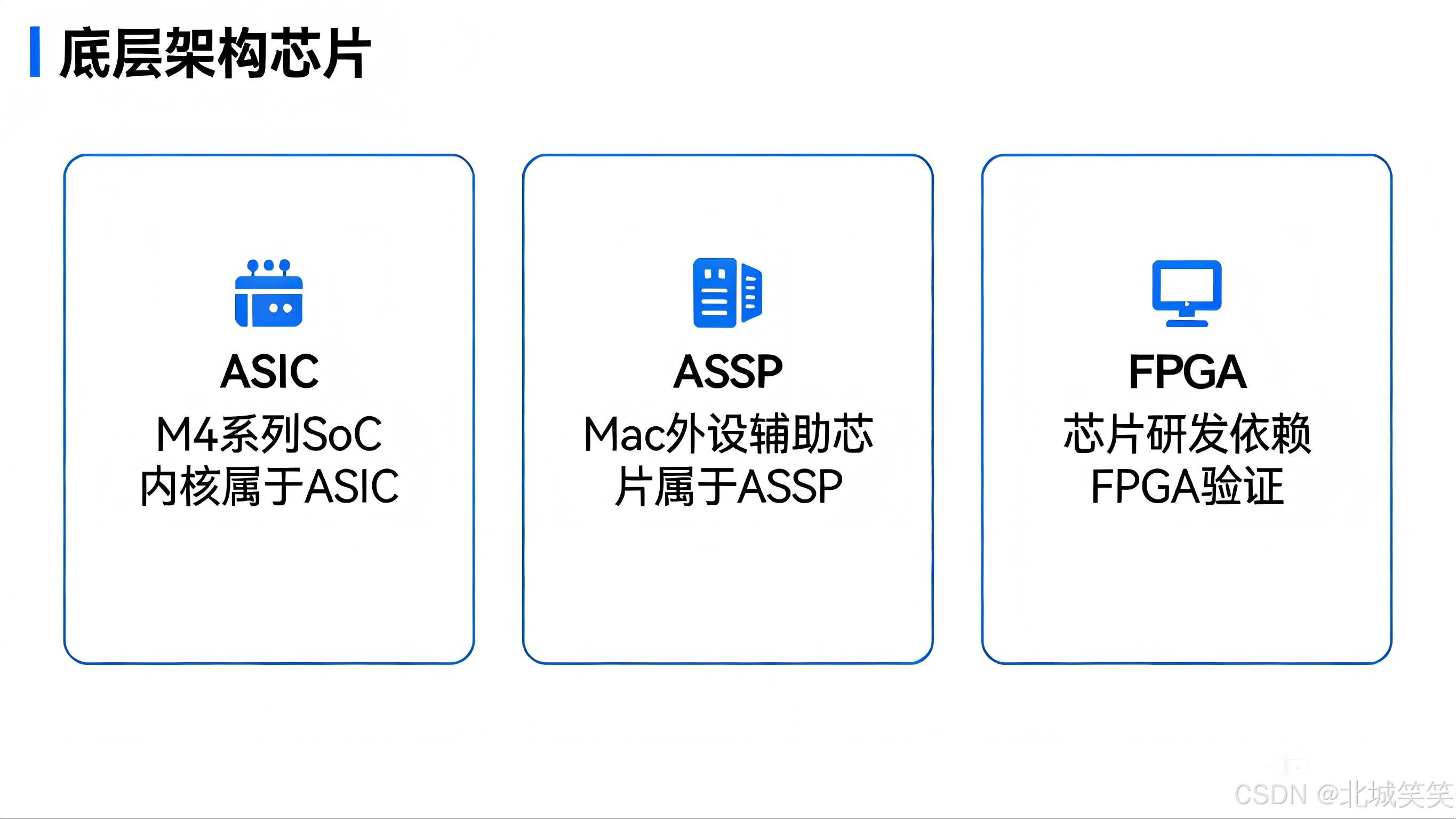

一、底层架构类芯片

底层架构类芯片(核心:硬固化/可编程特性)

底层架构类芯片决定了芯片的核心工作模式,核心区分在于功能是否可修改 ,主要分为硬固化专用芯片 和可编程逻辑芯片 两大类,是所有终端芯片的基础,也是Mac mini、Mac Studio 核心SoC(M4系列)研发的底层支撑,而FPGA 则是这类芯片研发过程中不可或缺的验证工具。

1.1 ASIC(全定制专用芯片)

ASIC ,即全定制专用集成电路 ,核心是"为单一客户、单一专属功能量身定制",属于硬固化芯片 ,逻辑一旦设计流片完成,无法修改 ,完全贴合特定场景的极致需求。

- 核心特性:独家定制 、无通用性、硬逻辑固化 ,研发成本极高(先进工艺流片动辄千万级),但量产成本低,性能和功耗可做到极致优化,适配专属场景的特殊需求。

- 应用场景:最典型的就是苹果M4/M4 Pro/M4 Max/M4 Ultra 系列SoC,其内部的CPU、GPU、NPU 等所有核心模块,均为ASIC定制硬核 ------比如M4 Ultra的双芯片融合架构、M4 Pro的GPU核心扩展,都是为苹果桌面设备(Mac mini、Mac Studio)量身定制的ASIC设计;此外,军工/航天专属控制芯片、企业私密加密模块、高端AI芯片的定制加速核,也属于ASIC,仅服务于单一客户或单一产品,不对外公开售卖。

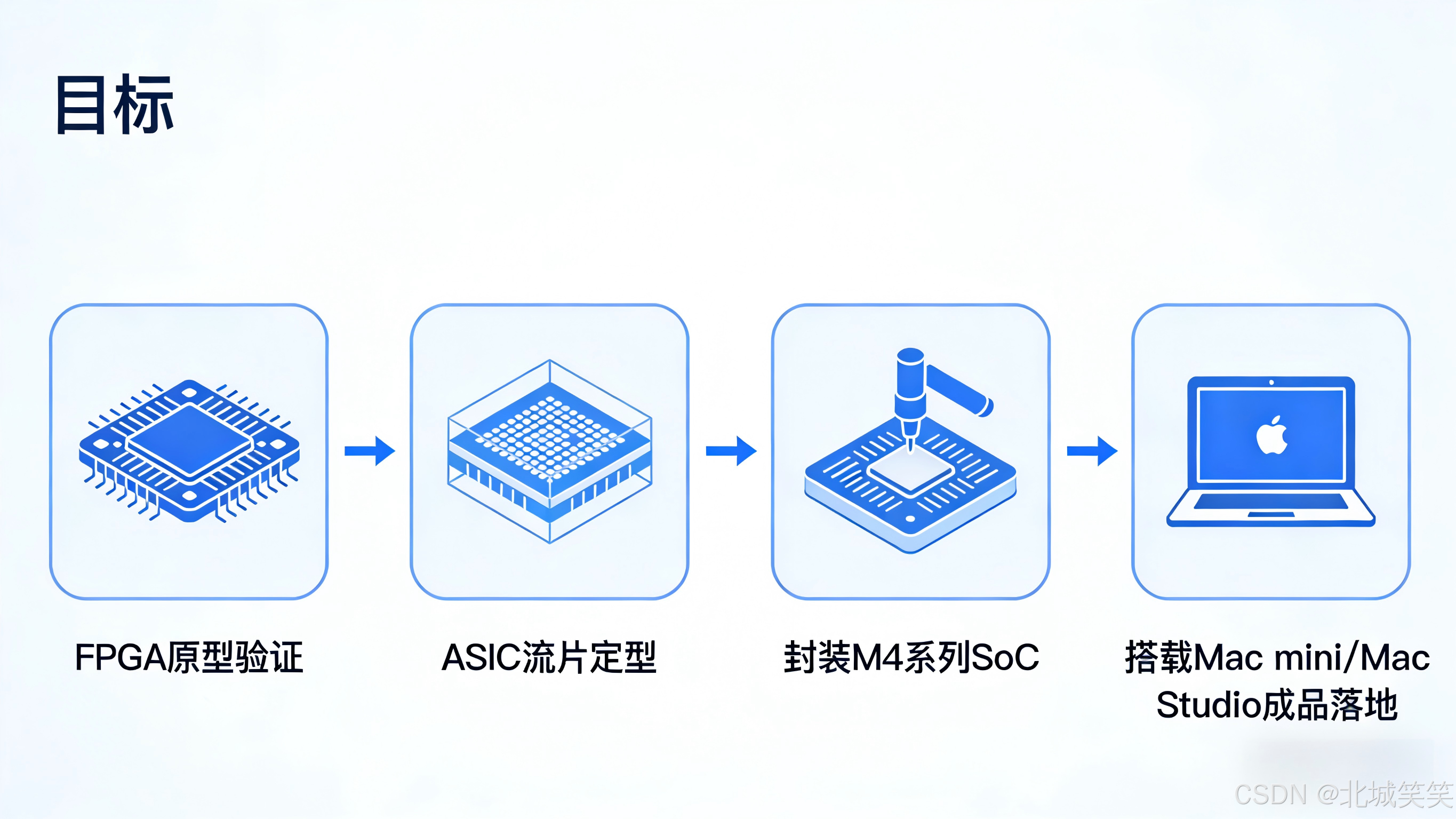

这类定制化ASIC硬核(尤其是M4系列SoC的复杂架构),在流片前必须通过FPGA搭建原型,验证CPU/GPU核心逻辑、时序兼容性、接口通断,避免流片失败,降低试错成本------苹果在研发M4 Ultra的UltraFusion互连技术时,就是通过FPGA验证双芯片协同的稳定性,确保其性能翻倍且无兼容性问题。

1.2 ASSP(通用标准专用芯片)

ASSP ,即通用标准专用芯片 ,同样属于硬固化芯片 ,与ASIC 的核心区别的是标准化、通用化 ,针对某一类通用固定功能设计,公开可采购,无需客户定制,适配全行业通用场景。

- 核心特性:标准化量产 、功能固定 、公开供货 ,研发成本由厂商分摊,单颗成本可控,无需客户投入研发,拿来即可集成使用,无法修改功能。

- 应用场景:各类电子设备的外设控制芯片 ,比如Mac mini、Mac Studio 主板上的雷电控制器 、网口PHY芯片 、音频编解码芯片(Codec) 、电源管理PMIC,这些都是ASSP芯片------它们并非苹果定制,而是行业通用的标准化产品,所有品牌均可采购使用,与Mac mini、Mac Studio内部的M系列SoC(ASIC)形成互补,负责外设接口、电源管理等辅助功能。

ASSP芯片虽功能固定,但研发阶段同样需要FPGA验证其协议兼容性(比如雷电控制器的高速信号传输、网口芯片的通信逻辑),确保其能与M系列SoC顺畅协同,避免出现接口不兼容、信号不稳定的问题。

ASIC 与 ASSP 的关系:

ASIC(专用集成电路)是为特定需求定制的芯片大类,而 ASSP(专用标准产品)可以看作是 ASIC 的一个"标准化子集"------同样面向某一类专用功能,但以通用产品形式批量销售、可被不同厂商直接复用。也就是说:ASSP 属于 ASIC 的一种形态(标准化专用),而 ASIC 还包括完全定制、不可通用的专有芯片 。

1.3 FPGA(可编程逻辑芯片)

FPGA ,即现场可编程门阵列 ,属于可编程芯片 ,核心是硬件可重构 ,内部由大量可编程逻辑门、布线和寄存器构成,可通过Verilog/VHDL 重构底层硬件电路,支持反复擦写、修改逻辑 ,具备全并行运算能力 和精准时序控制。

核心特性:硬件可编程 、全并行执行 、时序精准(纳秒级) 、可反复重构,开发门槛高(需掌握数字电路、时序分析),单颗成本高于MCU,灵活性极强,可适配多场景需求。

FPGA 属于可编程逻辑器件(PLD),本质是基于超大规模集成电路 (VLSI)的可重构数字芯片,属于数字集成电路和通用集成电路。

应用场景:

- ① 芯片研发核心环节:M4/M4 Pro/M4 Max/M4 Ultra系列SoC、CPU、GPU流片前的原型验证(这是FPGA最核心的应用之一,苹果研发M系列芯片时,通过FPGA搭建与最终SoC功能一致的原型,测试CPU/GPU核心性能、统一内存架构的效率,修复逻辑漏洞);

- ② 工业/通信领域:高速信号处理、雷达控制、高频交易、光纤通信;

- ③ AI/边缘计算:视频并行解码、边缘AI加速;

- ④ 高端特种SoC 内嵌(eFPGA ),实现灵活适配,无需外接独立FPGA 芯片(目前M系列SoC暂未内嵌eFPGA,但其研发依赖独立FPGA板卡)。

虽然Mac mini、Mac Studio的量产整机中没有FPGA芯片,但它们的核心M系列SoC能实现稳定、高性能的表现,离不开FPGA在研发阶段的验证------可以说,没有FPGA的原型验证,就没有M4系列SoC的一次流片成功,更没有Mac设备的流畅体验。

二、功能成品类芯片

功能成品类芯片(核心:终端算力/控制落地)

功能成品类芯片是基于底层架构芯片集成或单独设计,直接用于终端设备,聚焦算力输出 或逻辑控制 ,是我们日常接触最多的芯片类型,直接决定设备的核心性能。其中,SoC系统级芯片 是Mac mini、Mac Studio 的核心,而CPU、GPU 则是SoC的核心组成部分,它们的性能表现、架构设计,直接决定了两款Mac设备的定位差异,而这一切的研发过程,都与FPGA紧密相关。

2.1 SoC (系统级芯片)

SoC ,即系统级芯片 ,核心是高度集成 ,将CPU 、GPU 、NPU 、接口控制器等多个功能模块(本质是多个ASIC 硬核)封装在一颗芯片内,实现"单芯片搞定核心系统",本质是一颗超大号的ASIC 。苹果M4系列芯片(M4/M4 Pro/M4 Max/M4 Ultra),就是SoC的标杆产品,分别搭载在Mac mini 和Mac Studio 上,支撑不同场景的性能需求。

- 核心特性:超高集成度 、低功耗 、小型化 ,一站式提供核心算力和接口,无需外接过多芯片,简化终端设备的主板设计,兼顾性能与体积;其中,统一内存架构 是M系列SoC的核心优势------与传统电脑的"CPU独立内存+GPU独立显存"设计不同,M系列SoC的CPU、GPU、NPU共享同一内存池,数据无需在不同内存间传输,大幅降低延迟、提升效率,这也是Mac设备流畅度优于传统电脑的关键原因之一。

- 应用场景:消费电子(Mac mini 搭载M4/M4 Pro SoC、Mac Studio 搭载M4 Max/M4 Ultra SoC,苹果M系列 、手机骁龙/天玑芯片 )、车规主控芯片 、机顶盒、DPU核心芯片、嵌入式终端主控,是目前小型智能设备的核心芯片。

不同M系列SoC的差异与设备适配:

- M4 SoC:入门级SoC,集成10核CPU、10核GPU,120GB/s内存带宽,适配Mac mini基础款,满足日常办公、轻度创作需求;

- M4 Pro SoC:中端SoC,12核CPU、20核GPU,200GB/s内存带宽,适配Mac mini高配款,应对中度创作、开发测试需求;

- M4 Max SoC:高端SoC,14核CPU、32核GPU,410GB/s内存带宽,适配Mac Studio基础款,满足专业视频剪辑、3D建模需求;

- M4 Ultra SoC:旗舰级SoC,通过UltraFusion互连技术将两颗M4 Max融合,24核CPU、64核GPU,820GB/s内存带宽,适配Mac Studio高配款,应对8K视频渲染、AI模型训练等重度专业需求。

部分流程:

M系列SoC作为高度集成的ASIC,其复杂的统一内存架构、CPU/GPU核心扩展、UltraFusion互连技术,在研发阶段均需通过FPGA进行原型验证------比如验证统一内存的带宽效率、双芯片融合的协同稳定性,确保流片后能适配Mac mini、Mac Studio的不同性能需求,避免出现算力浪费、兼容性问题。

👉 SoC 是 ASIC 的一种复杂形态,而不是简单等同。

2.2 CPU(中央处理器)

CPU ,即中央处理器 ,是通用串行计算核心 ,基于冯·诺依曼架构,具备全能调度能力,循序执行各类系统指令和软件任务,是电子设备的大脑 ,可独立存在(传统电脑的独立CPU),也可作为SoC 的内部模块(M系列SoC的CPU核心)。

- 核心特性:通用化 、串行运算 、调度能力强,适配各类软件,擅长复杂的通用计算和任务调度,无需依赖其他芯片即可完成核心运算,但单独使用时需搭配主板、内存等外设;传统电脑的CPU多为独立芯片(如Intel i5/i7、AMD Ryzen),需搭配独立内存、显卡,而M系列SoC的CPU核心是ASIC化的定制硬核,与GPU、内存控制器集成在同一芯片上,效率更高、功耗更低。

- 应用场景:传统电脑(台式机/笔记本)的独立CPU、服务器 、Mac mini、Mac Studio的M系列SoC主核、嵌入式终端,负责办公、系统运行、通用数据运算,是所有通用计算设备的核心;其中,Mac mini的M4 CPU(10核)适合日常办公,Mac Studio的M4 Ultra CPU(24核)适合多任务并行、高性能计算。

无论是传统电脑的独立CPU,还是M系列SoC的CPU核心,在研发阶段都需要FPGA验证其逻辑正确性、时序稳定性------比如验证CPU的指令执行效率、多核心协同能力,确保其能稳定运行各类软件,避免出现卡顿、崩溃问题;尤其是M4 Ultra的16性能核+8能效核架构,通过FPGA验证不同核心的调度逻辑,实现性能与功耗的平衡。

2.3 GPU(图形/并行处理器)

GPU ,即图形处理器 ,核心是多核心并行 ,最初设计用于图形渲染,后因并行运算优势,广泛应用于AI加速、科学计算等场景,可独立存在(传统电脑的独立显卡),也可集成在SoC 内(M系列SoC的GPU核心)。

- 核心特性:多核心并行 、图形处理能力强、浮点运算高效 ,擅长批量数据并行处理,不擅长复杂的串行逻辑调度,需配合CPU 使用,发挥并行算力优势;传统电脑的独立GPU(如NVIDIA RTX系列、AMD RX系列)有独立显存,与CPU、内存独立工作,数据传输延迟较高;而M系列SoC的GPU核心是ASIC化的定制硬核,共享统一内存,数据传输效率远超传统电脑,这也是Mac Studio能流畅处理8K视频、3D渲染的核心原因。

- 应用场景:传统电脑的独立显卡用于游戏、图形设计;Mac mini 的M4/M4 Pro GPU(10核/20核)适合照片编辑、短视频剪辑;Mac Studio的M4 Max/M4 Ultra GPU(32核/64核)适合8K视频剪辑、3D动画渲染、AI训练与推理、超算、三维仿真,是图形处理和并行运算的核心芯片。

GPU的并行运算逻辑、图形渲染引擎,在研发阶段需通过FPGA验证------比如验证GPU核心的并行处理效率、光线追踪逻辑,确保其能流畅处理复杂图形任务;M系列SoC的GPU核心(尤其是M4 Ultra的64核GPU),通过FPGA验证多核心并行的稳定性,避免出现渲染卡顿、画质异常等问题,同时优化与统一内存的协同效率。

2.4 DPU(数据处理器)

DPU ,即数据处理器 ,专门用于卸载CPU的数据处理负载 ,聚焦网络转发、存储管理、安全加密等数据相关任务,本质是一款专用SoC ,内部集成ASIC 硬核,是数据中心的核心芯片。

- 核心特性:专用数据处理 、高带宽 、低延迟 ,可大幅卸载CPU 的负担,专注于数据相关的高速处理,避免CPU被海量数据占用,提升整体系统效率;与M系列SoC类似,DPU也采用高度集成的ASIC架构,部分高端DPU会内嵌eFPGA,实现灵活适配不同通信协议。

- 应用场景:云计算数据中心 、服务器机房、5G基站、分布式存储系统、高端网络设备,主要用于数据转发、存储优化、安全加密等场景;虽然Mac mini、Mac Studio未搭载独立DPU,但M系列SoC内部的接口控制器、网络模块,具备部分DPU的基础功能,可满足日常数据传输需求。

DPU的研发与M系列SoC类似,其内部ASIC硬核的逻辑验证、高速接口的兼容性测试,均需通过FPGA完成;内嵌eFPGA的高端DPU,可通过FPGA的可编程特性,灵活适配不同场景的数据流调度,提升数据处理效率。

2.5 MCU (单片机/微控制器)

MCU ,即微控制器(单片机) ,属于软件可编程芯片 ,内部集成小型CPU 、闪存、内存和I/O接口,通过**软件代码(C/汇编)**修改逻辑,实现简单的控制功能,成本低、功耗低 ,是嵌入式控制的核心。

- 核心特性:软件可编程 、低成本 、低功耗 、开发门槛低,擅长低速逻辑控制,无需复杂的外设搭配,接上电源即可实现简单控制,功能灵活可修改,但性能有限;与M系列SoC、FPGA相比,MCU性能较弱,无法承担高性能计算任务。

- 应用场景:家用家电(空调、电饭煲、洗衣机)、智能硬件(智能门锁 、传感器、遥控器)、小型工控设备(红绿灯、继电器、串口采集模块),适合低成本、低功耗、简单控制的场景;需要注意的是,Mac mini、Mac Studio 这类高性能桌面设备,核心依赖M系列SoC(ASIC),整机中没有MCU,其外设的简单控制的功能,由SoC内部的I/O控制器(ASIC硬核)或外接的ASSP芯片实现。

MCU和FPGA均为可编程芯片 ,但定位差异极大------MCU侧重低速软件控制,FPGA侧重高速硬件并行;在部分复杂设备中,FPGA可与MCU协同工作(FPGA负责高速信号处理,MCU负责简单控制),但在Mac设备中,两者均不直接存在,仅FPGA在M系列SoC研发阶段发挥核心作用。

ASSP 与 MCU 的场景区别:

ASSP 通常承担"固定功能模块"的角色,例如接口控制(USB/雷电)、音频编解码、网络 PHY、电源管理等,功能高度专一、无需用户编程,更多作为主系统(SoC/CPU)的配套芯片存在;

而 MCU 是"可编程控制核心",通过 C/C++ 等软件实现逻辑控制,适用于设备控制、状态管理、简单计算等场景。

简单理解:

👉 ASSP 是"拿来即用的功能模块",MCU 是"可编程的小控制器"。

三、核心芯片关键区分

核心芯片从属关系&关键区分(避坑重点)

这一部分重点解决大家的高频疑问,明确各类芯片的从属关系、核心差异,尤其是MCU与FPGA的可编程区别 、高端SoC内嵌FPGA 的细节,同时结合Mac mini、Mac Studio、M系列SoC、传统电脑的实际案例,厘清芯片体系,助力大家精准选型、避开认知误区,全程自然衔接FPGA相关知识点。

3.1 SoC与其他芯片的从属关系(结合Mac设备&传统电脑)

- SoC的本质是超大号ASIC :苹果M4/M4 Pro/M4 Max/M4 Ultra系列SoC,本质就是高度集成的ASIC,内部集成的CPU、GPU、NPU等所有功能模块,均为ASIC硬逻辑硬核,逻辑固定,无法修改,核心优势是集成化、低功耗;这与传统电脑的"独立CPU+独立GPU+独立内存"架构完全不同------传统电脑的CPU、GPU是独立芯片,需搭配多个ASSP芯片(如内存控制器、接口芯片),体积大、功耗高,而M系列SoC将所有核心模块集成在一颗芯片上,实现了体积与性能的平衡,这也是Mac mini小巧便携、Mac Studio性能强劲的核心原因。

- ASSP与SoC完全互斥 :ASSP是标准化通用芯片,永远是主板外接的独立芯片,无法集成到SoC内部(两者定位不同:SoC是定制集成,ASSP是通用外设);比如Mac mini、Mac Studio的雷电控制器、网口PHY芯片、电源管理PMIC,都是外接的ASSP芯片,与内部的M系列SoC(ASIC)协同工作,负责外设接口、电源管理等辅助功能;传统电脑的内存控制器、声卡、网卡,也多为ASSP芯片。

- CPU、GPU的两种存在形式 :CPU、GPU可作为独立芯片存在(如传统电脑的Intel i7 CPU、NVIDIA RTX 4090 GPU),也可作为SoC的内部模块集成(如M系列SoC的CPU、GPU核心);前者灵活性高,可单独升级,但效率低、功耗高;后者集成度高,效率高、功耗低,但无法单独升级------这也是Mac设备(Mac mini、Mac Studio)内存、存储均为板载,无法后期升级的原因(M系列SoC的统一内存架构,内存与SoC封装在一起)。

- SoC与FPGA的关联 :普通消费级SoC(苹果M4系列、手机骁龙芯片)内部无FPGA;仅高端特种SoC会内嵌eFPGA(嵌入式FPGA),普通民用场景几乎见不到;但无论是M系列SoC,还是传统电脑的独立CPU/GPU,其研发阶段都离不开FPGA的原型验证------FPGA是芯片研发的"试金石",确保芯片逻辑正确、性能稳定,避免流片失败。

3.2 MCU 与FPGA可编程的核心区别(重点,结合实际应用)

MCU 和FPGA 均为可编程芯片,可修改功能,但两者的可编程方式、底层逻辑、应用场景天差地别,也是从业者最易混淆的点,结合Mac设备、传统电脑的案例,拆解如下:

- 编程方式(核心差异) :MCU 是软件可编程 ,通过编写C语言、汇编语言等软件代码,控制内部小型CPU执行指令,实现逻辑控制,本质是修改软件逻辑 ,无需改动硬件结构;比如智能门锁的MCU,通过修改代码即可调整解锁方式;FPGA 是硬件可编程 ,通过Verilog/VHDL 等硬件描述语言,搭建底层硬件逻辑门、布线和寄存器,本质是修改硬件电路结构,可反复擦写重构,相当于"现场搭建专属芯片";比如苹果研发M4 Ultra时,通过FPGA搭建双芯片融合的硬件逻辑,验证UltraFusion互连技术的可行性。

- 底层架构 :MCU 内部是CPU+闪存+内存+I/O 的通用架构,依赖软件调度,核心是软件驱动硬件 ;FPGA 内部是大量可编程逻辑门、触发器和布线资源,无固定CPU,核心是硬件直接实现功能,无需软件调度------这也是FPGA比MCU运算速度快、时序更精准的原因。

- 执行逻辑 :MCU 是串行执行 ,指令按顺序依次运行,适合低速控制,存在软件调度延迟;FPGA 是全并行执行 ,多个逻辑模块同时工作,无调度延迟,时序精准(纳秒级) ,适合高速、多任务并行处理;比如M系列SoC的GPU核心(ASIC),其并行运算逻辑就是通过FPGA验证的,确保能同时处理大量图形数据,无卡顿。

- 开发门槛与成本 :MCU 开发门槛低,无需掌握数字电路知识,单颗成本极低(几元到几十元),适合批量低成本场景,是嵌入式入门的首选;FPGA 开发门槛高,需精通数字电路、时序分析、硬件描述语言,单颗成本高(几十元到上千元),开发人力成本也高,适合高端高速场景------比如苹果研发M系列SoC,需要专业的FPGA开发团队,验证芯片的复杂逻辑。

- 应用场景差异 :MCU 侧重低速控制 ,主打简单、低成本,比如家电控制、传感器采集,与Mac设备、传统电脑的核心算力需求无关;FPGA 侧重高速并行、芯片原型验证、特种硬件加速 ,主打高性能、高实时性,比如M系列SoC的研发验证、传统电脑独立GPU的逻辑验证、数据中心的高速信号处理。

3.3 高端SoC 内嵌eFPGA的详细说明(重点,结合行业案例)

普通消费级SoC (如苹果M4系列、手机骁龙芯片)内部无FPGA ,但高端特种SoC (军工、通信、高端AI服务器领域)会内嵌eFPGA(嵌入式FPGA),这也是SoC与FPGA结合的重要形式,虽然Mac设备暂未采用,但与M系列SoC的研发逻辑相通:

- 什么是eFPGA :嵌入式FPGA 是将一小块可编程FPGA 逻辑阵列,集成到SoC 芯片内部,并非独立FPGA 芯片,是SoC 的一个功能模块,逻辑规模更小,仅满足定向可编程需求;与M系列SoC的ASIC硬核不同,eFPGA可通过硬件描述语言修改逻辑,实现灵活适配。

- 内嵌eFPGA 的核心目的:兼顾ASIC的高性能、低功耗 优势,和FPGA的可编程灵活性 ,解决传统SoC 硬逻辑固化、无法适配多协议的痛点,缩小板卡体积、降低功耗成本;比如高端AI服务器SoC,通过eFPGA灵活调整AI加速逻辑,适配不同的AI算法,这与苹果M系列SoC为不同Mac设备(Mac mini、Mac Studio)定制ASIC硬核的思路一致,都是"精准适配场景需求"。

- 核心特性:集成化 、小型化 、硬件可编程 、低延迟高带宽 ,可与SoC 内CPU/GPU 协同工作;与独立FPGA相比,eFPGA体积更小、功耗更低,与SoC内部模块的协同效率更高,适合对体积和功耗有要求的高端场景。

- 应用场景:仅限高端特种领域------军工主控SoC 、通信设备SoC 、高端AI服务器SoC 、定制车规SoC;虽然Mac mini、Mac Studio的M系列SoC未内嵌eFPGA,但苹果未来可能会在高端Mac Studio的SoC中引入eFPGA,提升设备的灵活性,适配更多专业创作场景。

- 典型案例:Xilinx Speedcore eFPGA IP、华为昇腾高端AI SoC 、Intel服务器级SoC ,均搭载eFPGA 实现灵活硬件加速;这些SoC的研发过程,同样需要独立FPGA板卡进行原型验证,与M系列SoC的研发逻辑完全一致。

3.4 统一内存架构 vs 传统电脑架构(理解性能差异的关键)

统一内存架构(UMA) 是以苹果 M 系列 SoC 为代表的核心设计理念,也是 Mac mini、Mac Studio 性能与功耗表现突出的底层原因之一。其本质是将 CPU、GPU、NPU 等所有计算单元共享同一块物理内存,通过 SoC 内部的高带宽总线直接访问数据;这与传统电脑"CPU 使用系统内存 + GPU 使用独立显存"的分离架构形成鲜明对比。

统一内存架构(以 M 系列 SoC 为例):

在苹果 M4 / M4 Pro / M4 Max / M4 Ultra 等 SoC 中,内存并非独立插在主板上,而是与 SoC 封装在同一基板(甚至同一封装内),形成"片上统一内存"。CPU、GPU、NPU 访问的是同一份数据,无需数据在不同内存之间来回复制,这种设计带来了三个核心优势:

- 零拷贝(Zero-Copy):CPU 处理的数据可直接被 GPU/NPU 使用,无需额外搬运

- 极高带宽:Max / Ultra 芯片可达数百 GB/s,远高于普通 DDR 内存

- 低延迟与低功耗:减少总线通信与数据搬运开销

这也是为什么 Mac Studio 在视频剪辑、AI 推理、图形处理等场景中表现极其高效的根本原因。

传统电脑架构(x86 平台):

传统电脑采用的是"分离式架构":CPU 使用主板上的 DDR 内存,GPU 使用独立显卡上的 GDDR 显存,两者之间通过 PCIe 总线通信。这种架构的特点是:

- 硬件可独立升级(CPU、GPU、内存可分别更换)

- 生态成熟、扩展性强

但也存在明显问题:

- 数据拷贝开销大(CPU → GPU 需要显式传输)

- 带宽受限于 PCIe(远低于片上互连)

- 功耗较高、延迟更大

例如在视频渲染或 AI 计算中,CPU 将数据传输给 GPU 时,会产生明显的性能损耗,而这在统一内存架构中是不存在的。

本质差异总结(避坑重点):

- M 系列 SoC:计算单元共享内存 → 高效率、低功耗、强协同,但不可 升级 / 拆装

- 传统电脑:计算单元独立内存 → 灵活可扩展,但存在性能损耗

与芯片体系的关联:

统一内存架构本质上是 SoC 高度集成(ASIC 化)的进一步体现,与前文提到的"CPU/GPU 作为 SoC 内部模块"是同一设计逻辑的延伸;而传统电脑的分离架构,则对应"CPU/GPU 独立芯片 + 多个 ASSP 外设"的体系。

这也进一步说明:

👉 Mac mini / Mac Studio 的性能优势,并不仅来自芯片算力本身,更来自整体架构设计(SoC + UMA)的协同优化。

**⭐另外,**MCU(Microcontroller Unit)与 SoC(System on Chip)本质上都是高度集成的芯片,但定位差异明显:

MCU 更偏向"嵌入式控制核心",内部集成简单 CPU、少量内存与外设接口,通常运行 C/C++ 等软件程序,侧重低功耗、低成本与实时控制,广泛用于家电、汽车电子、物联网设备;

而 SoC 则是"完整计算系统的芯片化",将 CPU、GPU、NPU、内存控制器及多种功能模块高度集成在一颗芯片中(如 Apple M4),强调高性能与系统级协同,应用于手机、PC(如 Mac mini、Mac Studio)、服务器等复杂计算场景。

简单来说:

MCU 是做控制的"微型大脑",SoC 是做计算的"完整系统"。

四、本文结尾

以上就是CPU 、GPU 、DPU 、MCU 、ASIC 、ASSP 、SoC 、FPGA 八大核心芯片的分类、特性与落地场景,同时结合Mac mini、Mac Studio 的实际案例,详解了M4/M4 Pro/M4 Max/M4 Ultra系列SoC的差异、统一内存架构 与传统电脑架构的区别。无论是苹果M系列SoC的成功,还是传统电脑独立CPU/GPU的稳定运行,都离不开FPGA的原型验证支持。

实际研发选型牢记:

- 通用计算与系统调度选 CPU;

- 大规模并行计算(AI / 图形)选 GPU;

- 数据中心网络与存储卸载选 DPU;

- 低成本控制选 MCU;

- 固定功能接口与外设控制选 ASSP(如网卡 PHY、雷电控制器、电源管理等通用专用芯片);

- 高集成智能终端选 SoC (如 Apple M4 系列,应用于 Mac mini、Mac Studio,本质为超大规模 ASIC 集成系统)。

- 高速并行与芯片原型验证选 FPGA;

实际研发选型的本质,是在 性能、功耗、成本与灵活性之间进行工程权衡;不同芯片形态(CPU / GPU / DPU / MCU / ASSP / SoC / FPGA)并无绝对优劣,关键在于是否匹配具体场景。理解各类芯片的 架构边界及其协同方式,才是系统级设计能力的核心。

以 Apple M 系列 SoC 为代表的统一内存架构 ,正是"多计算单元高度融合与协同 "的典型,其性能优势来源于系统级架构设计,而非单一芯片算力本身。

欢迎评论区交流FPGA开发 、芯片选型 、eFPGA工程落地 ,以及Mac设备SoC架构相关问题。

五、更多操作

本文围绕八大主流芯片 的分类差异,结合苹果 M4 系列 与 Mac 设备案例,厘清MCU 与 FPGA 可编程区别 、eFPGA 应用逻辑,梳理芯片选型核心,帮从业者理清体系、避坑提效。

如果你希望进一步深入这一方向,下面这些内容可以作为延伸阅读:

📌 FPGA 与系统级开发

FPGA 专栏![]() https://blog.csdn.net/weixin_65793170/category_12665249.html

https://blog.csdn.net/weixin_65793170/category_12665249.html

FPGA 系列,文章目录(总览)

FPGA系列,文章目录![]() https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502

https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502

内容涵盖:

- FPGA 基础与进阶

- 高速接口(PCIe / Ethernet)

- 数据流处理架构

- 硬件与上层系统协同设计

👉 适合想深入"算力侧与系统底层"的读者

如果你正在做:

- 实时数据系统

- 数字孪生 / 可视化平台

- FPGA + Web 系统集成

也欢迎留言交流,一起探讨"如何把算力真正变成系统能力"。

📌 前端工程化与可视化实践

Vue Develop 实战专栏![]() https://blog.csdn.net/weixin_65793170/category_12116741.html

https://blog.csdn.net/weixin_65793170/category_12116741.html

持续更新内容包括:

- Vue2 / Vue3 工程实践

- 实时通信(WebSocket)

- 数据可视化(ECharts / WebGL)

- 性能优化与复杂系统前端架构

👉 适合想从"前端开发"走向"系统交互与可视化层"的同学

如果本文对你有帮助,欢迎:👍 点赞 | ⭐ 收藏 | 💬 评论