4.11 OTHER TOPICS IN TEST GENERATION

4.11.1 Test Set Compaction(测试集压缩)

通过ATPG产生的向量可能太多了,所以要想办法减少向量,有两种测试集压缩的形式:

- 静态的Static compaction:就是结合或者移除一些多余的向量。有两种方式:

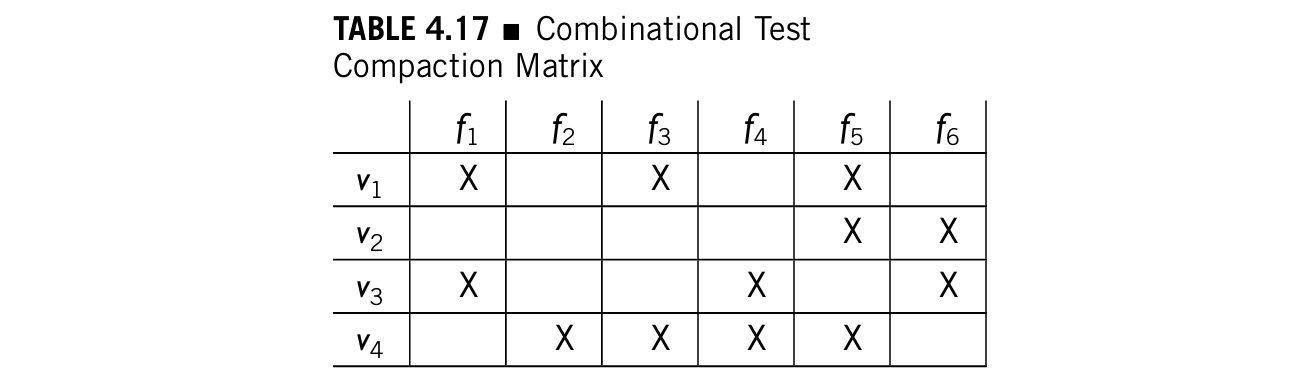

- covering algorithm:用一个矩阵,行代表向量,列代表对应能检测的故障,以下图为例:

例如v2就是没必要的,因为它能检测出来的故障别的向量也能检测出来,v4就是必须的,因为它有别的向量检测不出来的故障。

例如v2就是没必要的,因为它能检测出来的故障别的向量也能检测出来,v4就是必须的,因为它有别的向量检测不出来的故障。 - 找到兼容的向量,比如11X1和X101用其中一个就够了

- covering algorithm:用一个矩阵,行代表向量,列代表对应能检测的故障,以下图为例:

- 动态的Dynamic compaction:被集成在了ATPG的过程中,生成的向量都是能尽量多地检查出故障的向量。intelligently fill in the "don't care" bits in the vectors:例如检测故障fi用1x10x就行,两个bit不用指定,反而能检测出更多故障。

针对时序逻辑电路的测试集压缩更复杂,因为去掉一个向量或者序列必须要用fault simulation验证以保证故障覆盖率不受损失。

4.11.2 N -Detect ATPG

为了提升测试集的质量,人们考虑用针对不同故障的不同测试集去检测故障,但是这需要multiple ATPG engines,每个engine都需要不同的fault model,虽然在理论上这是可行的,但是实际是不可实现的。

所以又想到替代的办法,就是生成一个向量,可以在给定fault model的每个故障下用一个测试集测试多次。n-detect test set的规模是和n成正比的。

4.11.3 ATPG for Acyclic Sequential Circuits(无环时序逻辑电路的ATPG)

无环的时序电路可以按照time frame展开成组合逻辑电路进行ATPG。

4.11.4 IDDQ Testing

不同于之前讨论的测试方法,之前都是测试电压,IDDQ是测试电流。

一个good chip的电流有个期待值,defective chip的电流可能会大很多。

IDDQ测试有两个点:

- 因为电流测量比电压测量慢,所以需要的向量更少

- 电流测试中要处理好噪声,以保证测试质量

4.11.5 Designing a High-Level ATPG

这个High-Level不是高水平,是高电路层级。

传统的方法是门级的ATPG,但是对于大规模集成电路而言还是不太能满足要求,为了提升性能考虑研究高层级的ATPG,但是基于VHDL等语言的涉及到一系列问题,所以有人提出用**finite state machine (FSM)**作为电路的表现形式,但也有一些缺陷。

所以高层级的APTG还是一大研究方向。书前面就说过,这里也说的比较简要。

4.12 CONCLUDING REMARKS

把这一张的内容记了一段流水账。