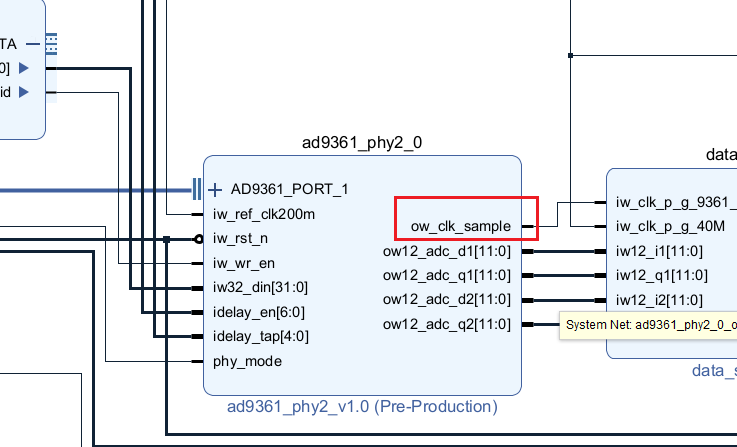

前一段时间在调AD9361时,采用9361出来的随路时钟ow_clk_sample(它是过了PLL出来的40MHz时钟),**用它来驱动后级电路时会出现部分电路无法正常工作,不出现ILA抓波形窗口,**为了方便我就将出来的数据全部进行了跨时钟域处理,全部改到晶振驱动的40MHz时钟下,波形窗口可正常工作。但采到的数据I,q都会有数据有时,但BPSK调制时,只调制了I路呀!问题未解决?怀疑板卡问题?

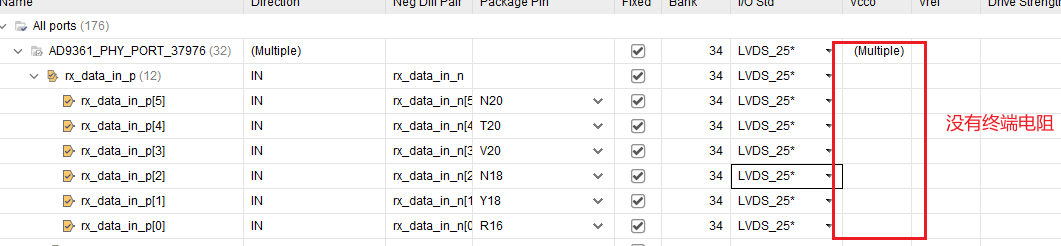

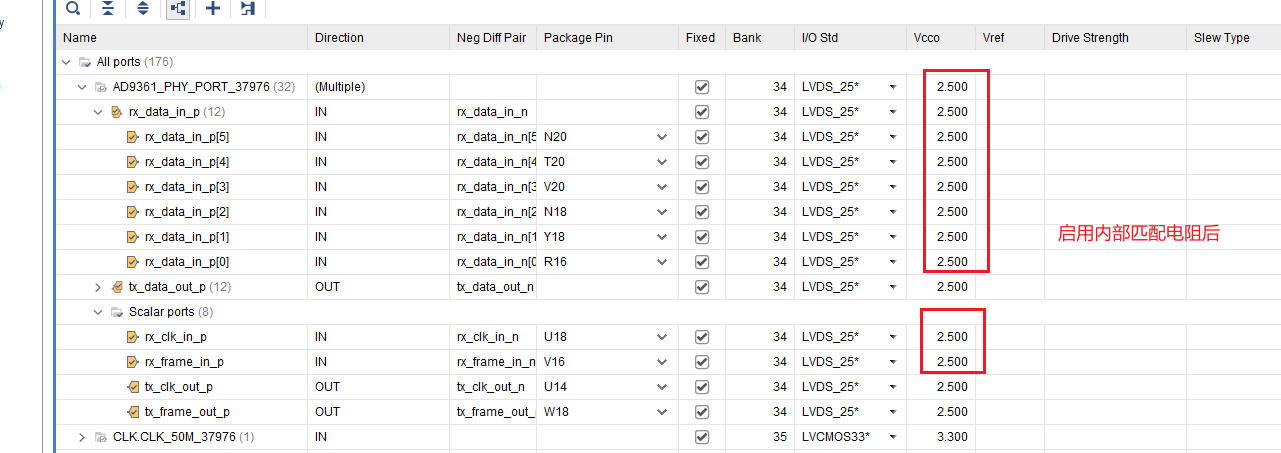

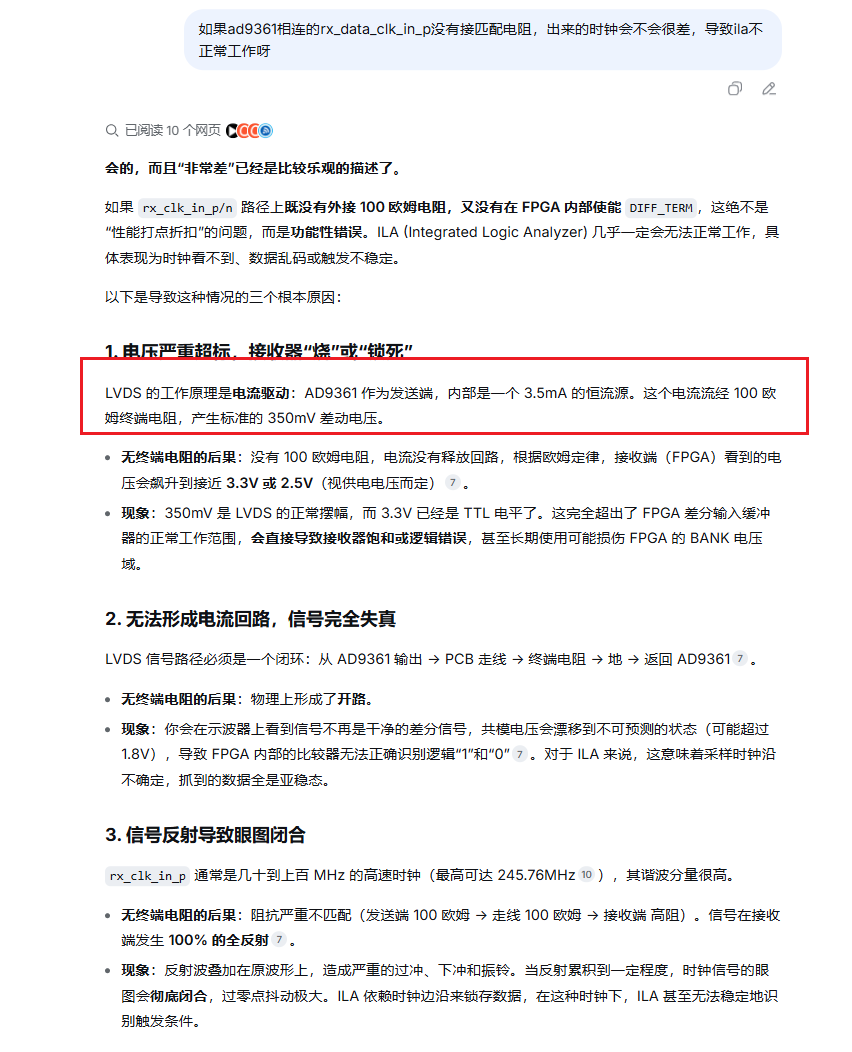

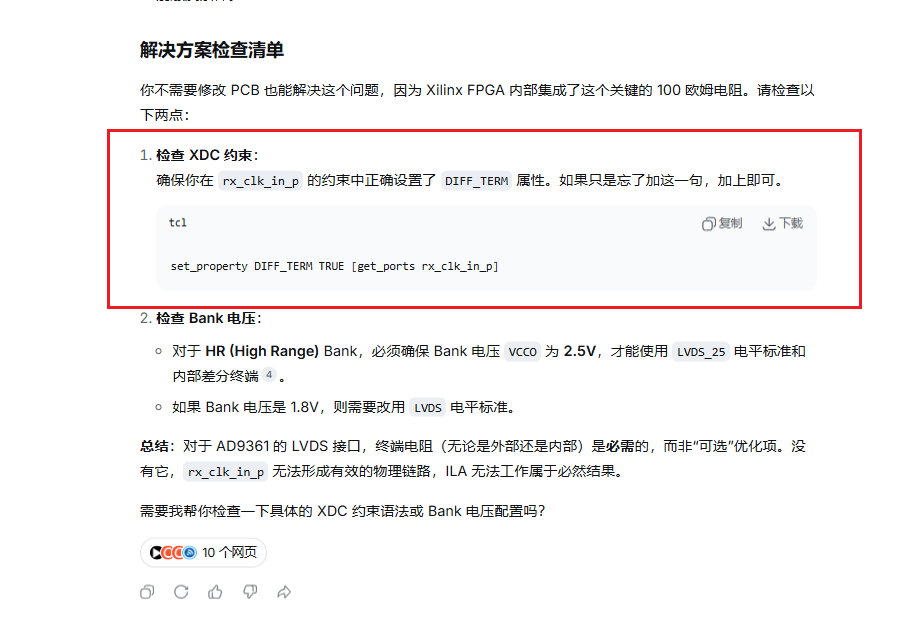

2026.04.16:我对比别的板卡引脚时发现如下问题:rx_clk_in_P相关的rx端都需要开启内部100Ω的匹配电阻,高速电路才能正常工作。修改后ILA出来了。

之前数据采样错误也可能是这个原因导致的。没有匹配电阻会导致数据采样异常。

不启用内部匹配电阻,rx相关的信号是没有VCCo 2.5这个值的。

set_property DIFF_TERM TRUE [get_ports rx_clk_in_p]

create_clock -period 12.500 -name rx_clk_in_p -waveform {0.000 6.250} [get_ports rx_clk_in_p]

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVDS_25 DIFF_TERM 1} [get_ports rx_clk_in_p]

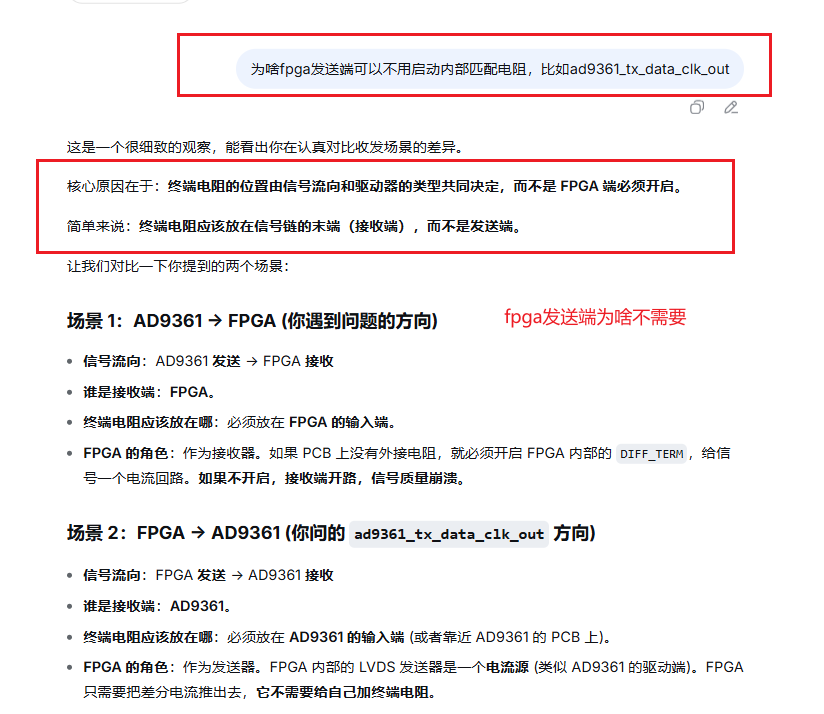

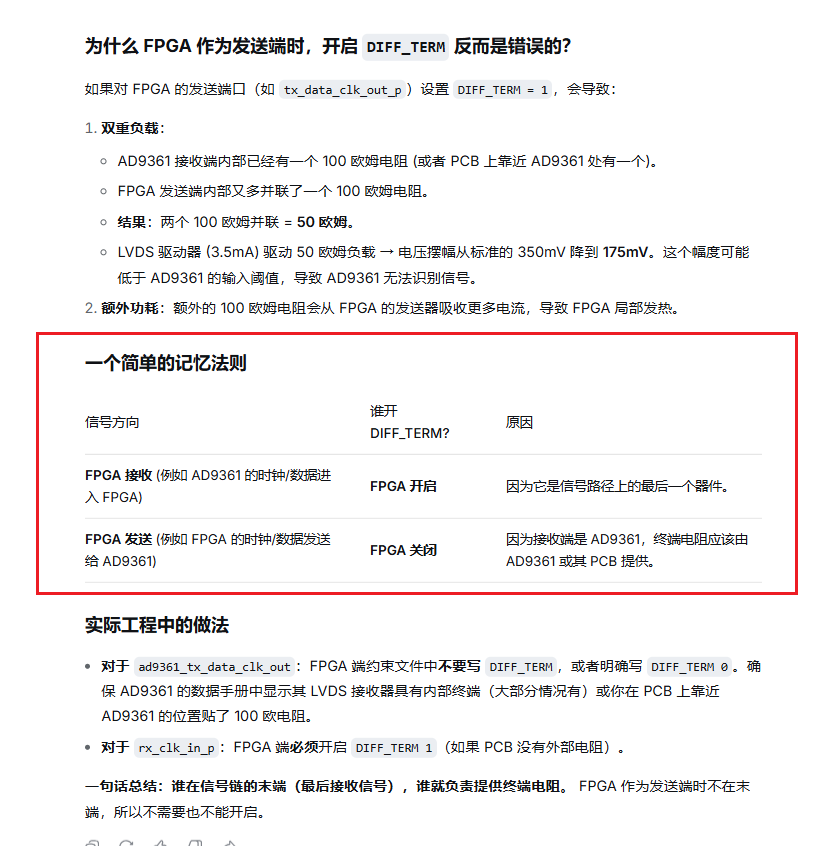

tx端不用启动匹配电阻tx端为啥不需要?

更换完成后,发现出来的随路时钟时有时无,通过计时器发现有时不计数,所以判断为板卡有问题。