把 MATLAB 算好的 UW 序列(通常是具有良好自相关性的 PN 码或 CAZAC 序列)保存为 .coe 文件,例化一个 Block RAM (BRAM) 作为 ROM。

1,什么是ROM?

**ROM(Read-Only Memory,只读存储器),**在FPGA里,ROM就是一个带编号的柜子

地址(Address):就是柜子编号。

数据(Data):就是柜子里的东西(要发送的UW数据)。

2,用MATLAB生成.coe文件

Vivado 里的 ROM 是空的,它需要一份"清单"告诉它每个抽屉里该装什么。这份清单的后缀名就叫 .coe (Coefficient File),.coe是Xilinx Vivado块存储器(BRAM)初始化文件格式。

先用MATLAB生成一个极其规律的"递增序列"作为测试用的UW,生成如下内容

memory_initialization_radix=16;

memory_initialization_vector=

00000000,

00010001,.............................................

007E007E,

007F007F;

3,在 Vivado 中召唤 ROM IP 核

3.1,打开 IP Catalog

3.2,搜索Block Memory Generator,它就是FPGA里面用来做RAM,ROM,FIFO的"万能存储器基石"。

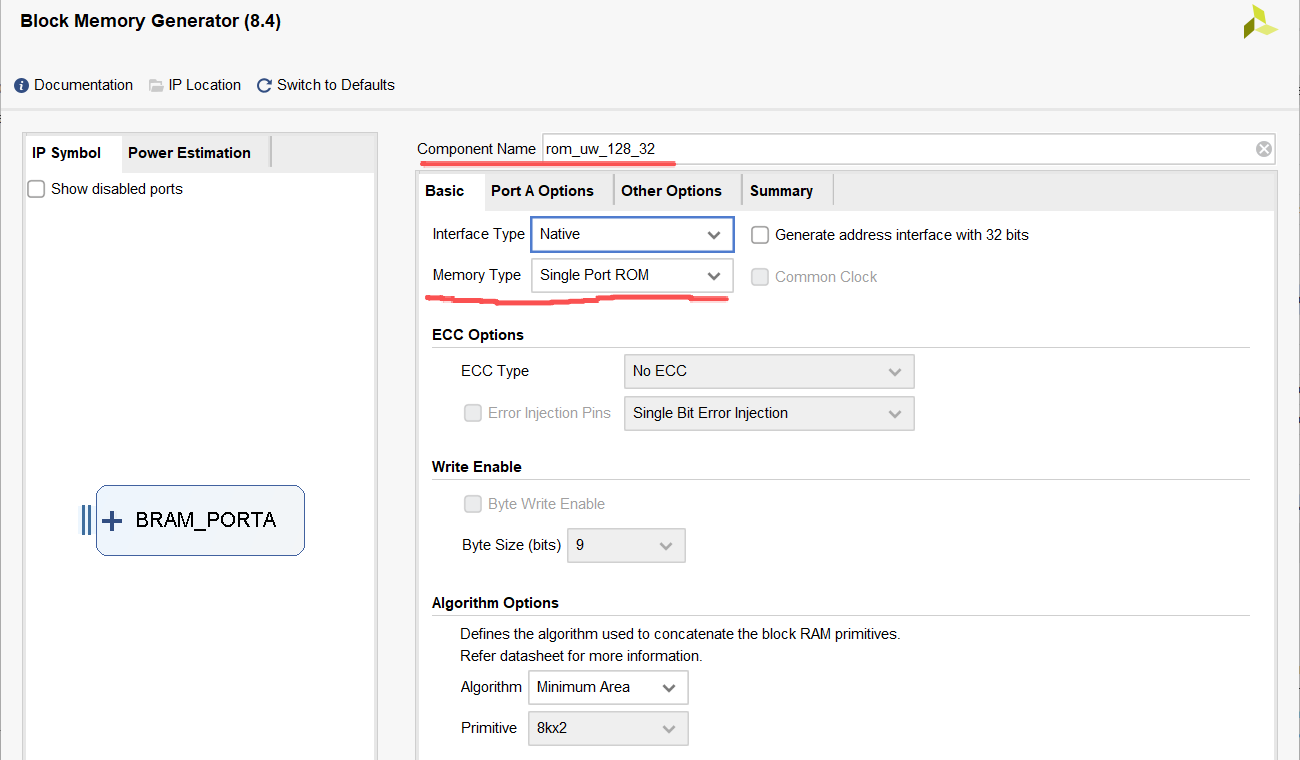

3.3,Basic (基础设置)

Component Name(命名):rom_uw_128_32(代表里面存的是UW,深度128,宽度32)。

Memory Type :选择 Single Port ROM(单端口只读存储器)。因为我们只需要读,不需要往里写数据,选单端口最省资源。

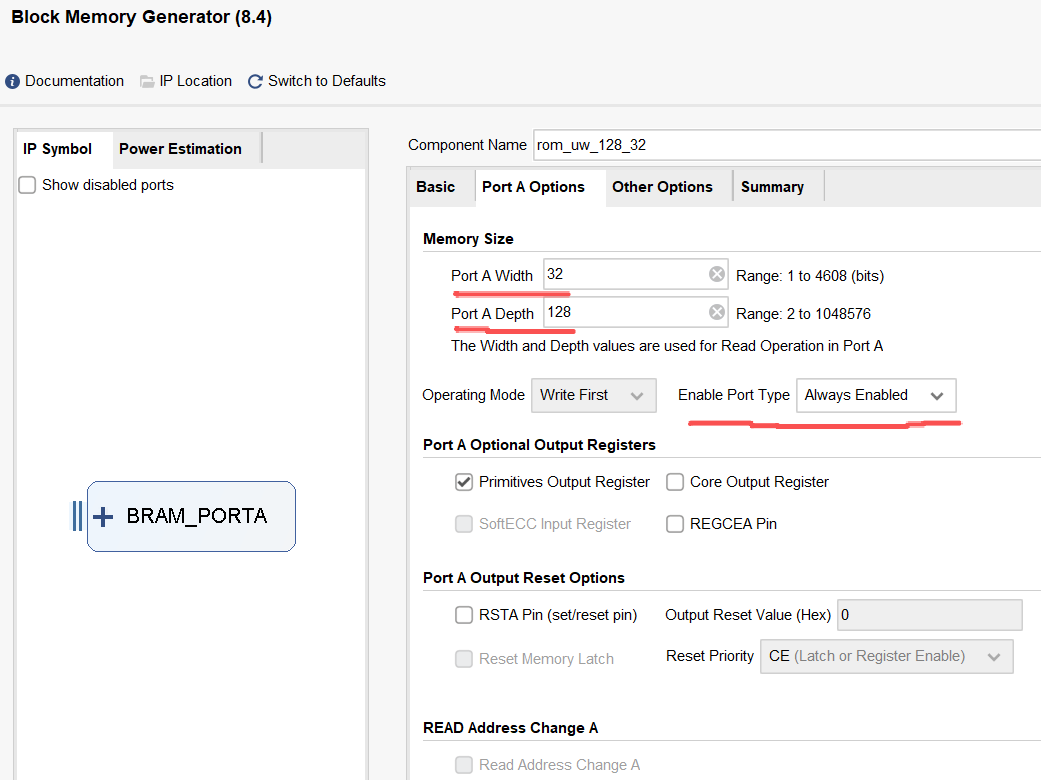

3.4,Port A Options (端口设置)

Port A Width :填 32(因为我们的 I 路和 Q 路拼起来是 32 位)

Port A Depth :填 128(因为你生成了 128 个 UW 数据)

Enable Port Type :选择 Always Enabled(让它一直开着,省得我们再去写一个使能信号控制它)。

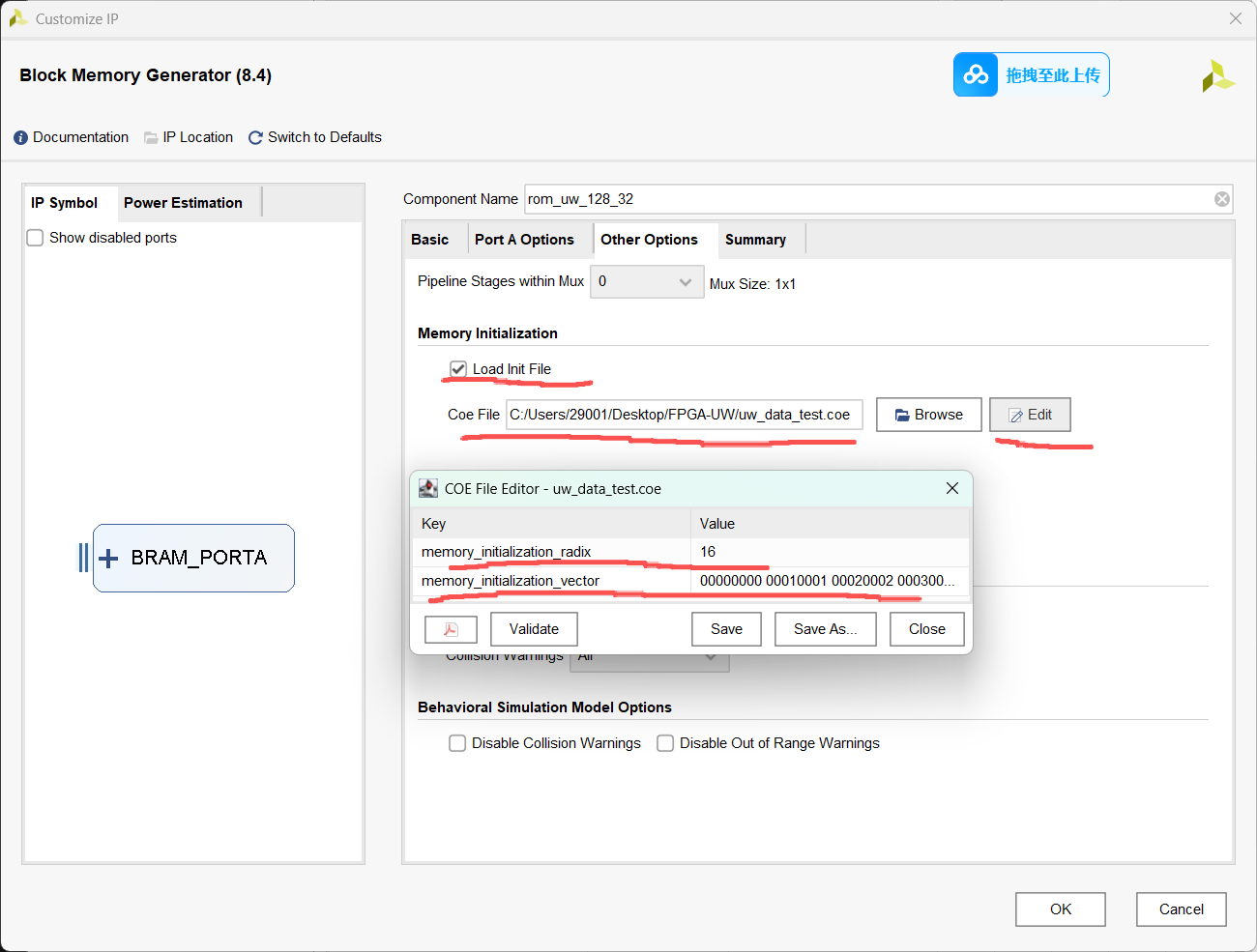

3.5,Other Options (极其关键:加载 COE 文件)

找到 Memory Initialization ,勾选 Load Init File。

点击后面的 Browse 按钮,找到刚才放在桌面的那个 uw_data_test.coe 文件。

【验证环节】:当你选好 COE 文件后,你可以点击右侧的edit按钮。如果 Vivado 没报错,并且能预览出你生成的那些递增数据,说明大功告成