- Analog-to-Digital Converter的缩写,译为模拟/数字转换器。是指将连续变化的模拟信号转换为离散的数字信号的器件

- 各种模拟量的采集:电子温度计、数字体温计、电子秤、数字万用表、数字示波器、光照强度计、噪声检测计

ADC的概述

ADC的主要性能指标

- 分辨率:ADC的分辨率通常以输出二进制数的位数表示,位数越多,分辨率越高,如12位ADC,在3.3V参考电压的情况下,能分辨出的最小电压为:3.3/4095≈0.80586mV

- 采样率:每秒采集信号的个数,如 2.5Msps,表示每秒可以采样 2.5×106次

- 转换时间:从转换开始到获得稳定的数字量输出所需要的时间

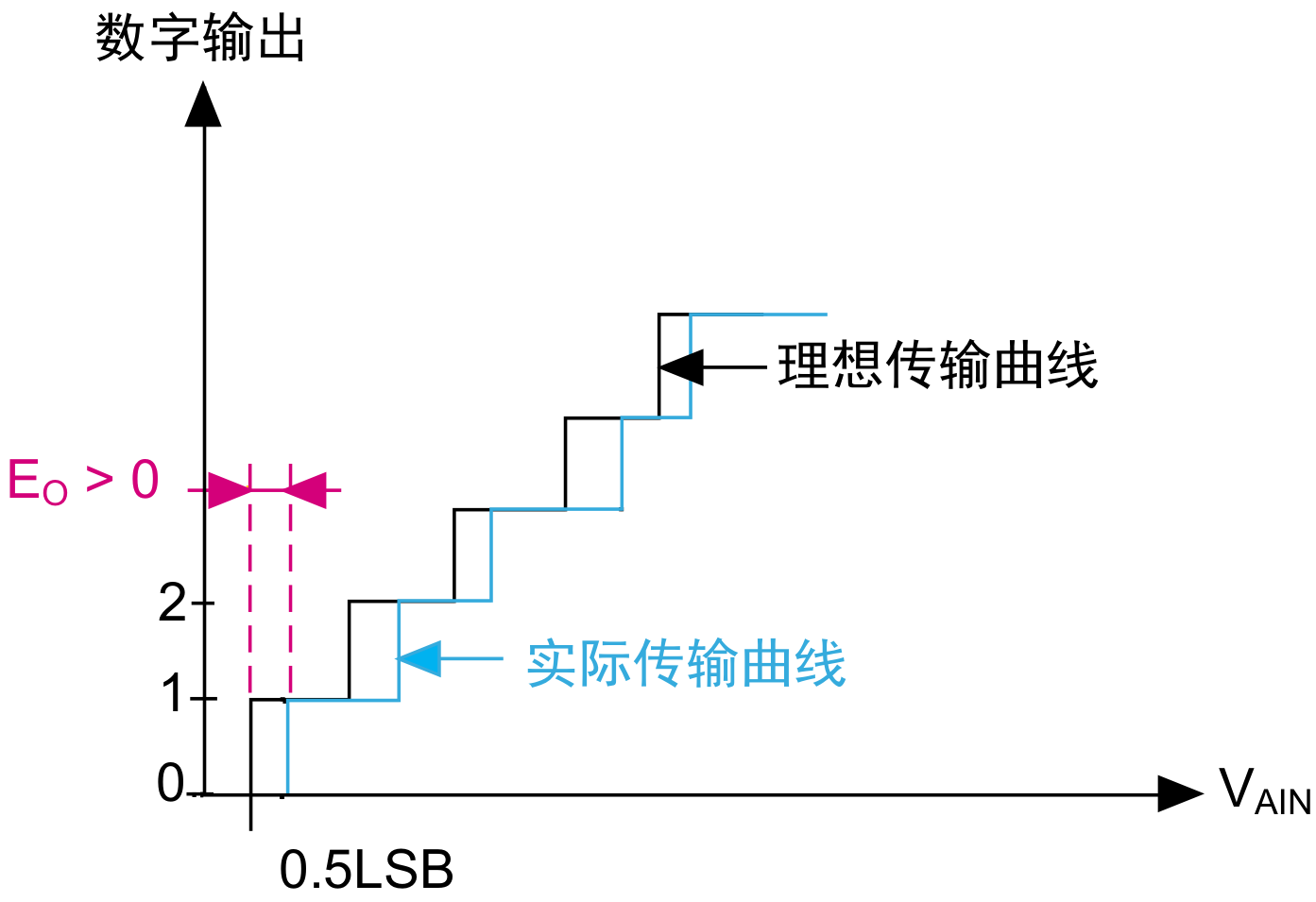

- 转换精度:ADC输出的数字量所表示的模拟值与实际输入的模拟量之间的偏差,造成转换误差的原因有很多,有器件自身的原因,也要应用的原因

ADC采样值到实际电压的转换

- 已知:ADC位数: n,ADC参考电压: Vref,采样值为:Ncov,则被采样点的电压为:

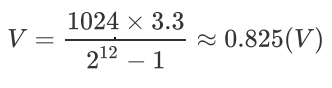

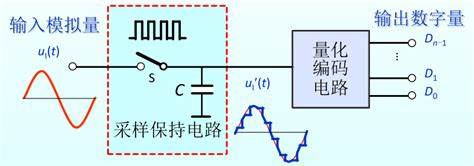

- 例1,12位ADC,参考电压是3.3V,采样值是 1024,则 采样点的电压是:

- 例2,14位ADC,参考电压是2.5V,采样值是 990,则 采样点的电压是:

逐次逼近型(SAR)实现原理

- 是单片机上最常见的ADC实现方案,除次之外还有积分型、并行比较型、压频变换型

- 原理类似于数据结构中的折半查找(二分法搜索)

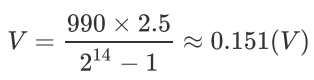

- 逐次逼近型ADC是应用非常广泛的模/数转换方法,它包括1个比较器、1个数模转换器、1个逐次逼近寄存器(SAR)和逻辑控制单元。它是将采样输入信号与已知电压不断进行比较,1个时钟周期完成位转换,N位转换需要N个时钟周期,转换完成,输出二进制数

- 具体的说:初始化DAC的输出由寄存器设置为1/2Vref,然后由比较器判断大小来决定输出1或0,进而进行下一步再次设置寄存器输出DAC,如此循环到最后一次LSB。依次输出的0和1即为转换后的数字量。算法核心就是二分法搜索,类似于猜数字值的游戏

- 这一类型ADC的分辨率和采样速率是相互矛盾的,分辨率低时采样速率较高,要提高分辨率,采样速率就会受到限制

- 特点:

- 100K到1M的中等速度,12到16位的中等精度,综合性能较好,因此是目前应用最多的ADC架构之一

- 精度主要决定于DAC的转换精度,因此DAC需要校准,比较器也需要满足高速和能够匹配系统的较高精度

- 功耗可调,由转换速度决定,因此也限制了高速应用

- 总之SAR型ADC的内部各组成模块需要组合设计性能匹配最优

ADC电路设计注意事项

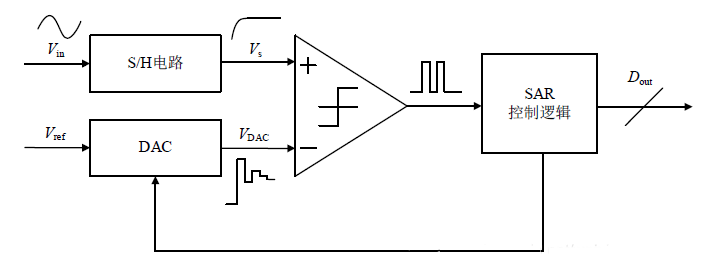

采样保持电路

- 根据奈奎斯特定律(也称之为"香农"定律),采样频率,需要大于2倍的被测信号频率,才能还原该信号

输入电压范围

- 输入电压需要在参考电压范围内,对于模拟量的输出,最好转换到其最大值接近参考电压最大值,以发挥ADC分辨率的优势

参考电压的重要性

- 一般带ADC功能的单片机,要求参考电压不能高于供电电压,且要求保持稳定及高精度

- 有专用的参考电压供电IC,如 TL431 提供精准的2.5V参考电压

- STM32系列,根据封装形式,决定是否有单独的ADC参考电源引入脚

STM32U5中的ADC

概述与特性

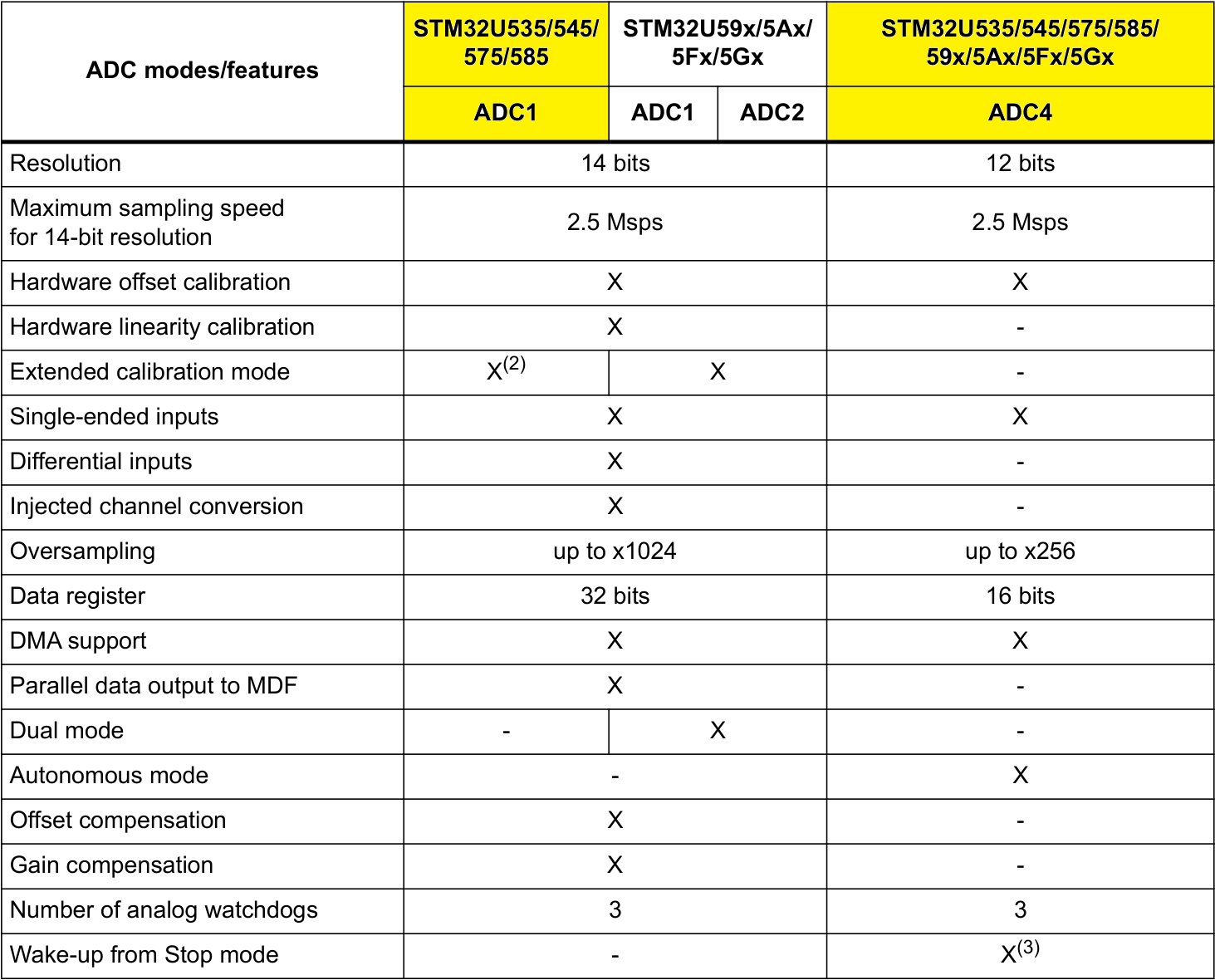

主要特性

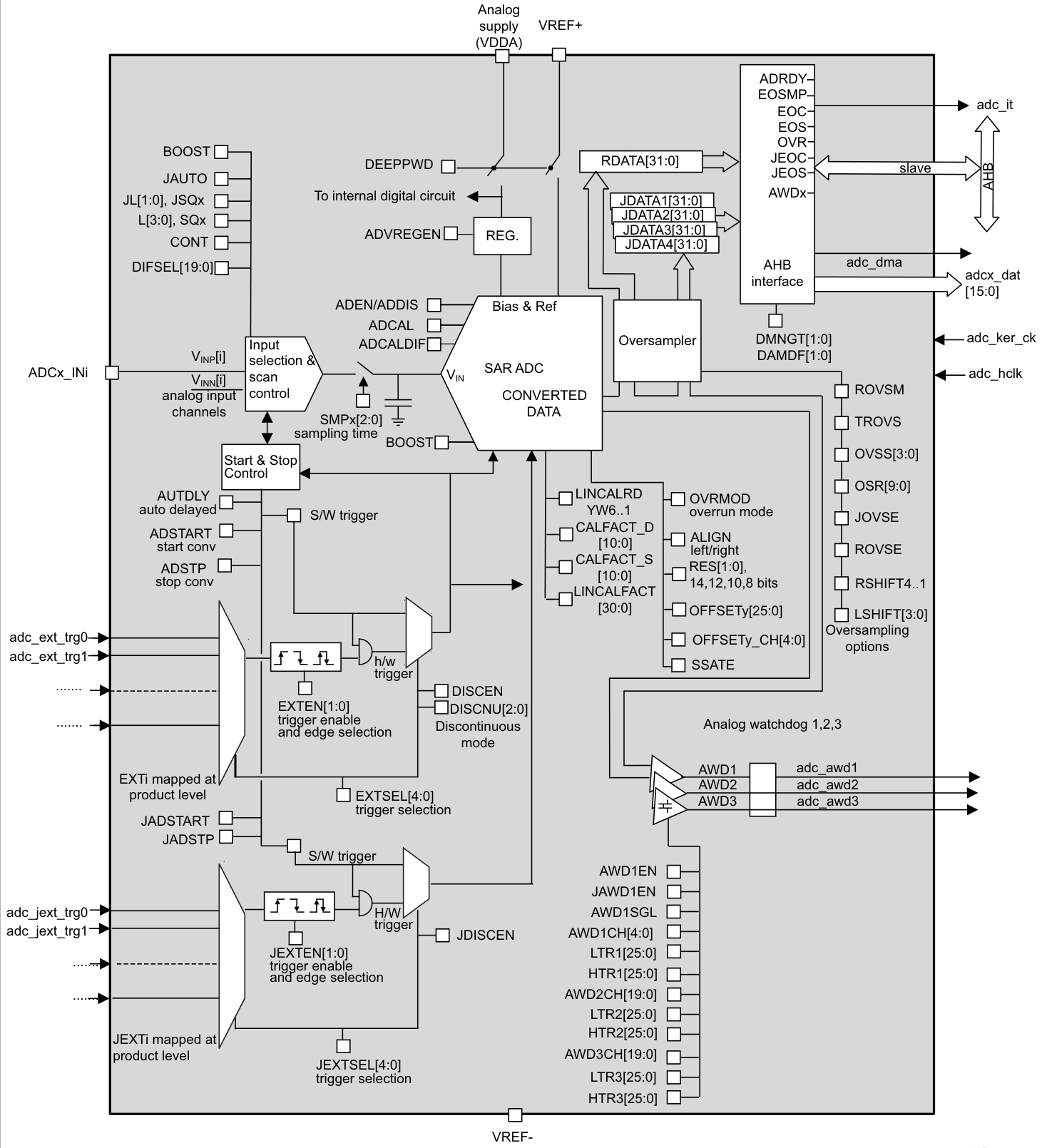

逻辑框图

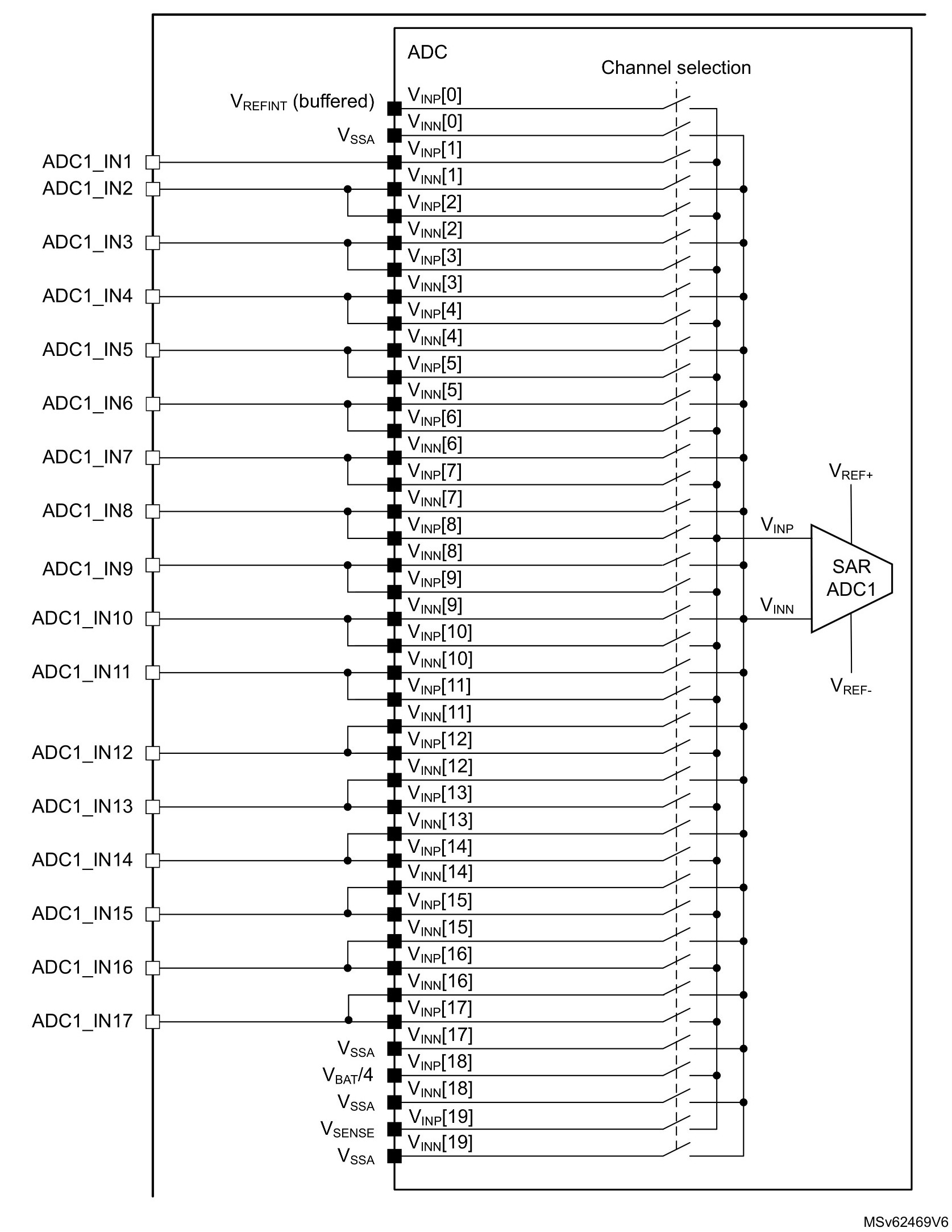

可使用的通道

- 一共20个通道

- 17个连接GPIO的模拟输入通道

- 3个内部模拟输入通道

- 内部温度传感器 (VSENSE)

- 内部参考电压 (VREFINT)

- 后备电源电压 (VBAT/4)

ADC深度掉电模式和ADC调压器

- 默认情况下,ADC处于深度掉电模式(Deep-power-down mode),此时其供电电压被内部切断以降低漏电流(ADC_CR寄存器中DEEPPWD位的复位状态为1)

- 要启动ADC操作,请按以下步骤操作:

- 首先通过清除DEEPPWD位退出深度掉电模式

- 然后通过设置 ADC_CR 寄存器中的ADVREGEN位使能ADC内部电压调节器。在启动校准或使能ADC前,软件必须等待ADC电压调节器的启动时间,这可以可通过轮询ADC_ISR寄存器中的LDORDY位实现

- 当ADC操作完成后,可以禁用ADC(ADEN=0)。为节省功耗,还可同时禁用ADC电压调节器(清除ADVREGEN位),以此来进一步降低功耗

- 此外,可通过设置ADC_CR寄存器中的DEEPPWD位再次进入ADC深度掉电模式,这在进入Stop模式前特别有用

- 设置DEEPPWD位将自动禁用ADC电压调节器,并清除ADVREGEN位

- 当内部电压调节器禁用时(ADVREGEN=0),内部模拟校准因子会保留

- 在ADC深度掉电模式下(DEEPPWD=1),内部模拟校准数据会丢失,必须重新启动校准或重新应用之前保存的校准因子

校准

- ADC提供自动校准功能,该功能可控制包括ADC上电/断电在内的完整校准流程

- 校准过程中,ADC会计算单端模式和差分模式的偏移校准系数。该系数包含内部偏移量和线性度参数,校准结果将在ADC内部持续生效直至下一次断电

- 校准是任何ADC操作的前提条件,它能消除芯片间差异导致的系统误差,并对偏移量和线性度偏差进行补偿

- 偏移校准对单端通道和差分通道均适用

- 线性度校正只需执行一次(与单端/差分配置无关):

- 启用线性度校准:在ADC_CR寄存器中设置ADCALLIN位,随后启动的校准将同时执行线性度和偏移校准

- 禁用线性度校准:清除ADC_CR中的ADCALLIN位,校准仅执行偏移校准

- 通过软件设置ADCAL位可启动校准流程,此时ADC必须处于禁用状态(ADEN=0)。校准期间ADCAL位保持为1,完成后由硬件自动清零,校准系数将存储于ADC模拟模块中

- 如果ADC被禁用(ADEN = 0),内部模拟校准值将得以保留。然而,若ADC长时间处于禁用状态、环境温度发生变化或电源电压变动超过10%,建议在重新启用ADC前执行新的偏移校准周期

- 每次ADC电源关闭时(例如当设备进入待机或VBAT模式),内部模拟校准值将会丢失。此时若软件已保存先前校准生成的校准系数,为避免重复校准耗时,可直接将该校准系数重新写入ADC模拟模块而无需再次校准

单端和差分输入

- ADC通道可配置为单端输入模式或差分输入模式

- 该配置通过写入ADC_DIFSEL寄存器中的DIFSEL[19:0]位实现,且必须在ADC禁用状态下(ADEN =0)进行配置

- 在单端输入模式下,通道"i"待转换的模拟电压为外部正输入VINP[i]与负基准电压VREF-之间的差值

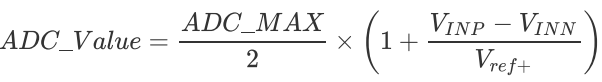

- 在差分输入模式下,通道"i"待转换的模拟电压为外部正输入VINP[i]与负输入VINN[i]之间的差值。差分模式输出数据为无符号格式:

- 当VINP[i] = VREF-且VINN[i] = VREF+时,输出数据为0x0000(14位分辨率模式)

- 当VINP[i] = VREF+且VINN[i] = VREF-时,输出数据为0x3FFF

- 转换值由下面的公式计算出

注:ADC_MAX 是当前分辨率下的最大转换值,如14bit,则为0x3FFF

- 当ADC配置为差分模式时,两个输入端必须偏置在VREF+/2电压

- 当通道"i"配置为差分输入模式时,其负输入电压将连接至VINN[i-1]

通道选择及分组

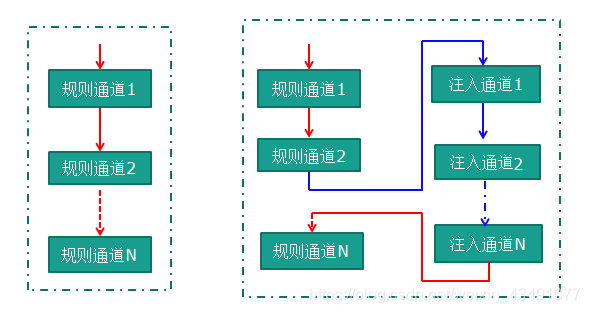

规则通道组

- 规则通道就是很规矩的意思,我们平时一般使用的就是这个通道组。相当于正常运行的程序。最多16个通道

- 规则通道和它的转换顺序在ADC_SQR[1...3]寄存器中选择,规则组转换的总数应写入ADC_SQR1寄存器的L[3:0]中

- ADC模块上20个可选的通道,可以以任意的顺序选择任意的通道

- 规则通道组每个通道转换完成的数据,都在一个数据寄存器ADC_DR中

注入通道组

- 注入,可以理解为插入,插队的意思,相当于中断。最多4个通道。

- 如果在规则通道组转换期间,注入通道组被启动,则当前的转换会复位,ADC会优先对注入通道序列进行转换,直到注入通道组中的通道根据相应的规则转换完成,规则通道组的规则转换会从上次中断的规则转换处恢复

- 注入通道组和它的转换顺序在ADC_JSQR寄存器中选择。注入通道组里转化的总数应写入ADC_JSQR寄存器的L[1:0]中

- 注入通道组的转换数据分别保存在对应的数据寄存器ADC_ADC_JDR[1...4]中

通道预选寄存器(ADC_PCSEL)

- 对于通过SQRx或JSQRx位选定的每个通道,必须预先配置相应的ADC_PCSEL位

转换顺序

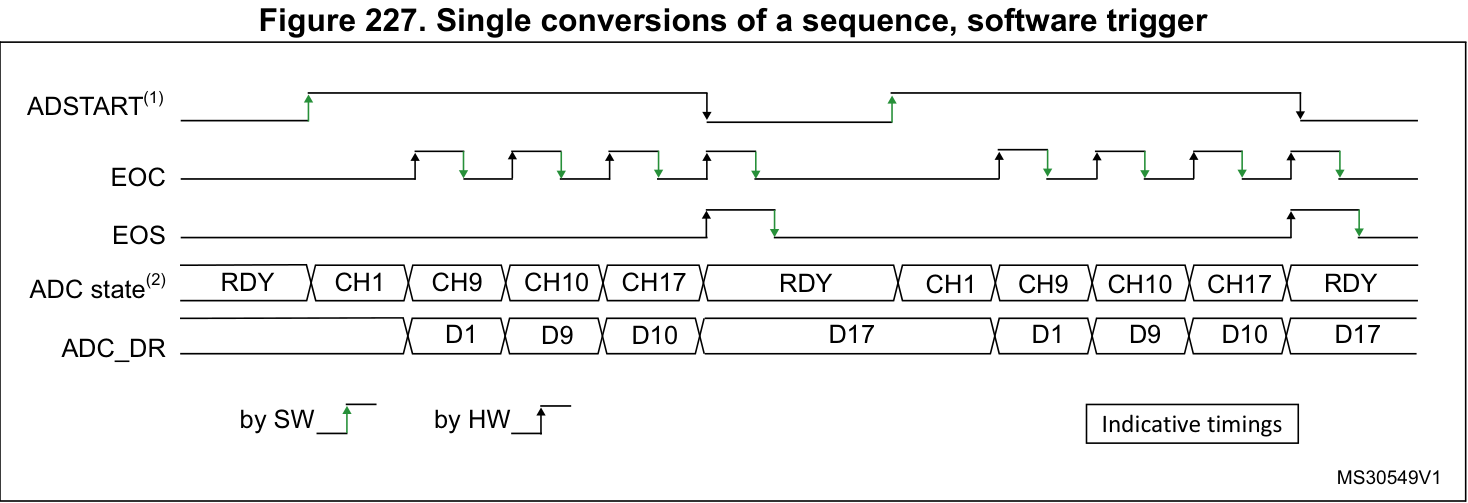

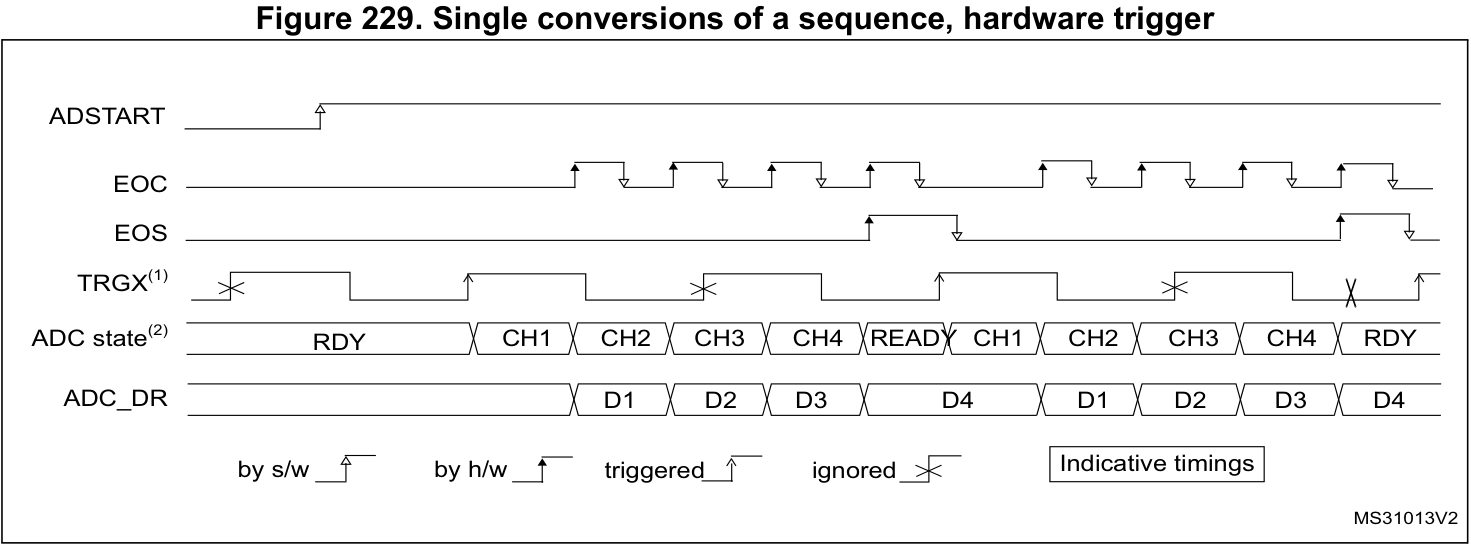

单次转换模式(CONT = 0)

- 在单次转换模式下,ADC会对所有通道执行一次转换。该模式通过以下任一方式在CONT位为0时启动:

- 通过设置ADC_CR寄存器中的ADSTART位(针对规则通道,且选择软件触发)

- 通过设置ADC_CR寄存器中的JADSTART位(针对注入通道,且选择软件触发)

- 外部硬件触发事件(适用于规则或注入通道)

- 在注入通道序列中,每次转换完成后:

- 转换数据会存入四个32位ADC_JDRy寄存器中的一个

- JEOC(注入转换结束)标志位被置位

- 若JEOCIE位已置位,则产生中断

- 在规则通道序列完成后:

- EOS(规则序列结束)标志位被置位

- 若EOSIE位已置位,则产生中断

- 随后,ADC停止工作,直到新的外部规则或注入触发事件发生,或者再次设置ADSTART或JADSTART位

注意: 若需对单个通道进行转换,应将序列长度设置为1

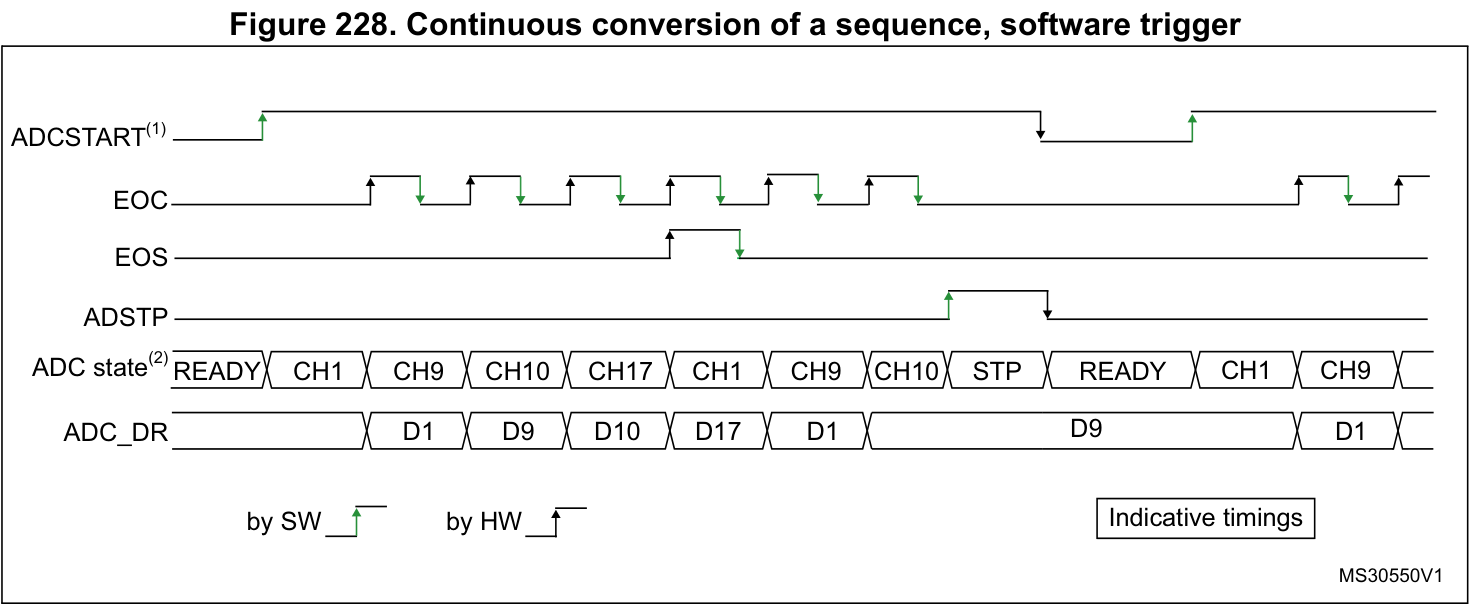

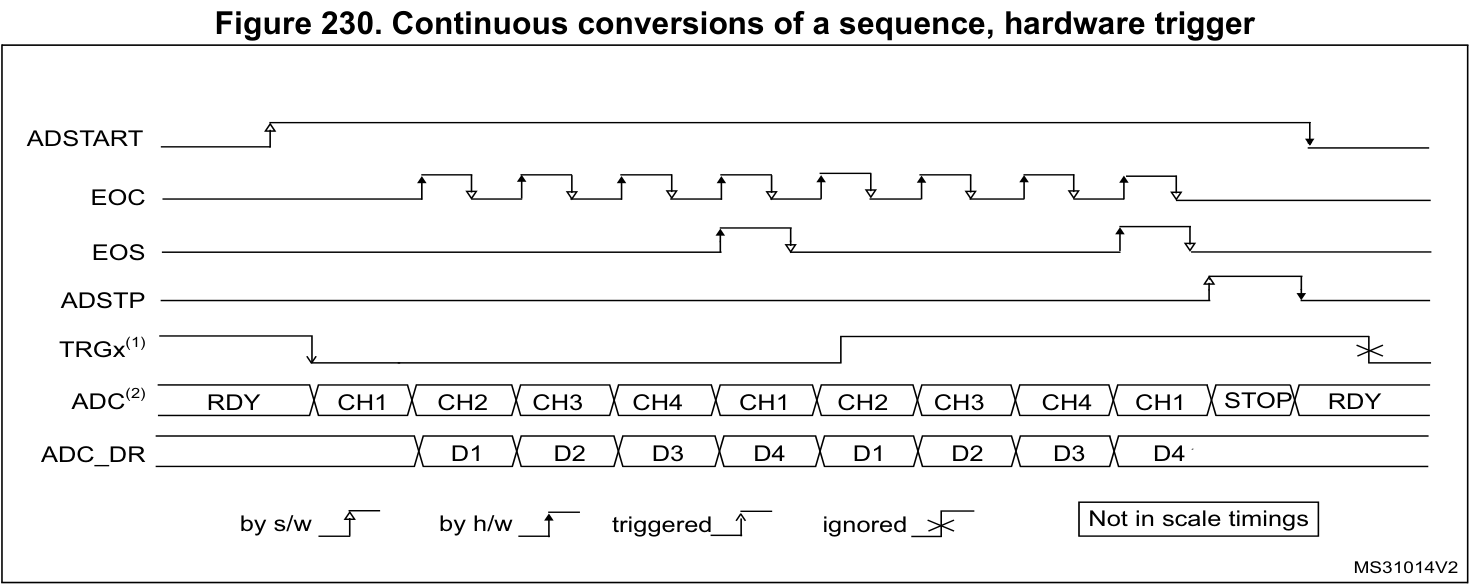

连续转换模式 (CONT = 1)

- 此模式仅适用于规则通道

- 在连续转换模式下,当软件或硬件规则触发事件发生时,ADC会执行一次所有规则通道的转换,然后自动重新启动,并持续循环执行该转换序列。该模式通过以下方式在CONT位为1时启动:

- 外部触发

- 设置ADC_CR寄存器中的ADSTART位

- 在规则通道序列中,每次转换完成后:

- 转换数据存入32位ADC_DR寄存器

- EOC(转换结束)标志位被置位

- 若EOCIE位已置位,则产生中断

- 在转换序列完成后:

- EOS(序列结束)标志位被置位

- 若EOSIE位已置位,则产生中断

- 随后,ADC立即重新开始新的转换序列,并持续循环执行

不连续转换模式

规则组模式

- 该模式通过设置 ADC_CFGR1 寄存器中的 DISCEN 位使能,用于转换ADC_SQRy 寄存器中选定转换序列的一个短序列(子组),子组包含 n 次转换(n ≤ 8)。n 的值由 ADC_CFGR1 寄存器中的 DISCNUM[2:0] 位设定

- 当外部触发发生时,ADC 会从 ADC_SQRx 寄存器中选择接下来的 n 次转换执行,直到整个序列的所有转换完成。序列的总长度由 ADC_SQR1 寄存器的 L[3:0] 位定义

- 注意,无法同时使用连续转换模式和不连续转换模式

- 示例 DISCEN = 1,n = 3,待转换通道 = 1, 2, 3, 6, 7, 8, 9, 10, 11

- 第 1 次触发:转换通道 1、2、3(每次转换均生成 EOC 事件)

- 第 2 次触发:转换通道 6、7、8(每次转换均生成 EOC 事件)

- 第 3 次触发:转换通道 9、10、11(每次转换均生成 EOC 事件,并在通道 11 转换完成后生成 EOS 事件)

- 第 4 次触发:重新开始,转换通道 1、2、3(每次转换均生成 EOC 事件)

- ...(依此循环)

注入组模式

- 该模式通过设置ADC_CFGR1寄存器中的JDISCEN位启用。在外部注入触发事件后,它会逐个通道转换ADC_JSQR寄存器中选择的序列。这相当于常规通道的不连续模式,其中'n'固定为1

- 当外部触发发生时,它将启动ADC_JSQR寄存器中选择的下一个通道转换,直到序列中的所有转换完成。总序列长度由ADC_JSQR寄存器中的JL[1:0]位定义

- 示例:JDISCEN = 1,要转换的通道 = 1, 2, 3

- 第1次触发:通道1被转换(生成JEOC事件)

- 第2次触发:通道2被转换(生成JEOC事件)

- 第3次触发:通道3被转换,并生成JEOC事件 + JEOS事件

- ...

转换的启动和停止

软件的启动和停止

软件启动

- 可通过将 ADC_CR2 寄存器中的 ADON 位置 1 来为 ADC 供电。首次将 ADON 位置 1 时,会将ADC 从掉电模式中唤醒

- SWSTART 位置 1 时,启动规则组 AD 转换

- JSWSTART 位置 1 时,启动注入组 AD 转换

- SWSTART和JSWSTART通过硬件复位,复位条件:

- 单次转换完成

- 规则组的不连续转换完成

- 其他情况下,软件操作停止ADC转换后

软件停止

- ADSTP位置 1 时,停止正在进行的规则组转换,当前转换被终止,部分结果被丢弃

- JADSTP位置 1 时,停止正在进行的注入组转换,当前转换被终止,部分结果被丢弃

- 停止转换后,扫描序列也被终止,意味着,下次开始,重新按新序列开始停止转换后,可以重新配置ADC

外部触发

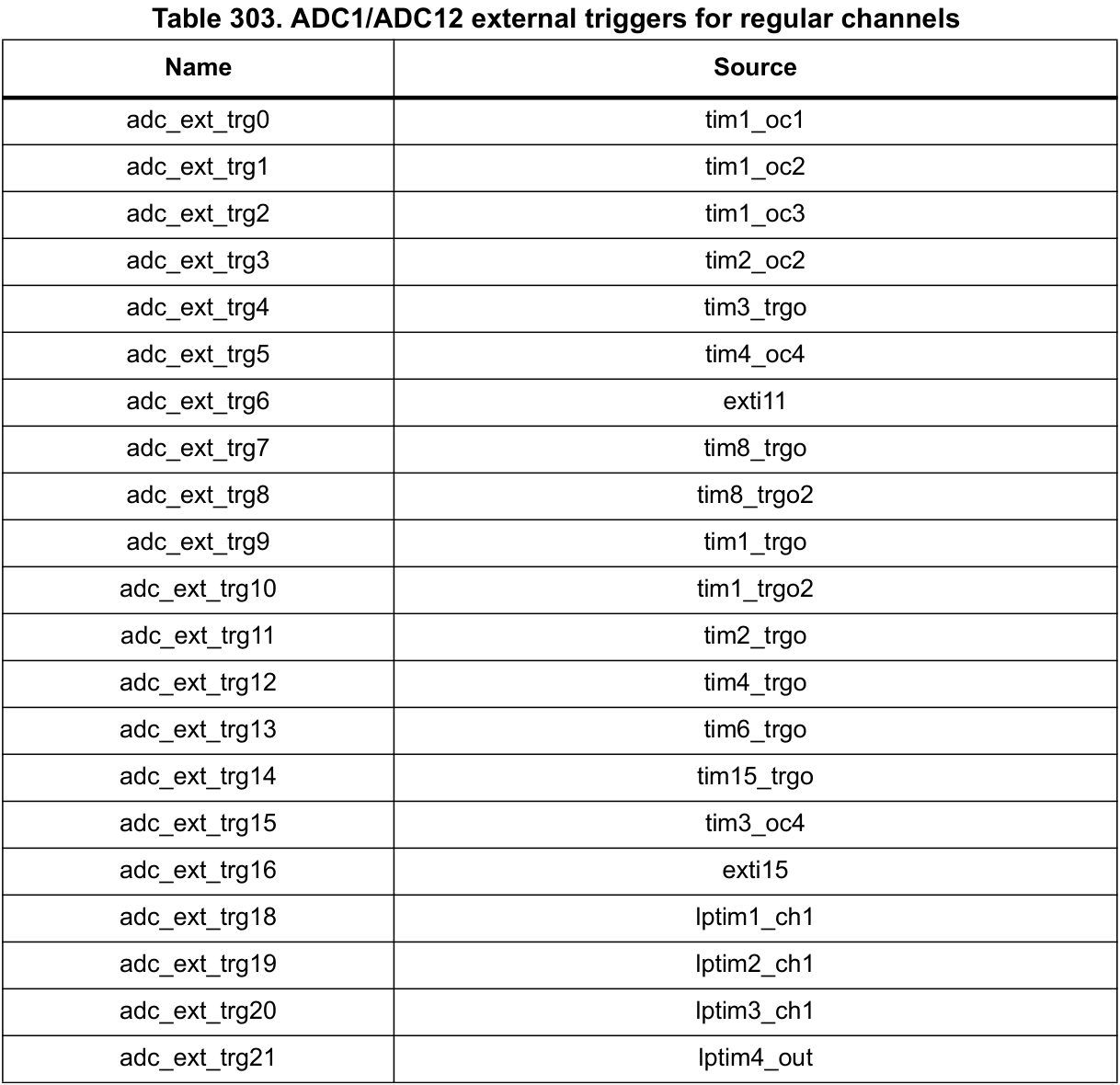

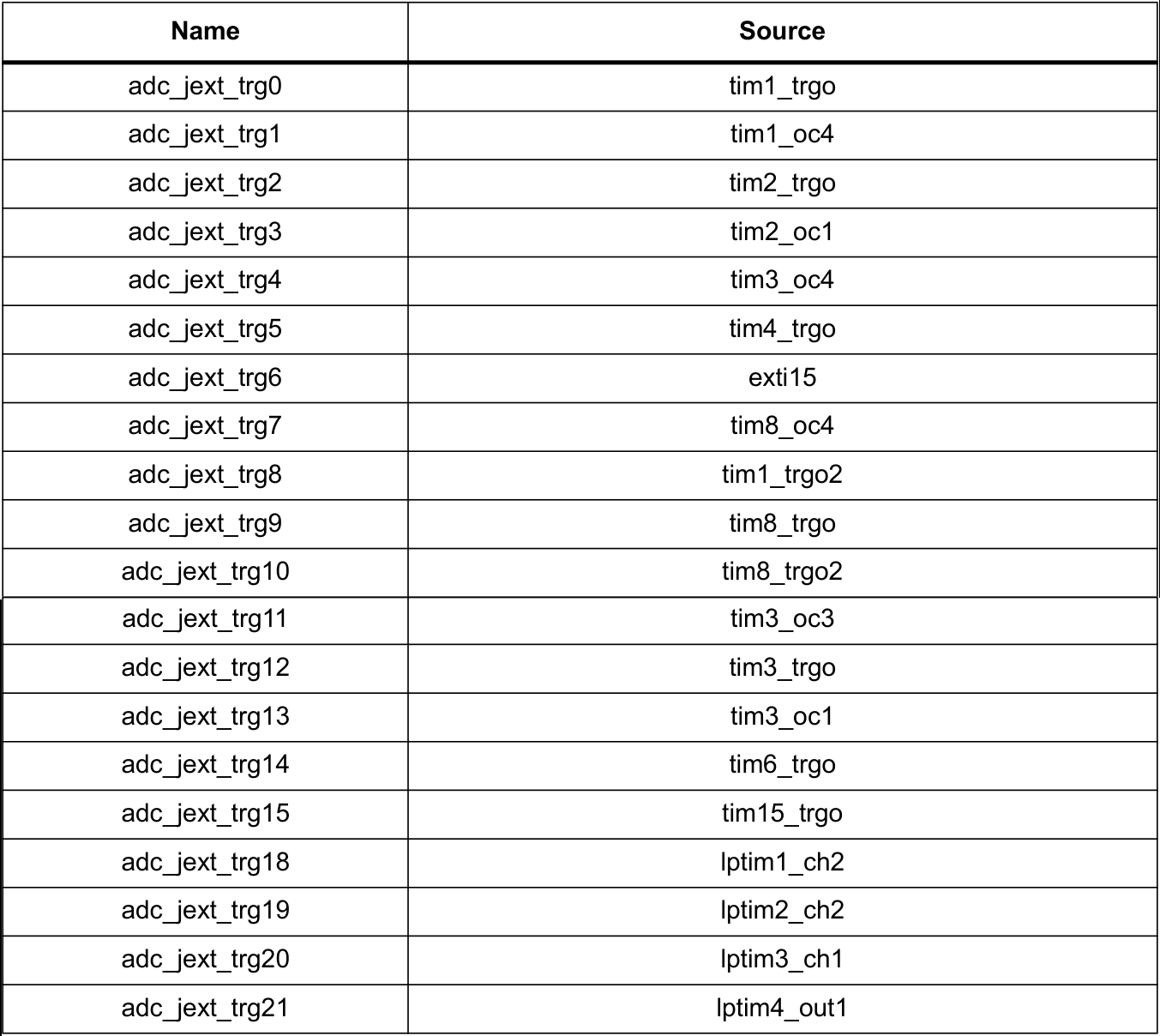

可选的外部触发事件

- 可以通过外部事件(例如,定时器输出、EXTI 中断线)触发转换

- 使用外部事件触发,在触发信号开始后,仍然需要使用SWSTART或JSWSTART来启动ADC转换

- 外部事件能够以所选极性触发转换,极性由EXTEN[1:0]或JEXTEN[1:0]控制

| EXTEN/JEXTEN[1:0] | 触发极性 |

|---|---|

| 00 | 外部硬件触发无效,软件触发有效 |

| 01 | 外部硬件上升沿触发 |

| 10 | 外部硬件下降沿触发 |

| 11 | 外部硬件上升、下降沿均触发 |

- 规则组外部触发条件

- 注入组外部触发条件

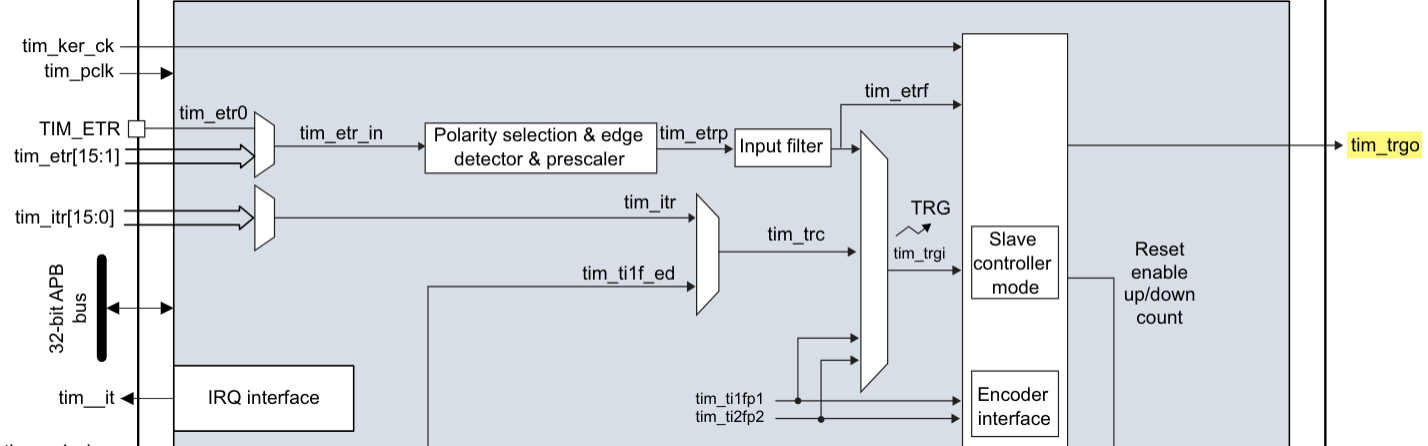

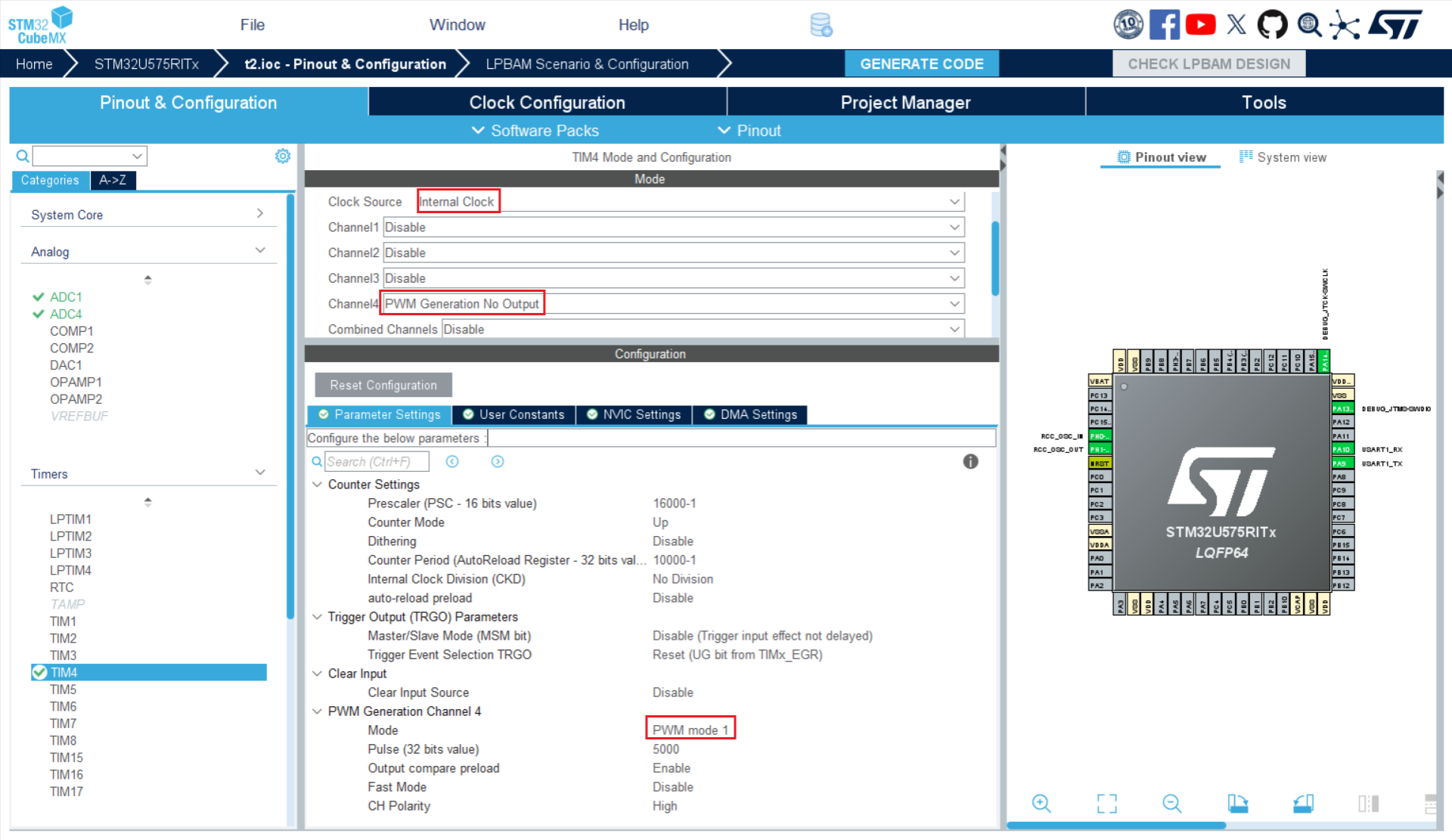

外部定时器的 trgo 信号触发源

- TRGO信号:定时器的主输出触发信号(Timer Trigger Output),可通过内部连线直接触发ADC,无需外部电路

- 触发源选择:定时器的更新事件(UEV)、比较匹配等均可作为TRGO源

- TIMx_CR2寄存器 - MMS[3:0]主模式选择配置表

| MMS [3:0] 值 | 模式名称 | 触发输出信号源 (tim_trgo) | 应用场景说明 |

|---|---|---|---|

| 0000 | 复位模式 | TIMx_EGR 寄存器的 UG 位(更新事件) | 控制从定时器复位。 |

| 0001 | 使能模式 | 计数器使能信号 CNT_EN(CEN 控制位与门控模式触发输入的逻辑 AND) | 同步启动多个定时器,或控制从定时器的使能窗口(需注意门控模式下的延迟)。 |

| 0010 | 更新事件模式 | 定时器更新事件(UEV) | 主定时器作为从定时器的预分频器(例如生成周期性 ADC 触发信号)。 |

| 0011 | 比较脉冲模式 | CC1IF 标志置位时生成正脉冲(捕获或比较匹配时触发) | 需要单次脉冲触发的场景(如精确控制外部设备时序)。 |

| 0100 | 比较输出 1 模式 | tim_oc1ref 信号(通道 1 比较参考) | 使用定时器通道 1 的比较事件触发其他外设(如 DAC 或 ADC)。 |

| 0101 | 比较输出 2 模式 | tim_oc2ref 信号(通道 2 比较参考) | 同通道 1,适用于多通道协同操作。 |

| 0110 | 比较输出 3 模式 | tim_oc3ref 信号(通道 3 比较参考) | 同通道 1,扩展至通道 3。 |

| 0111 | 比较输出 4 模式 | tim_oc4ref 信号(通道 4 比较参考) | 同通道 1,扩展至通道 4。 |

| 1000 | 编码器时钟模式 | 编码器接口的时钟信号 | 仅当 SMS [3:0] 为特定值(如 0001、1010 等)时有效,用于编码器相关时序控制。 |

- 配置方法(以更新事件为例)

- 设置定时器基本定时功能,重点是更新周期

- 配置TRGO与更新事件关联

- 启动定时器

- ADC触发选择定时器的TRGO信号

采样和转换结束

- 每次转换结束,可以通过EOC和JEOC标志置位来表明常规转换或注入转换结束,如果相应的中断允许位使能,还会产生相应的中断

- 标志可通过以下两种方式由软件清除:

- 向该标志位写1

- 读取ADC_DR 或 ADC_JDRy 寄存器

分组转换结束

- ADC在每次规则转换序列结束时,通过 EOS 标志置位通知整组转换结束

- ADC在每次注入转换序列结束时,通过 JEOS 标志置位通知整组转换结束

- 若 EOSIE 或 JEOSIE 中断使能位被置1,将触发中断

- 软件可通过向EOS或JEOS标志位写入1来清除该标志

不同转换方式的时序图

单次转换,软件触发

连续转换,软件触发

单次转换,硬件触发

连续转换,硬件触发

可配置的转换精度

- 通过降低ADC分辨率可实现更快的转换速度

- 用户可通过配置控制位RES[1:0]将分辨率设置为14位、12位、10位或8位

- 降低分辨率可缩短转换时间,适用于对数据精度要求不高的应用场景

- 不同分辨率下的TSAR时序参数

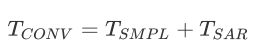

转换时间

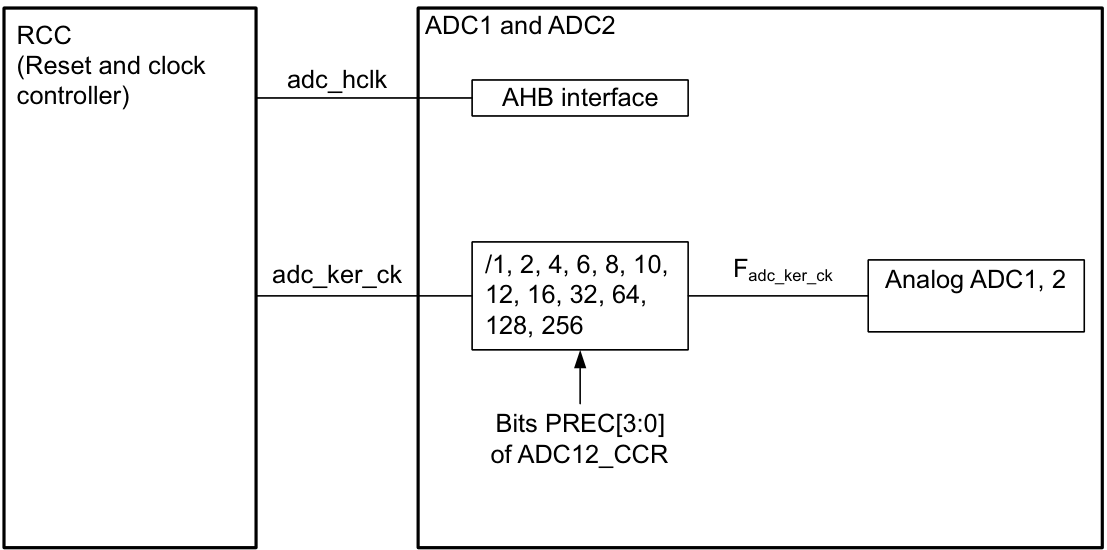

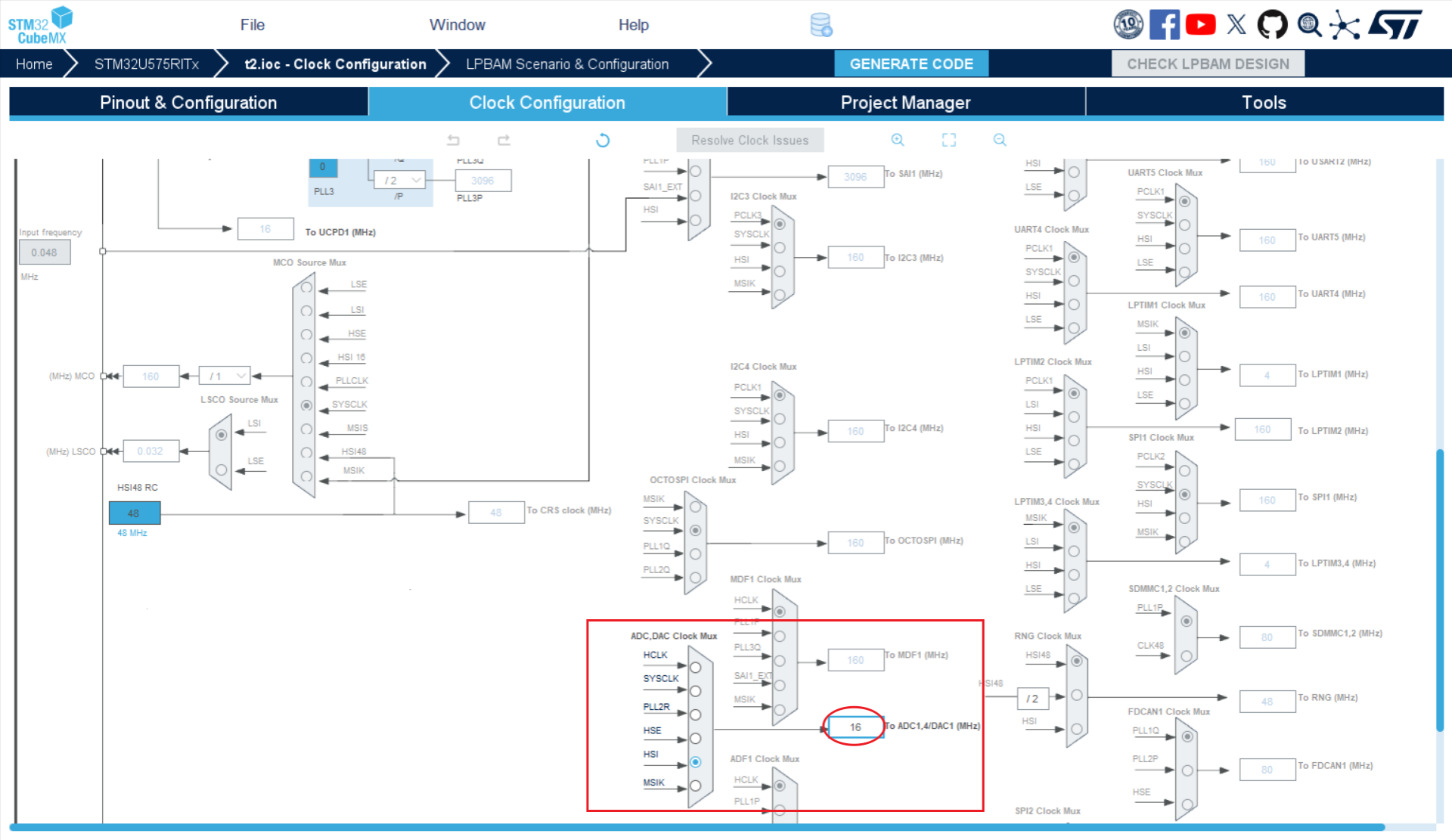

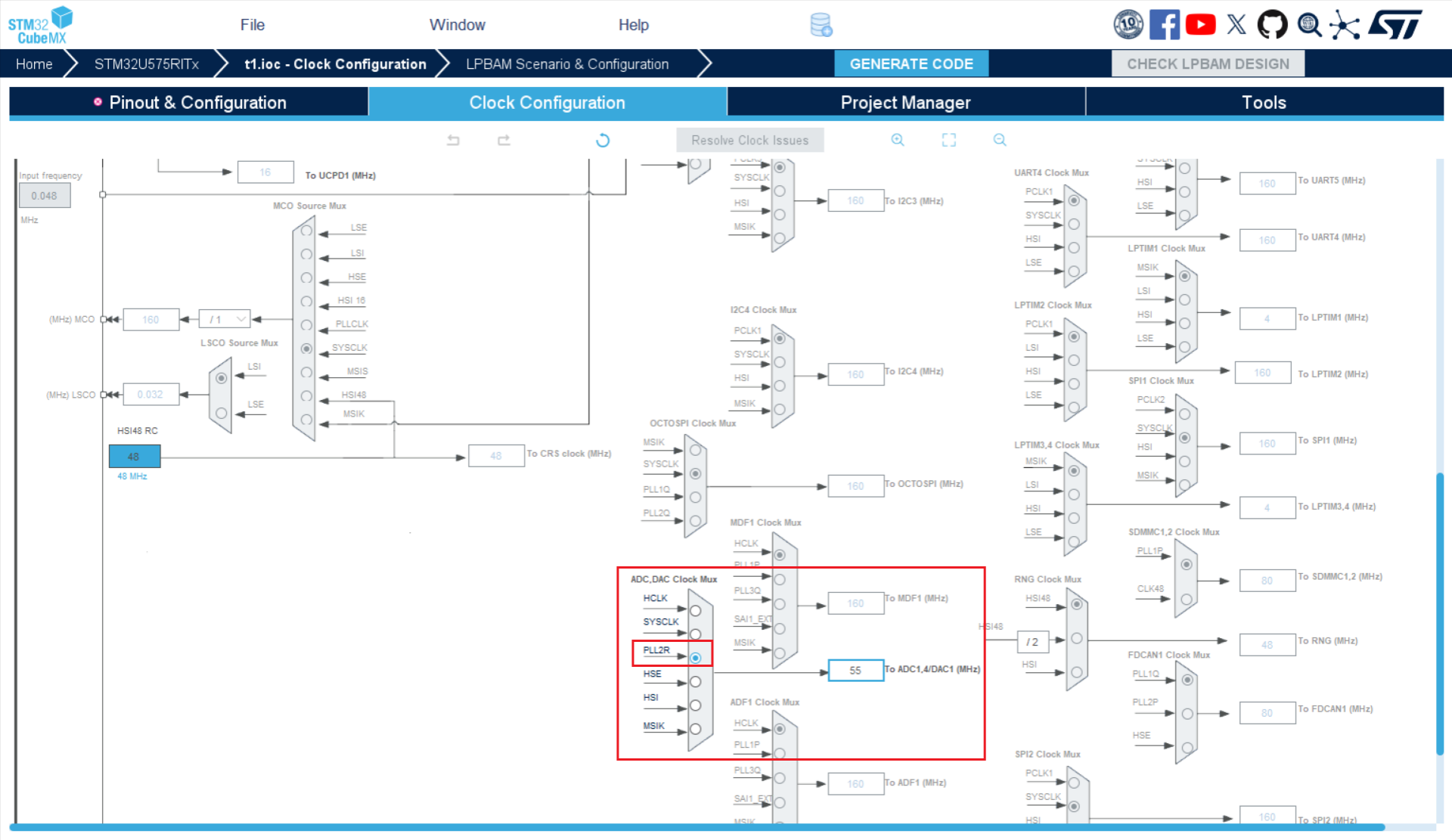

ADC时钟

- 双时钟域架构意味着ADC内核时钟独立于用于访问ADC寄存器的AHB总线时钟

- adc_ker_ck输入时钟可在不同时钟源之间选择,该选择在RCC中完成

- 选项1:ADC时钟可由独立于AHB时钟的内部或外部时钟源提供,且与AHB时钟异步

- 选项2:ADC时钟可从AHB时钟派生

- 选项1的优势在于无论AHB时钟方案如何选择,均可实现ADC时钟的最大频率。ADC时钟还可通过ADC12_CCR寄存器的PRESC[3:0]位配置预分频器,按1、2、4、6、8、10、12、16、32、64、128或256的比率分频

- 选项2可绕过时钟域再同步,适用于ADC由定时器触发且应用要求精确触发(无任何不确定性的情况)。否则,两个时钟域之间的再同步会引入触发时刻的不确定性。进入ADC模块的时钟频率范围:5MHz≤fadc≤55MHz5MHz\leq f_{adc}\leq 55MHz5MHz≤fadc≤55MHz

注意:时钟通过RCC配置,且必须符合器件数据手册中规定的工作频率要求

采样时间

- 每个通道可单独配置采样时间

- 通过 ADC_SMPR1 和 ADC_SMPR2 寄存器中的SMP值进行配置

- 可配置的采样时间按ClkADCClk_{ADC}ClkADC计

| SMP | ADC Clock | 时间 (µs)@55MHz |

|---|---|---|

| 000 | 5 | 0.09 |

| 001 | 6 | 0.11 |

| 010 | 12 | 0.22 |

| 011 | 20 | 0.36 |

| 100 | 36 | 0.65 |

| 101 | 68 | 1.24 |

| 110 | 391 | 7.11 |

| 111 | 814 | 14.8 |

ADC转换时间

- TSMPLT{SMPL}TSMPL :采样时间,可配置,最少5个ClkADCClk{ADC}ClkADC

- TSART{SAR}TSAR:SAR转换时间,根据所选精度不同,转换需要的时间不同,14bit时,需要17个

- ClkADCClk{ADC}ClkADC

- 最短ADC转换时间:(5+17)/55×106=0.4×10−6(s)=400ns(5+17)/55\times10^6 = 0.4\times10^{-6}(s) = 400 ns(5+17)/55×106=0.4×10−6(s)=400ns

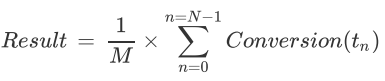

过采样

- 过采样是一种信号处理技术,它通过在信号的奈奎斯特频率以上的更高频率对信号进行采样,以提高模数转换器(ADC)的有效分辨率。这种技术通常用于提高低分辨率ADC的性能,而无需更换硬件

- 本质上,过采样是以时间换精度的方法

过采样的工作原理

- 过采样的核心思想是通过增加采样频率来降低量化噪声的影响。量化噪声是由于ADC将连续的模拟信号转换为离散的数字信号时产生的误差。在过采样过程中,这些噪声被分散到更宽的频率范围内,从而在感兴趣的频带内降低了噪声的功率密度。通过对信号进行过采样并应用数字低通滤波器,可以有效地减少噪声,提高信噪比(SNR),从而增加有效位数(ENOB)

过采样的使用条件

- 输入信号中必须存在白噪声,且其功率均匀分布在感兴趣的频段内。如果输入信号过于纯净(如直流电压),量化噪声会呈现固定的模式(如周期性纹波),此时过采样无效

- 噪声的幅度必须超过1个最低有效位(LSB),以确保信号的微小变化能够被ADC捕捉到

过采样提高分辨率的方法

- 每提高1位有效分辨率,需将采样率提高至4N倍(N为增加的位数)。例如:

- 提高1位:采样率需×4

- 提高2位:采样率需×16

- 具体实施:

- 提高采样频率:将原始采样频率提升至所需的过采样率。例如,需要提高1位分辨率,那么采样频率提升4倍

- 数据累加:连续采样多个值,并对这些值进行累加。例如,接上例,将4倍的数据累加

- 数据抽取:将累加的结果右移特定位数,以获得增加了有效位数的ADC值。例如,接上例,将累加结果右移1位

stm32u5上的过采样

- ADC上的过采样模块能够处理多路转换并将其平均为单路数据,同时扩展数据位宽(最高支持24位,即14位数值配合1024倍过采样率)

- 其输出结果格式如下(参数N和M可调):

- 过采样比N通过ADC_CFGR2寄存器的OSR[9:0]位配置,范围2x至1024x。除法系数M采用最高10位的右位移操作实现,由ADC_CFGR2寄存器的OVSS[3:0]位定义

- 累加单元可生成最高24位结果(1024个14位数据累加),支持左移或右移操作。选择右移时,系统会根据位移舍弃的最低有效位进行四舍五入处理,再将结果存入ADC_DR数据寄存器

数据处理

数据对齐

- 数据对齐方式通过ADC_CFGR2寄存器中的以下位域进行配置:

- OVSS[3:0]:控制数据右移位数,范围 0 ~ 11 位

- LSHIFT[3:0]:控制数据左移位数,范围 0 ~ 15 位

偏移校准(补偿)

- ADC转换的值,可以自动的加上一个偏移量,达到偏移校准的目的,类似于称东西时,给称去皮, 比如,某通道的转换值,需要统一减去一个固定值,才是真实的值,那么可以使用该功能,转换 后,ADC模块自动减去ADC_OFR[y]寄存器中设置的偏移校准值,用户从结果寄存器中读取的值, 已经是校准后的值,简化了用户处理流程

- 可通过在 ADC_OFRy (y = 1,2,3,4)寄存器的OFFSETy_CH[4:0] 位配置该校准值对应的通道, OFFSETy[23:0] 位是偏移量。偏移量可以是正值或负值,通过 POSOFF 位配置:当 POSOFF 位清 零时,转换结果将减去 OFFSETy[23:0] 位中写入的用户定义偏移量(结果可能为负值),此时读 取的数据为有符号数,SEXT 位表示扩展的符号值

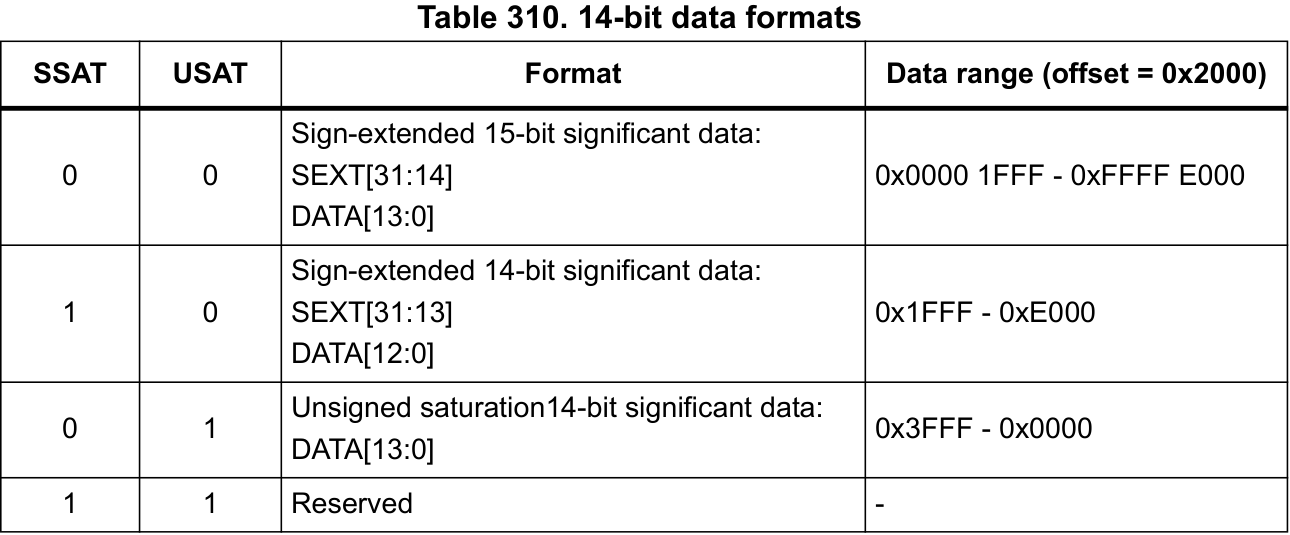

- 偏移量数值必须小于最大转换值(例如在 14 位模式下,最大偏移值为 0x3FFF)。该功能可用于 将无符号数据转换为有符号数据(例如在 14 位模式下,偏移量设置为0x2000)。 过采样模式下同样支持偏移校正。在过采样模式下,偏移量会在执行 OVSS 右移操作前被减去。

- 偏移校准可能导致数据宽度超出原始数据的位数。为了限制数据宽度,可通过ADC_OFRy 寄存器中 的SSAT (有符号饱和)和USAT (无符号饱和)位启用数据饱和功能

- 无符号14位数据 可通过设置 0x2000 的偏移值扩展为15位有符号数据

- 若需保持原始14位数据宽度,可通过设置SSAT位限制数据宽度为14位

- 若需将无符号数据饱和至原始宽度,可通过设置USAT位实现

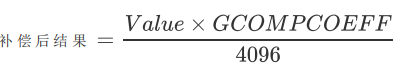

增益校准(补偿)

- ADC转换的值可以自动乘以一个比例值,以达到数据缩放的功能

- 当在 ADC_CFGR2 寄存器中设置 GCOMP 位时,所有转换后的数据均会启用增益补偿。每次转换后,数据将按以下公式计算:

- 由于 GCOMPCOEFF[13:0] 可编程范围为 0 至 16383,因此实际增益补偿系数范围为 0 至3.999756

- 在将最终数据存入 RDATA(规则数据寄存器)或 JDATAx(注入数据寄存器)之前,系统会评估 LSB−1(最低有效位减1)的值,以进行数据四舍五入,从而最小化误差

数据的溢出与DMA

ADC 溢出模式(OVRMOD)

发生溢出的条件及溢出标志

- 当 ADC_DR FIFO(8个数据)已满,规则转换数据未被(CPU或DMA)读取,会发生缓冲区溢出事件,溢出标志(OVR) 用于指示这种情况,若 OVRIE(溢出中断使能) 位被置 1,则会触发中断

- 溢出事件后的 ADC 行为:

- ADC 仍继续运行,可保持转换,除非软件主动停止(通过设置 ADSTP 位)并重置转换序列

- OVR 标志需由软件写入 1 来清除

溢出模式配置

- 通过 ADC_CFGR1 寄存器的 OVRMOD 控制位,可配置溢出事件发生时数据的处理方式:

- OVRMOD = 0(默认模式,保留旧数据)

- 数据寄存器不会被覆盖,旧数据在 ADC_DR FIFO 中保留

- 新转换结果被丢弃,若 OVR 仍为 1,后续转换结果也会被丢弃

- 适用场景:需确保数据完整性,避免数据丢失(如高精度测量)

- OVRMOD = 1(覆盖模式,保留最新数据)

- 数据寄存器会被最新转换结果覆盖,之前未读取的数据丢失

- 此模式下,ADC_DR FIFO 被禁用,ADC_DR 寄存器始终存储最新转换数据

- 适用场景:需实时获取最新数据,可接受部分数据丢失(如高速采样)

ADC 转换数据处理与的DMA介入

不使用DMA的转换管理

- 若转换速率足够慢,可通过软件处理转换序列。此时,软件需利用EOC标志及其关联中断处理每个数据。每次转换完成后,EOC标志置位,即可读取ADC_DR寄存器。必须将OVRMOD配置为0,以便将溢出事件作为错误处理

不使用DMA且无溢出的转换管理

- 在某些应用场景下(如器件配备模拟看门狗时),可能需要在不每次读取数据的情况下让ADC转换一个或多个通道。此时需将OVRMOD位配置为1,且软件应忽略OVR标志。溢出事件不会中断ADC的持续转换,ADC_DR寄存器始终保存最新转换结果

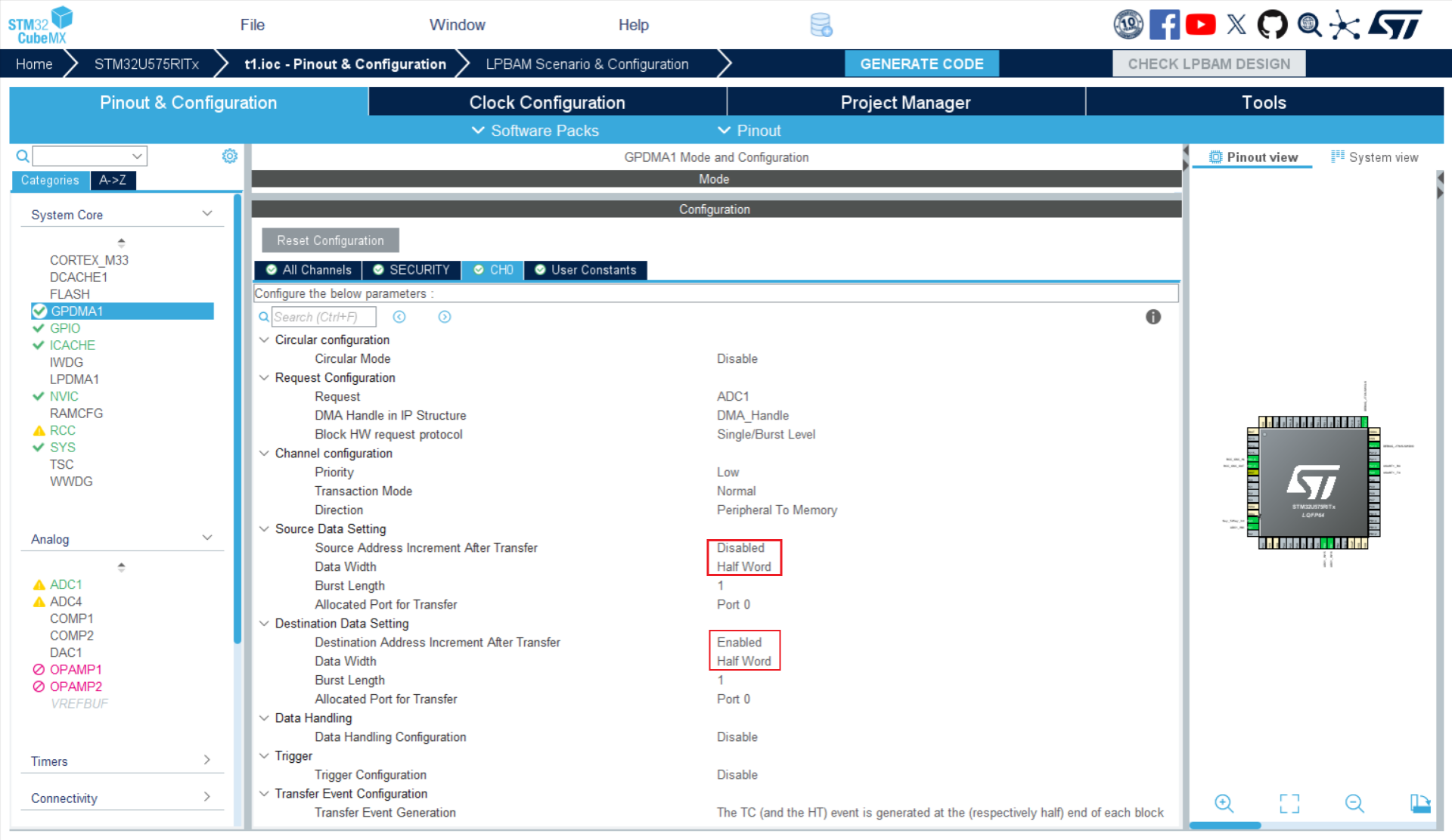

基于DMA的转换管理

- 由于转换通道值存储在单一数据寄存器中,使用DMA转换多通道可有效避免ADC_DR寄存器中已存储数据的丢失

- 当启用DMA模式(ADC_CFGR寄存器的DMNGT[1:0]=01或11),每次通道转换后都会产生DMA请求,从而将转换数据从ADC_DR寄存器传输至软件设定的目标地址

- 若因DMA未能及时响应传输请求导致溢出(OVR=1),ADC将停止生成DMA请求,新转换数据不会被DMA传输。这意味着所有传输至RAM的数据均可视为有效。根据OVRMOD位的配置,数据可能被保留或覆盖。DMA传输请求将被阻塞,直至软件清除OSV位

单次DMA模式(DMNGT[1:0]=01)

- 适用于DMA传输固定数量数据的场景

- 单次DMA模式特性

- ADC每次产生新转换数据时发起DMA请求

- DMA完成最后一次传输后(触发传输完成中断时),即使重启转换也不再产生请求

- 传输完成后:

- ADC数据寄存器内容冻结

- 进行中的转换被中止且结果丢弃

- 避免因未完成转换产生溢出错误

- 扫描序列停止并复位

- DMA停止工作

循环DMA模式(DMNGT[1:0]=11)

- 适用于DMA循环模式下的连续传输。

- 循环DMA模式特性

- ADC持续在数据寄存器就绪时生成DMA请求(即使DMA已完成末次传输)

- 支持配置DMA循环模式处理连续模拟输入数据流

带FIFO的DMA

- 数据输出寄存器配备8级FIFO,可并行产生两种DMA请求:

- "SREQ单次请求"(数据就绪时)

- "BREQ突发请求"(累积4个数据时)DMA可编程为单次传输模式或增量突发模式(4拍)

ADC的中断

| 中断事件 | 事件标志 | 使能控制位 |

|---|---|---|

| ADC 准备就绪 | ADRDY | ADRDYIE |

| 常规组转换结束 | EOC | EOCIE |

| 常规组转换序列结束 | EOS | EOSIE |

| 注入组转换结束 | JEOC | JEOcie |

| 注入组转换序列结束 | JEOS | JEOSIE |

| 模拟看门狗 1 状态位置位 | AWD1 | AWD1IE |

| 模拟看门狗 2 状态位置位 | AWD2 | AWD2IE |

| 模拟看门狗 3 状态位置位 | AWD3 | AWD3IE |

| 采样阶段结束 | EOSMP | EOSMPIE |

| 溢出 | OVR | OVRIE |

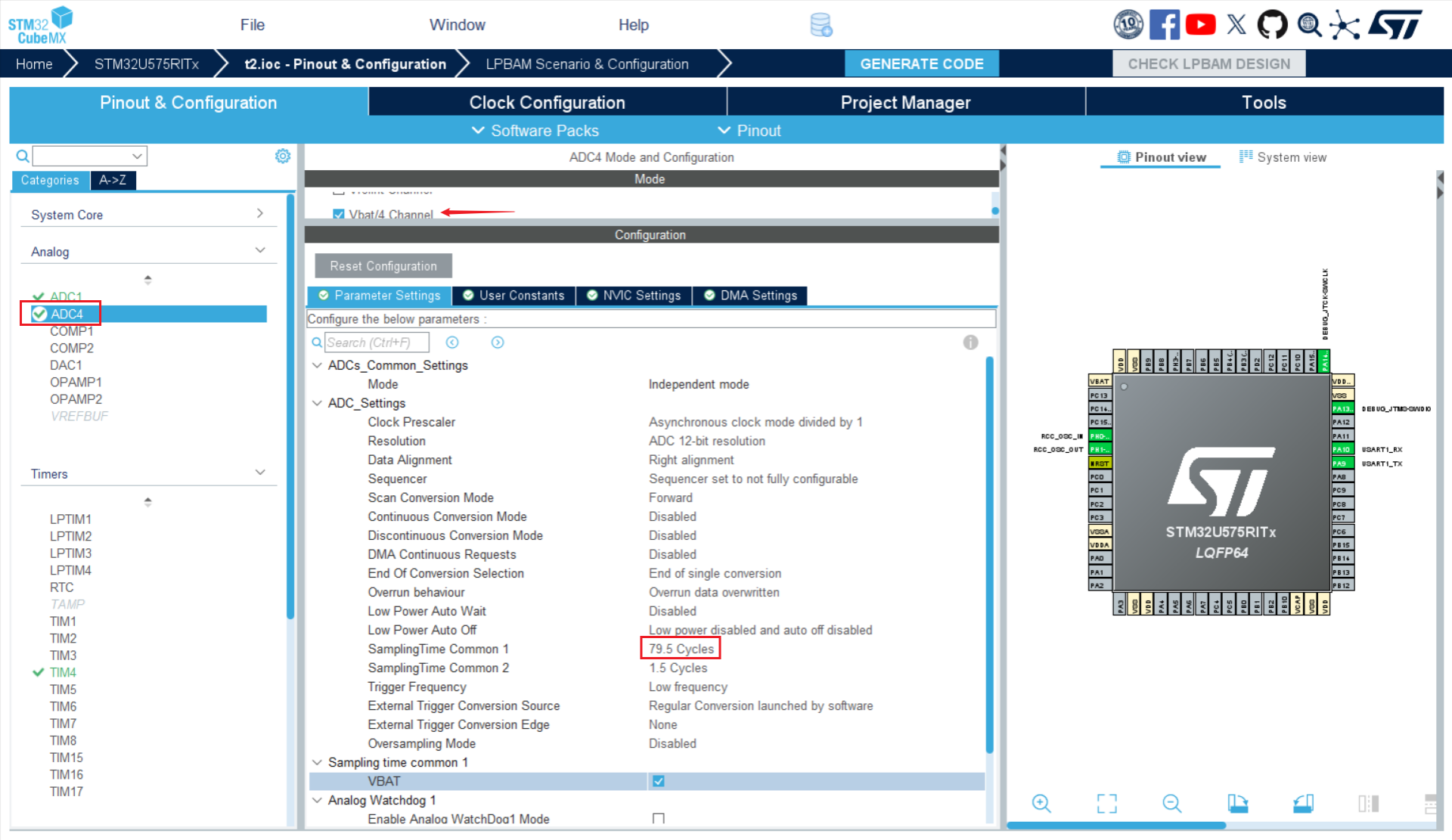

ADC4和ADC1的区别

- 转换分辨率:12位

- 没有差分输出模式

- 没有规则组和注入组的区分,仅有一种分组,仅能按通道编号顺序采集

- 共用2个预设的采样时间,每个通道可以2选1

- 内部没有FIFO,如果当前的转换结果没有被及时读取,就会引发溢出标志置位,也不支持DMA的多字节突发传输模式

- 在部分低功耗模式下,仍能保持工作状态,或者保持通过DMA对持续转换

ADC基本应用

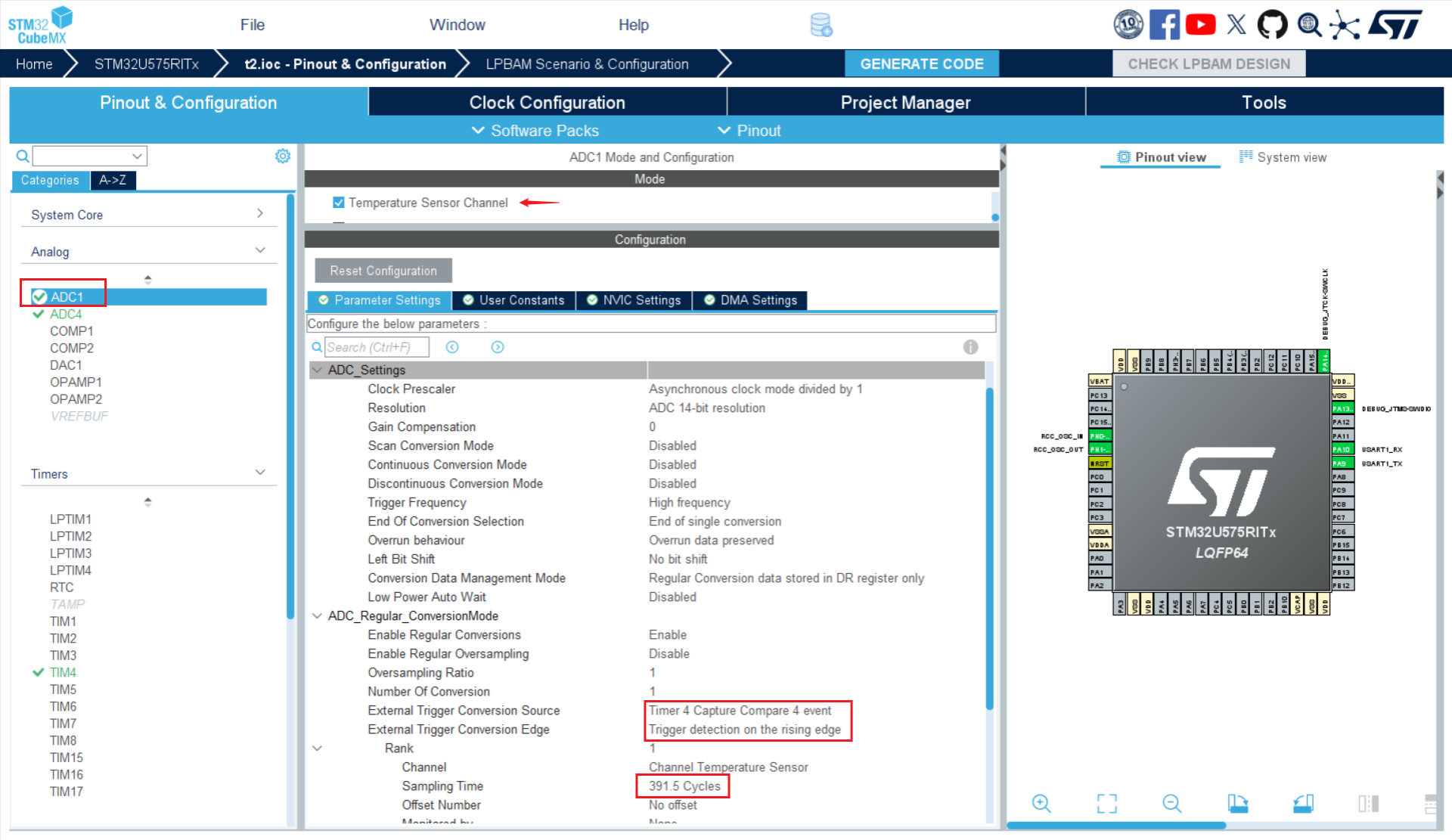

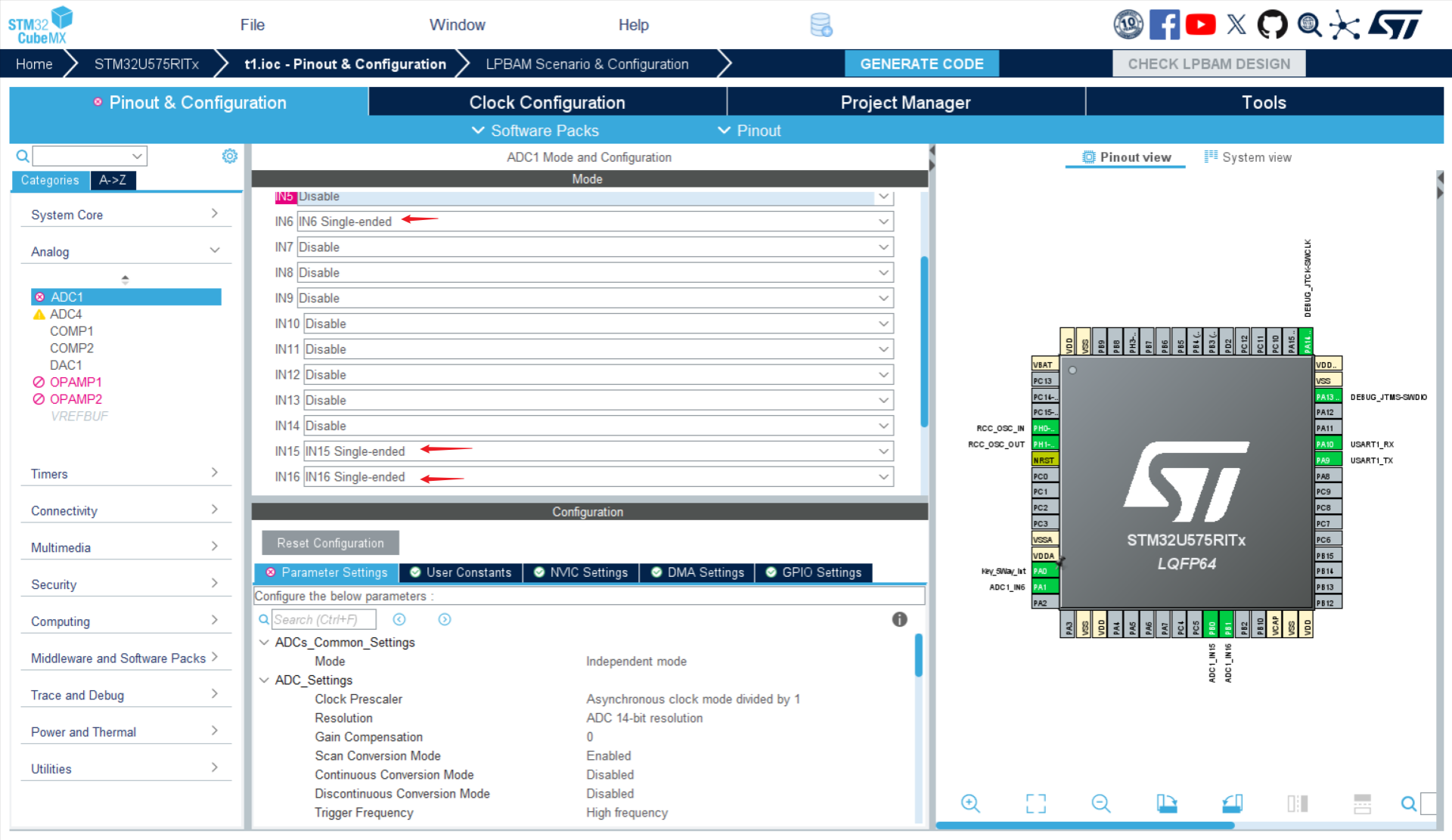

查询及中断用法

- ADC1测量芯片结温,由定时器触发,每1s,完成一次测量,并通过中断获取转换值,然后计算当前温度,并打印结果

- ADC4测量VBAT的值,由软件触发,每1s,查询方法实现转换,完成后,计算VBAT电压,并打印结果

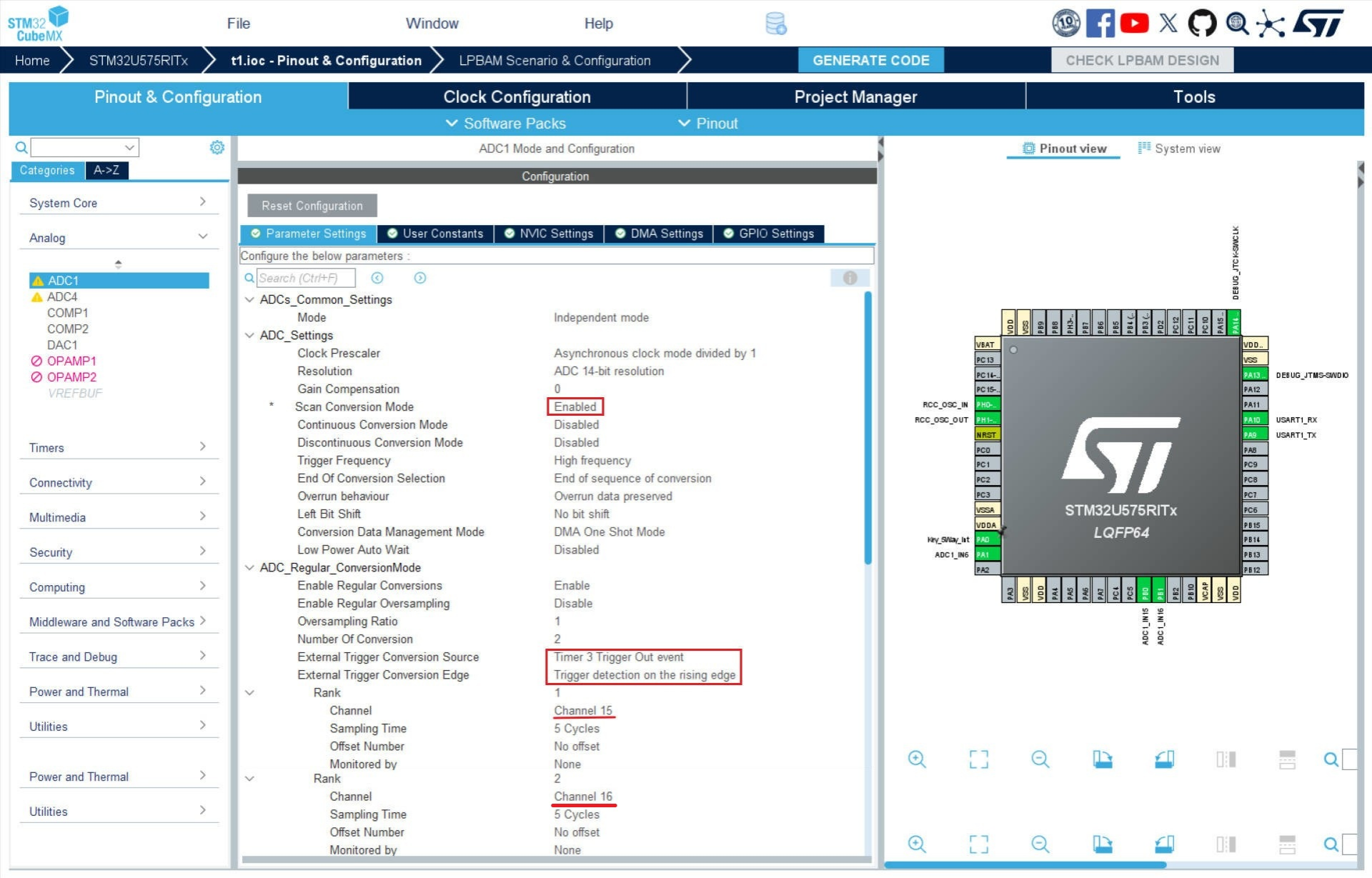

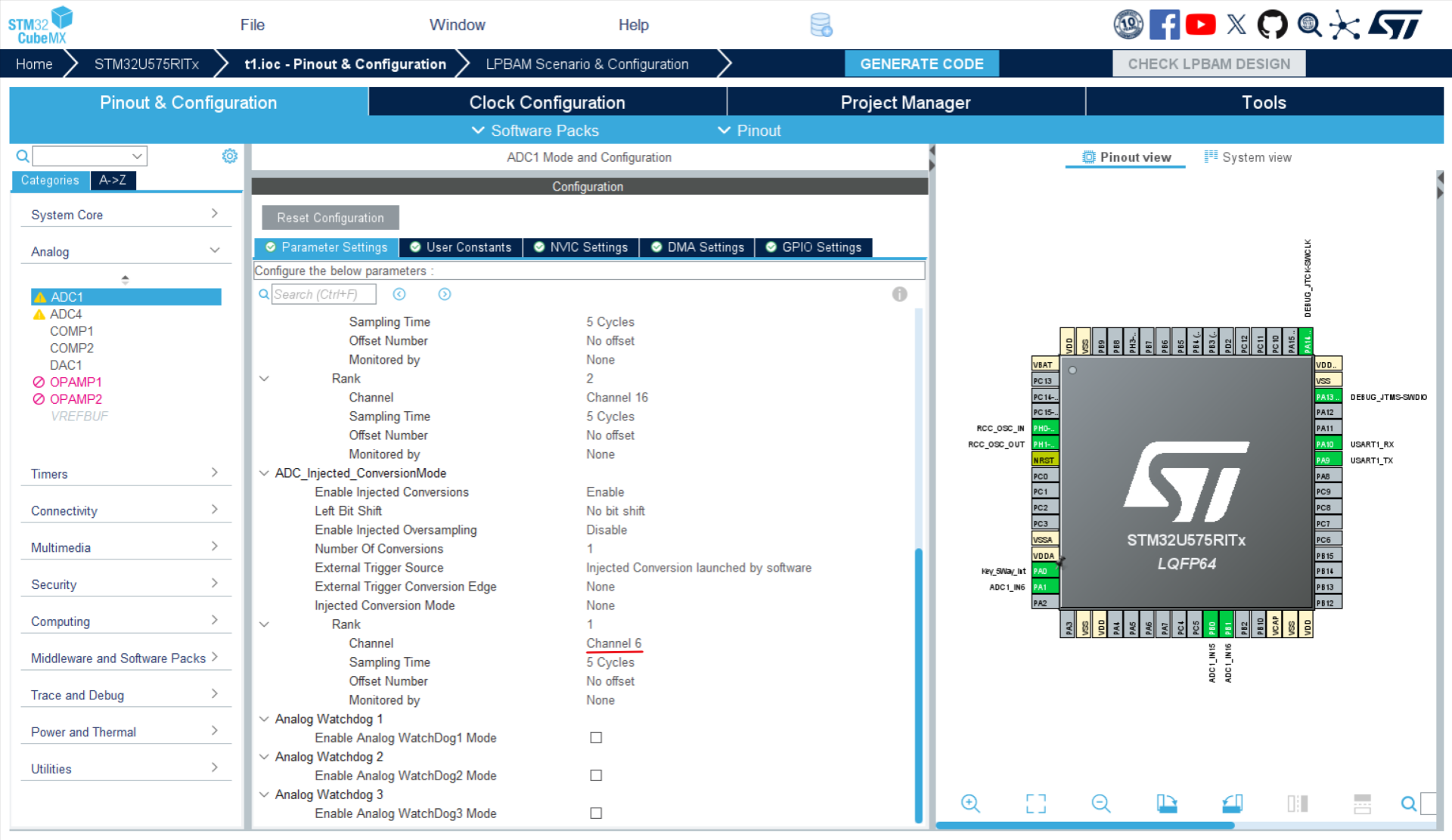

DMA用法

- 采集电流和电压ADC值,组成规则通道组使用外部定时器触发,每50ms采集1次,每采集10次,DMA方式处理后,求平均值,并打印采集结果

- 五向按键的电压输入使用注入组,在按下时,产生中断,然后在延时去抖以后,软件启动注入组的转换,根据测得的电压值,识别是哪个方向的按键被按下,通过串口打印结果

c

//打开模拟量相关处理单元电源

void HAL_PWREx_EnableVddA(void);

//启动ADC校准,CalibrationMode 可选ADC_CALIB_OFFSET 或 ADC_CALIB_OFFSET_LINEARITY

//最后一个参数单端或双端,对U575的ADC无效

HAL_StatusTypeDef HAL_ADCEx_Calibration_Start(ADC_HandleTypeDef *hadc,

uint32_t CalibrationMode,

uint32_t SingleDiff);

//阻塞(查询)方式启动ADC转换

HAL_StatusTypeDef HAL_ADC_Start(ADC_HandleTypeDef *hadc);

//获取当前ADC转换状态

__HAL_ADC_GET_FLAG(__HANDLE__, __FLAG__);

//非阻塞(中断)方式启动ADC转换

HAL_StatusTypeDef HAL_ADC_Start_IT(ADC_HandleTypeDef *hadc);

//非阻塞(DMA)方式启动ADC转换

HAL_StatusTypeDef HAL_ADC_Start_DMA(ADC_HandleTypeDef *hadc,

const uint32_t *pData,

uint32_t Length);

//获取当前ADC转换值

uint32_t HAL_ADC_GetValue(const ADC_HandleTypeDef *hadc);

//转换完成中断回调函数

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef* hadc);

//注入组阻塞(查询)方式启动ADC转换

HAL_StatusTypeDef HAL_ADCEx_InjectedStart(ADC_HandleTypeDef *hadc);

//注入组(中断)方式启动ADC转换

HAL_StatusTypeDef HAL_ADCEx_InjectedStart_IT(ADC_HandleTypeDef *hadc);

//注入组转换完成中断回调函数

void HAL_ADCEx_InjectedConvCpltCallback(ADC_HandleTypeDef *hadc);

//注入组获取当前ADC转换值

uint32_t HAL_ADCEx_InjectedGetValue(const ADC_HandleTypeDef *hadc,

uint32_t InjectedRank);