目录

[2.1 45°旋转因子](#2.1 45°旋转因子)

[2.2 高阶蝶形修正因子参数](#2.2 高阶蝶形修正因子参数)

1.引言

由于FFT16顶层一共例化了4个专用常数复数乘法子模块,全部是定点复数旋转因子乘法器,专为16点/256点FFT蝶形运算定制,无通用乘法,全部为固定系数常数乘,节省FPGA资源。

2.FFT旋转因子核心系数

2.1 45°旋转因子

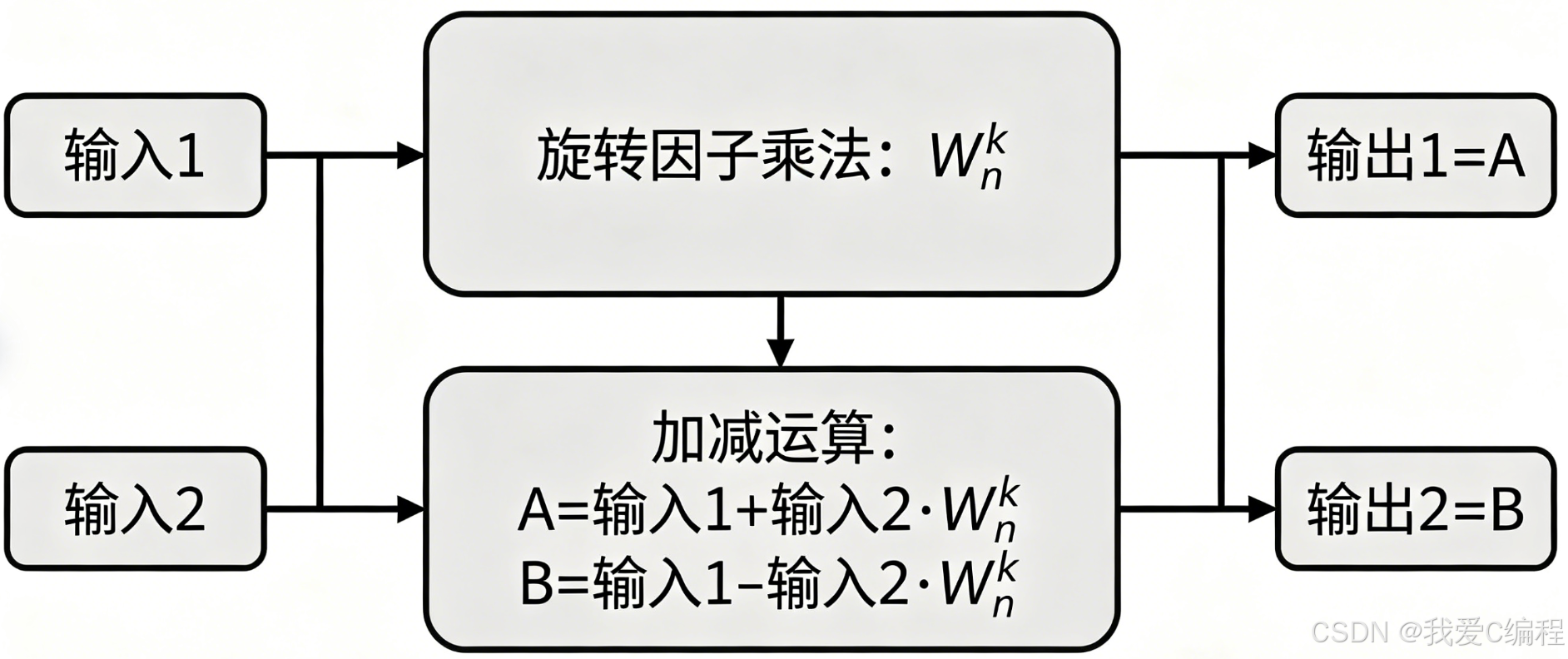

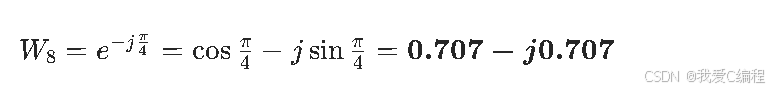

FFT旋转因子核心系数:

上述公式用于FFT中45°旋转因子的乘法运算,其负责FFT蝶形中√2/2衰减+45°相位旋转运算。

因此,我们通过verilog编写如下的程序,完成这个部分的复数运算:

module MPUC707 ( CLK,EI ,ED, MPYJ,DR,DI ,DOR ,DOI);

parameter nb=10;

input CLK ;

wire CLK ;

input EI ; //slowdown

wire EI ;

input ED; //data strobe

input MPYJ ; //the result is multiplied by -j

wire MPYJ ;

input [nb-1:0] DR ;

wire signed [nb-1:0] DR ;

input [nb-1:0] DI ;

wire signed [nb-1:0] DI ;

output [nb-1:0] DOR ;

reg [nb-1:0] DOR ;

output [nb-1:0] DOI ;

reg [nb-1:0] DOI ;

reg signed [nb+1 :0] dx5;

reg signed [nb : 0] dt;

reg signed [nb-1 : 0] dii;

wire signed [nb+2 : 0] dx5p;

wire signed [nb+3 : 0] dot;

reg edd,edd2, edd3; //delayed data enable impulse

reg mpyjd,mpyjd2,mpyjd3;

reg [nb-1:0] doo ;

reg [nb-1:0] droo ;

always @(posedge CLK)

begin

if (EI) begin

edd<=ED;

edd2<=edd;

edd3<=edd2;

mpyjd<=MPYJ;

mpyjd2<=mpyjd;

mpyjd3<=mpyjd2;

if (ED) begin

dx5<=DR+(DR <<2); //multiply by 5

dt<=DR;

dii<=DI;

end

else begin

dx5<=dii+(dii <<2); //multiply by 5

dt<=dii;

end

doo<=(dot >>>4) ;

droo<=doo;

if (edd3)

if (mpyjd3) begin

DOR<=doo;

DOI<= - droo; end

else begin

DOR<=droo;

DOI<= doo; end

end

end

assign dx5p=(dx5<<1)+(dx5>>>2); // multiply by 101101

`ifdef FFT256bitwidth_coef_high

assign dot= dx5p+(dt>>>4)+(dx5>>>13); // multiply by 10110101000000101

`else

assign dot= dx5p+(dt>>>4) ; // multiply by 10110101

`endif

endmodule

上面程序中,把0.7071分解成(5×2+5/4+1/16)/16≈0.70703125

2.2 高阶蝶形修正因子参数

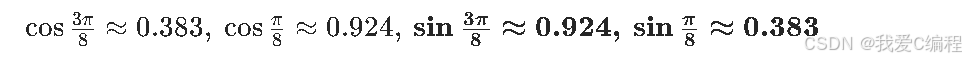

在FFT中,对应16点FFT细分旋转因子:

那么,0.924-0.383=0.541,即16点FFT八分区细分角度合成系数,用于高阶蝶形修正。

因此,我们通过verilog编写如下的程序,完成这个部分的复数运算:

module MPUC541 ( CLK,EI ,ED, MPYJ,DR,DI ,DOR ,DOI);

parameter nb=10;

input CLK ;

wire CLK ;

input EI ;

wire EI ;

input ED; //data strobe

input MPYJ ; //the result is multiplied by -j

wire MPYJ ;

input [nb-1:0] DR ;

wire signed [nb-1:0] DR ;

input [nb-1:0] DI ;

wire signed [nb-1:0] DI ;

output [nb-1:0] DOR ;

reg [nb-1:0] DOR ;

output [nb-1:0] DOI ;

reg [nb-1:0] DOI ;

reg signed [nb :0] dx5;

reg signed [nb :0] dx3;

reg signed [nb-1 :0] dii;

reg signed [nb-1 : 0] dt;

wire signed [nb+1 : 0] dx5p;

wire signed [nb+1 : 0] dot;

reg edd,edd2, edd3; //delayed data enable impulse

reg mpyjd,mpyjd2,mpyjd3;

reg [nb-1:0] doo ;

reg [nb-1:0] droo ;

always @(posedge CLK)

begin

if (EI) begin

edd<=ED;

edd2<=edd;

edd3<=edd2;

mpyjd<=MPYJ;

mpyjd2<=mpyjd;

mpyjd3<=mpyjd2;

if (ED) begin // 0_1000_1010_1000_11

dx5<=DR+(DR >>>2); //multiply by 5

dx3<=DR+(DR >>>1); //multiply by 3,

dt<=DR;

dii<=DI;

end

else begin

dx5<=dii+(dii >>>2); //multiply by 5

dx3<=dii +(dii >>>1); //multiply by 3

dt<=dii;

end

doo<=dot >>>2;

droo<=doo;

if (edd3)

if (mpyjd3) begin

DOR<=doo;

DOI<= - droo; end

else begin

DOR<=droo;

DOI<= doo; end

end

end

assign dx5p=(dt<<1)+(dx5>>>3); // multiply by 0_1000_101

`ifdef FFT256bitwidth_coef_high

assign dot= (dx5p+(dt>>>7) +(dx3>>>11));// multiply by // 0_1000_1010_1000_11

`else

assign dot= dx5p+(dt>>>7);

`endif

endmodule

在上述程序中,0.5411的二进制移位运算方式如下:

0.5411 ≈ 0.5410

=2.1640625/4

=(2 + 0.15625 + 0.0078125)/4

=(2 + 1.25/8 + 1/128)/4