地分割

- Grounding in mixed-signal systems demystified, Part 2描述了 PCB 设计中关于回流路径(Return Path)和地平面分割(Split Ground Planes)。

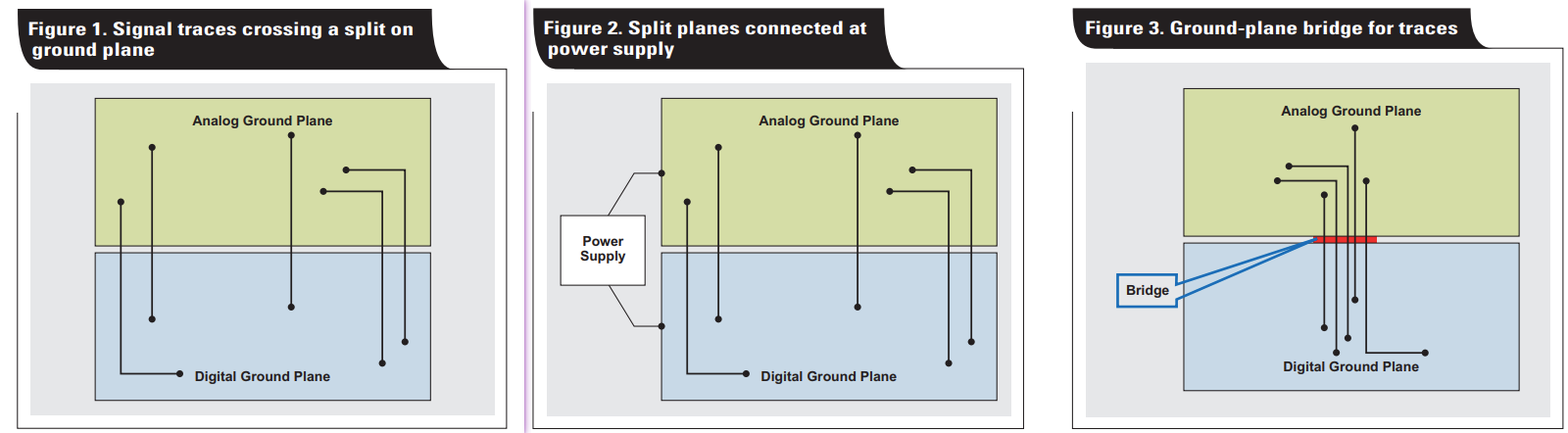

跨沟槽走线的(Figure 1 & 2 的情况)

-

分割了地平面,却又让信号线直接跨过那条"沟壑"时,就会发生以下情况:

- 阻抗不连续: 信号在跨越分割线时,其参考平面突然消失,导致瞬时阻抗剧增,引发严重的信号反射。

- 巨大的环路面积: 高频信号的回流总是寻找最低电感(即信号线正下方)的路径。如果下方断开了,回流必须绕行至两地连接的那个"单点连接处",形成一个巨大的环路天线。

"桥接"布局法 (Figure 3 的方案)

- 建设"桥梁": 在分割线上保留一块连通的区域(通常是铺铜),这就是所谓的"桥"。

- 垂直过桥: 所有跨越两个平面的信号线必须聚集在一起,并从这个"桥"的正上方通过。这样回流电流就能在信号线正下方的"桥"上通过,保持极小的环路面积。

- 连接点位置: * 如果必须单点接地,这个连接点(电阻/磁珠/桥)应该放在 ADC 芯片的下方或紧挨着它,而不是放在遥远的电源输入端。

"无地"传输方案 --- 切断回流对参考平面的依赖

- 差分对走线: 正如你之前问到的 V c m = 1.1 V V_{cm}=1.1V Vcm=1.1V 场景,如果使用真正的差分信号(如 LVDS、CML),回流电流主要在彼此之间流动,对地平面的依赖度降低。

- 光耦/变压器隔离: 这是最彻底的隔离,信号通过光或磁耦合,两端的参考地完全没有任何电气连接,从根本上消除了地环路。

地平面不分割

- 现代高速设计中,越来越多的专家建议使用统一的完整地平面 。

- 做法是:通过分区(Partitioning)而非分割(Splitting)。将模拟元件放一堆,数字元件放一堆,只要它们的信号线不互相乱穿,回流电流自然会保持在各自区域下方,互不干扰。

电源分割

"地不分、电源分"方案

-

回流路径的完整性: 正如你之前引用的文字所说,地平面一旦分割,信号线跨越时回流路径就会乱套。保持统一的地平面可以为所有信号(无论是数字还是模拟)提供阻抗最低、路径最短的回流通道。

-

电源隔离的必要性: 数字电源(3.3V)上布满了高频开关噪声,而模拟电源(A3V3)需要较高纯净度。通过桥接(电阻、磁珠或 π \pi π 滤波器)对电源进行物理分割,可以从源头上阻断噪声通过电源平面耦合。

-

物理分区: 将 PCB 划分为"模拟区"和"数字区"。将所有模拟元件(ADC、参考源、运放)放在一边,数字元件(MCU、FPGA、晶振)放在另一边。

-

回流自然隔离: 高频电流会倾向于在走线正下方的地平面回流。只要模拟信号线不走入数字区,数字信号线不走入模拟区,它们的回流在地平面上就是天然分开的,不会互相干扰。

示例

- 数字电路在开关切换时会产生大量的瞬态电流和高频噪声。如果直接将数字电源和模拟电源连在一起,这些噪声会直接干扰对噪声极其敏感的模拟电路(如 ADC、DAC 或传感器放大器)。可将数字电源(3.3V)通过一个 10 Ω 10 \Omega 10Ω 的电阻(R33)连接到模拟电源(A3V3)。

抑制高频噪声(PI/SI 优化)

- 低通滤波: 电阻与模拟平面上的去耦电容(通常 A3V3 后面会接电容到地)共同构成了一个简单的 RC 低通滤波器。它能有效滤除来自数字电源的高频干扰。

单点连接(Single Point Grounding/Powering)

- 物理隔离: 这强迫电流流经指定的路径,而不是在电源平面之间随意穿流,有助于保持模拟平面的"干净"。

| 桥接元件 | 核心优势 | 缺点 | 推荐应用场景 |

|---|---|---|---|

| 磁珠 (Default) | 滤除高频开关噪声 | 可能产生 LC 谐振 | 大多数混合信号系统 (MCU/RF) |

| 小电阻 (1-10 Ω \Omega Ω) | 抑制振铃,提供阻尼 | 会产生直流压降 | 极高精度的传感器采集 (低功耗) |

| 0 Ω 0 \Omega 0Ω 电阻 | 物理分区,无压降 | 基本没有噪声滤波能力 | 一般消费电子,对成本敏感 |

| 电感 ( 1 μ H 1 \mu H 1μH) | 极强的低频滤波 | 体积大,易受磁场干扰 | 功率较大的模拟驱动电路 |

布局提醒:

-

输入端: 靠近数字电源源头。

-

输出端: 紧接着(可选)放置 10uF + 0.1uF 的并联电容,且电容的地要直接连到模拟地平面上。

-

桥接位置: 桥接元件(如磁珠或 10 Ω 10 \Omega 10Ω 电阻)应放置在模拟区和数字区的边界处。

-

局部铺铜: A3V3 应该在模拟区单独铺设一个小的电源平面(Power Island)。这个小岛通过桥接元件从主 3.3V 平面取电。

-

去耦接地: A3V3 下方的去耦电容(10uF/0.1uF)的地焊盘应直接连到统一的地平面上。由于这些电容靠近模拟芯片,它们的噪声会直接泻入模拟区下方的地,而不会流向数字区。

| 风险点 | 描述 | 对策 |

|---|---|---|

| 跨区走线 | 数字信号线如果穿过模拟区的地,会污染模拟参考地。 | 严禁跨区: 任何数字信号走线不得进入模拟器件下方的地层区域。 |

| LC 谐振 | 使用 π \pi π 滤波器时,无阻尼 LC 可能引起电压振铃。 | 增加阻尼: 使用磁珠代替纯电感,或在电解电容旁并联陶瓷电容(利用电解电容的 ESR 提供阻尼)。 |

| 混合信号芯片 | 像 ADC 这种既有 AGND 又有 DGND 的芯片。 | 单点汇合: 将芯片的 AGND 和 DGND 引脚直接连到芯片下方的统一地平面上。 |

CG

- Input Filter Design for Switching Power Supplies

- π型滤波器是一种LC滤波器,其LC元件排列成希腊字母"π"的形状。π型滤波器可以配置为高通滤波器或低通滤波器。由于这些滤波器包含三个L或C元件,因此它们本质上是三阶滤波器,并且在截止频率以上具有很强的滚降特性(约20 dB/十倍频程)。标准实现方式是作为低通滤波器,这使得该电路可以用作直流电源输入的高阶滤波器。

- π型滤波器的低通版本能够有效去除高频噪声,因此可用作非稳压电源的强滤波器。低通版本也可作为稳压电路的输入滤波器。

- π型滤波器电路设计公式和计算器

- 分割电源层:何时以及为何要分割PCB的电源

- 为确保设计符合数据手册规范,您应遵循以下几条准则。首先,一个由来已久的问题:"AGND 和 DGND 接地层是否应该分开?" 简而言之:视情况而定。详细来说:通常不建议这样做。为什么呢?在大多数情况下,分割接地层弊大于利,因为分割接地层只会增加回流电流的电感。还记得公式 V = L(di/dt) 吗?电感越大,电压噪声也越大。随着开关电流的增加(而随着转换器采样率的提高,开关电流必然会增加),电压噪声也会增加。因此,除非有特殊原因,否则请保持接地连接。

- How to filter the input of a high-side current sensing

- https://www.eeworldonline.com/choosing-inductors-ferrite-beads-power-supply-filtering-faq/

- https://ww1.microchip.com/downloads/aemDocuments/documents/FPGA/ProductDocuments/BoardDesignFiles/Microchip_SmartFusion2_and_IGLOO2_Board_and_Layout_Design_Guidelines_AN4153_VC.pdf

- Ground in PCB Layout - Separate or Not Separate? (with Rick Hartley)