一、 概述

本章节通过仿真来观察EDID的读取数据波形,可以观察主机与从机的交互流程。

二、仿真示例

仿真模块:给主机和从机产生50MHz时钟和复位。

`timescale 1ns / 1ps

module ddr_tb(

);

reg sclk;

reg reset_n;

wire hdmi_rx_hpd;

wire hdmi_rx_ten;

wire scl;

wire sda;

initial begin

sclk = 0;

reset_n = 0;

#1000;

sclk = 1;

reset_n = 1;

end

always # 10 sclk = ~sclk;

ddc_ctrl inst_ddc_ctrl (

.sclk (sclk),

.reset_n (reset_n),

.hdmi_rx_hpd (hdmi_rx_hpd),

.hdmi_rx_ten (hdmi_rx_ten),

.scl (scl),

.sda (sda)

);

ddc_master inst_ddc_master (

.sclk (sclk),

.reset_n (reset_n),

.hdmi_rx_hpd (hdmi_rx_hpd),

.hdmi_rx_ten (hdmi_rx_ten),

.scl (scl),

.sda (sda)

);Endmodule

DDC主设备模块(主动读取EDID),ddc_master.v模块。

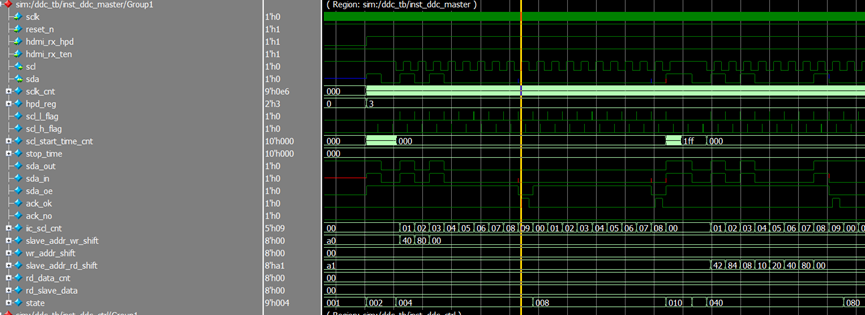

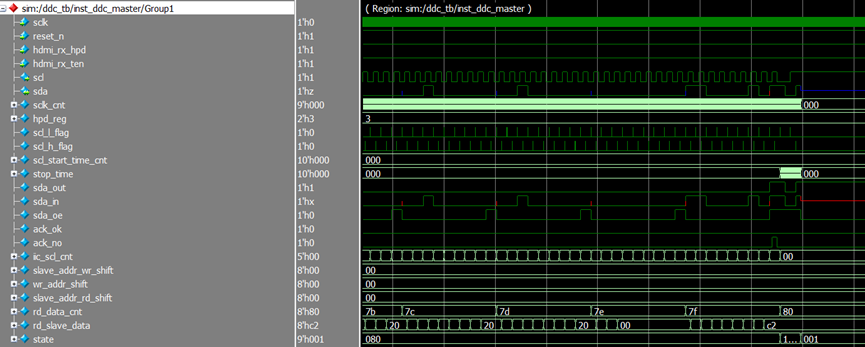

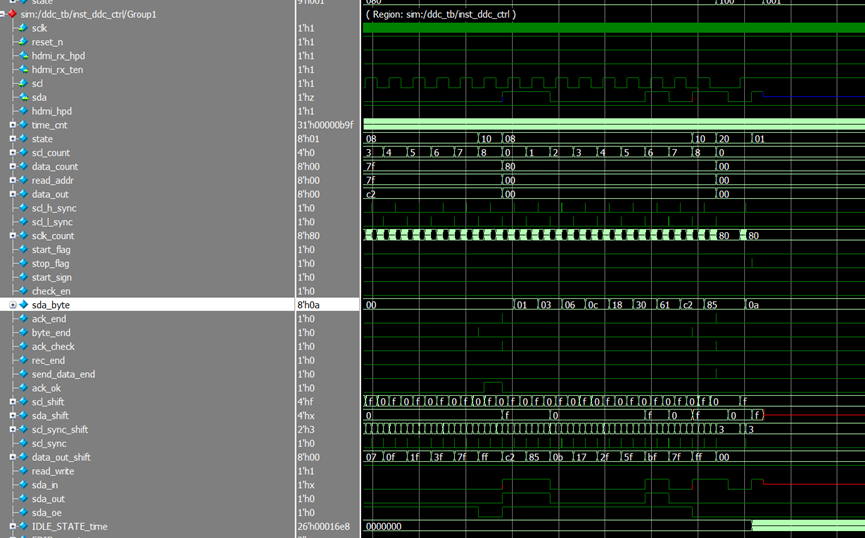

主机启动读指令波形:

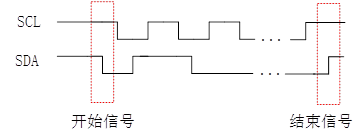

上图为主机通过IIC协议启动读取的波形,先发出启动信号,再发起虚拟写入操作,写入器件地址0,'hA0为写指令,之后写入寄存器地址'h00。再开始读寄存器,'hA1为读指令。

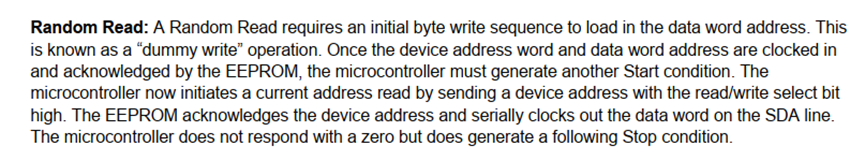

1、主机读取数据波形:

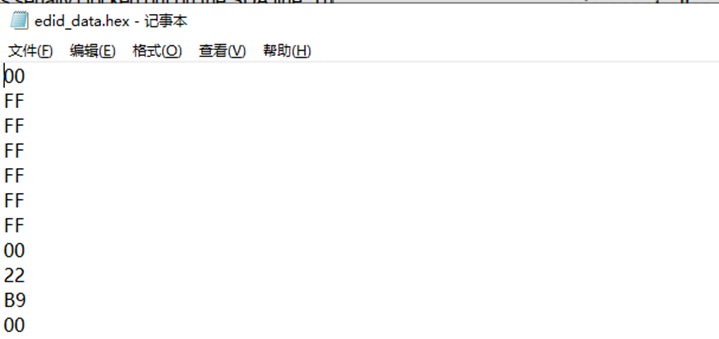

主机输入读指令后,开始读取数据,根据sda的二进制数据,可以看出第一个字节为00,后边为6个ff,后边依次跟着edid的数据。

结束读数据波形:

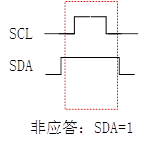

当最后的EDID数据读出来后,发起不应答信号(将sda_out拉高),输出sda位1,表示非应答,之后再产生停止指令。定值指令是指在SCL为高时,出现SDA上升沿表示停止信号。

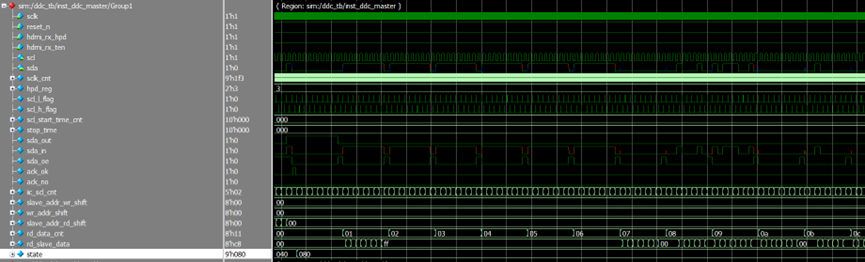

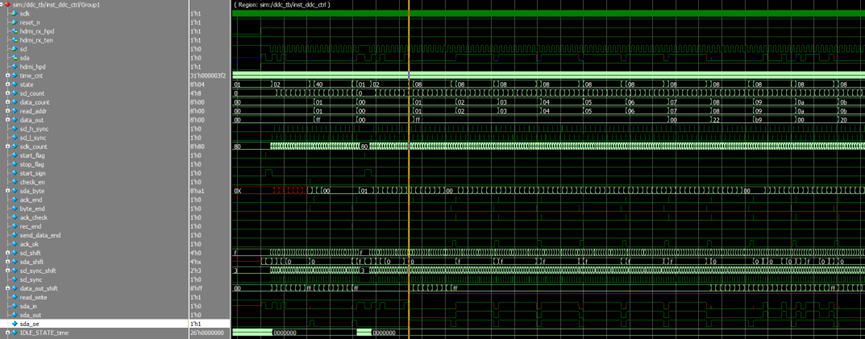

2、从机被读取数据波形:

Sda_oe为高时表示可以把sda_out作为sda发送,作为被读取的从机接口,需要做好从机应答过程。并输入被读取数据。输入的数据就是EDID数据。

在从机发送EDID数据的最后,接收到不应答标志,再接收到停止标志表示读取完成。

三、总结

本章节给出了IIC协议的主机和从机的读数据的仿真流程,ddc_ctrl:作为从设备,存储并提供EDID数据,ddc_master:作为主设备,主动读取显示设备的EDID。

本文章由威三学社出品

对课程感兴趣可以私信联系