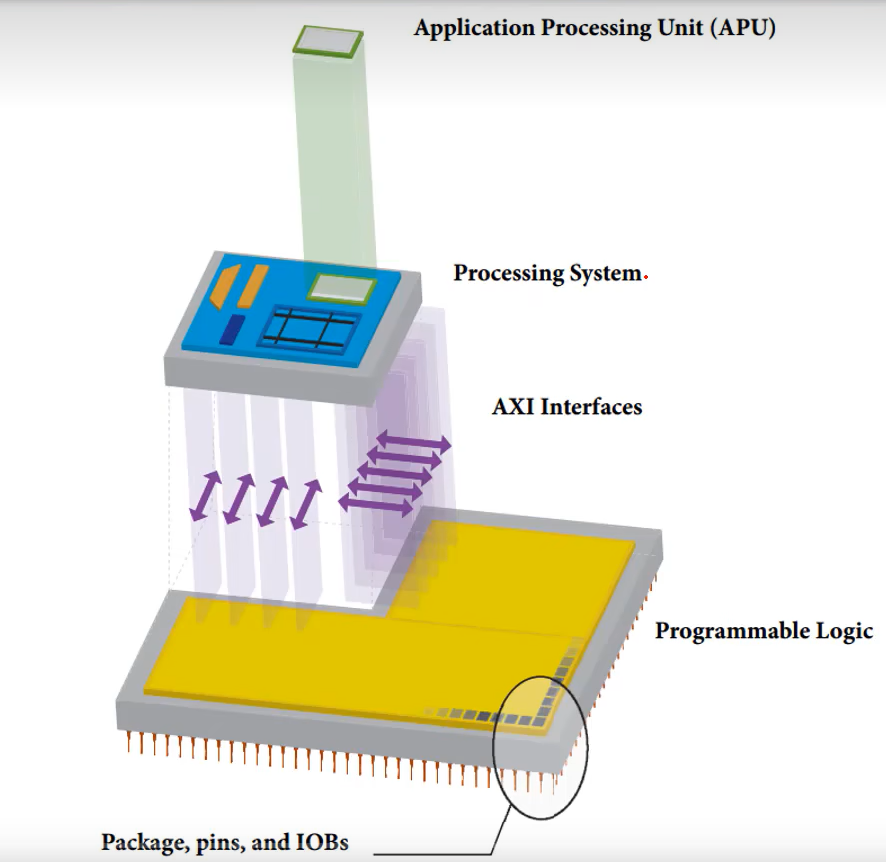

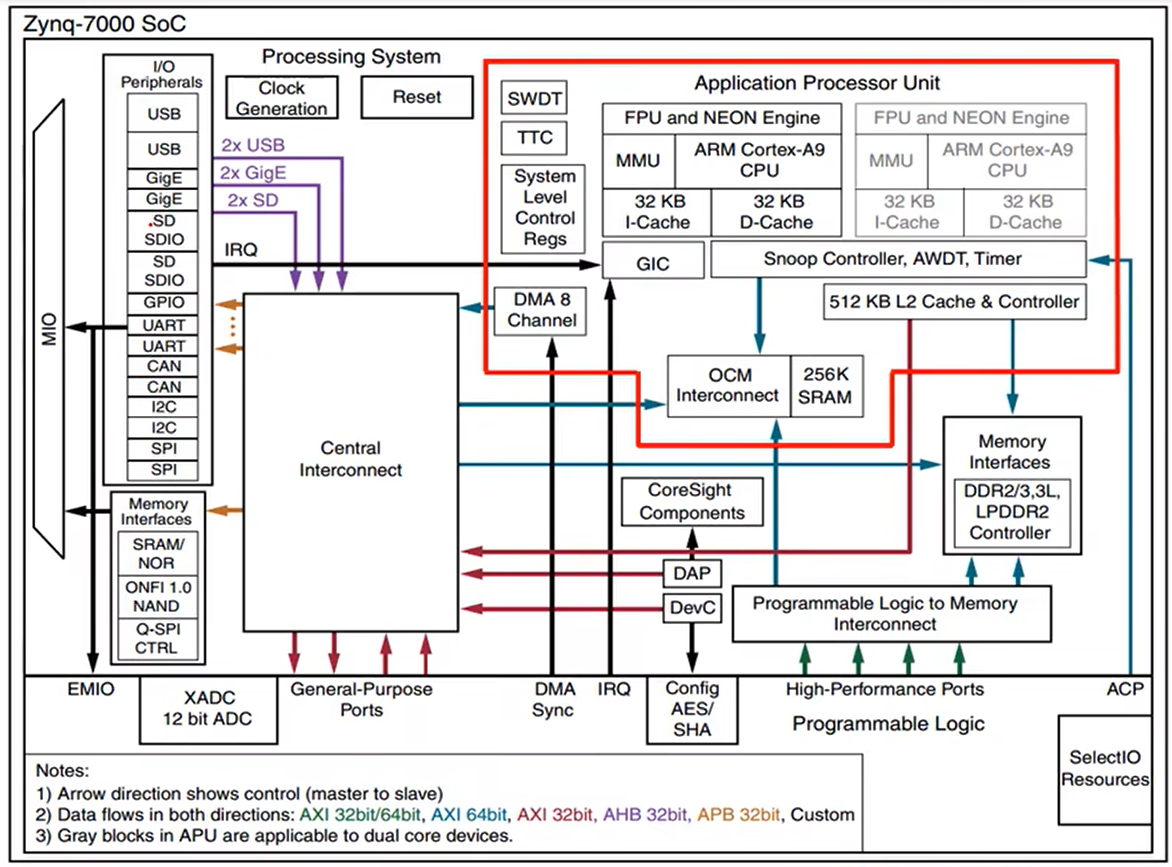

ZYNQ的本质特征,是它组合了一个双核ARM Cortex-A9处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件

Zynq整体架构图

- PS部分(Processing System)以Cortex A9 双核为核心

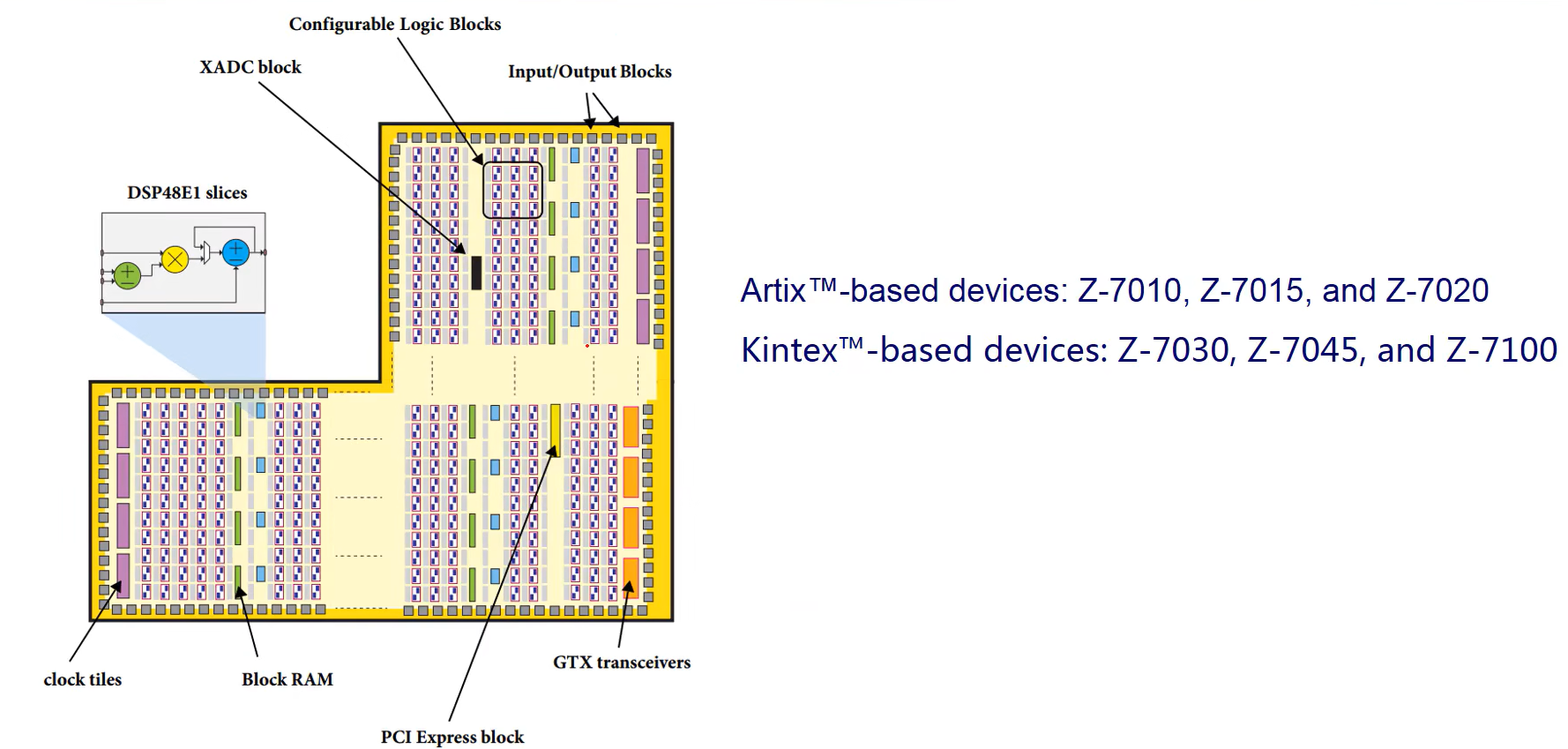

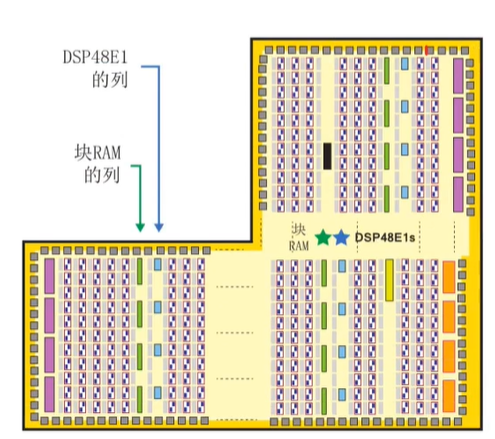

PL架构

-

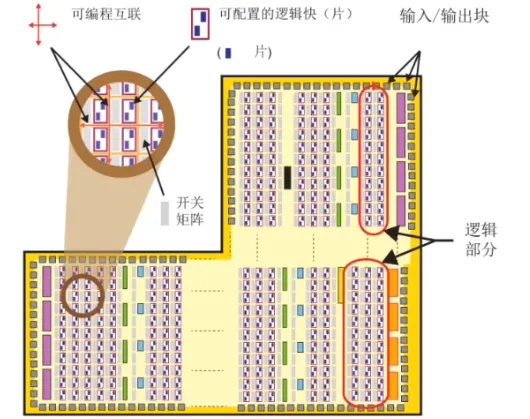

FPGA 是由逻辑片和可配置逻辑块(Configurable Logic Block,CLB)组成的,另外还有用于接口的输入 / 输出块 (Input/Output Block,IOB)(Xilinx 专有术语)

-

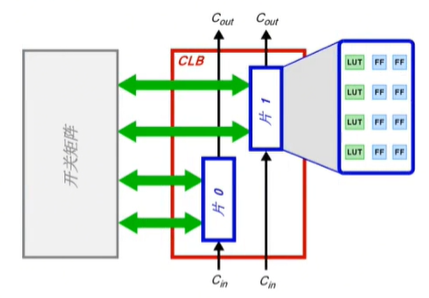

Configurable Logic Blocks,可配置逻辑块 (CLB) --- CLB 是逻辑单元的小规模、普通编组,在 PL 中排列为一个二维阵列,通过可编程互联连接到其他类似的资源。每个 CLB 里包含两个逻辑片,并且紧邻一个开关矩阵(逻辑块相邻区域,即下图灰色部分)。

-

开关矩阵如下图所示

-

片(Slice):CLB 里的一个子单元,里面有实现组合和时序逻辑电路的资源。Zynq 的片是由 4 个查找表、8 个触发器和其他一些逻辑组成。

-

LUT(Look-Up Table,查找表)------LUT 是一种用"存储 + 查表"的方式来实现任意组合逻辑的硬件结构。它不是直接用物理门电路(如与门、或门)搭建逻辑,而是通过预先存储所有可能的输入组合对应的输出结果,再根据实际输入去"查表"得到输出。图片中的文字信息如下:

- 查找表作为一个灵活的资源,可以实现

(一)至多6个输入的逻辑函数;

(二)一小片只读存储器(ROM);

(三)一小片随机访问存储器(RAM);

(四)一个移位寄存器。

LUT 可以按需组合起来形成更大的逻辑函数、存储器或移位寄存器。

- 查找表作为一个灵活的资源,可以实现

-

触发器(Flip-flop,FF):一个实现 1 位寄存的时序电路,带有复位功能。FF 的一种用处是实现锁存。(一个片上含有8个FF触发器)

-

开关矩阵 (Switch Matrix):每个 CLB 旁都有一个开关矩阵,实现灵活的布线功能(一)连接 CLB 内的单元;(二)把一个 CLB 与 PL 内的其他资源连接起来。(图示灰色部分)

-

进位逻辑 (Carry Logic):算术电路需要在相邻的片之间传递信号,就是通过进位逻辑来实现的。进位逻辑把布线和复用器组成链条来连接一个垂直列上的片。

-

输入/输出块 (Input/Output Blocks,IOB):IOB实现了PL逻辑资源之间的对接,并且提供物理设备"焊盘"来连接外部电路。每个IOB可以处理一位的输入或输出信号。IOB通常位于芯片的周边。

-

在实际设计中,大多数情况下不需要专门地指定这些资源,因为赛灵思工具会自动根据设计来安排所需的 LUT、FF、IOB 等,然后做相应的映射。

-

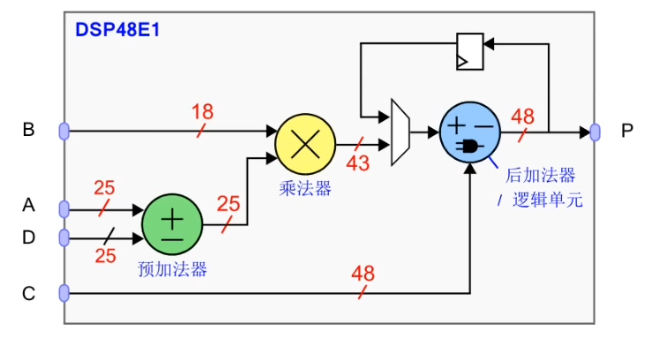

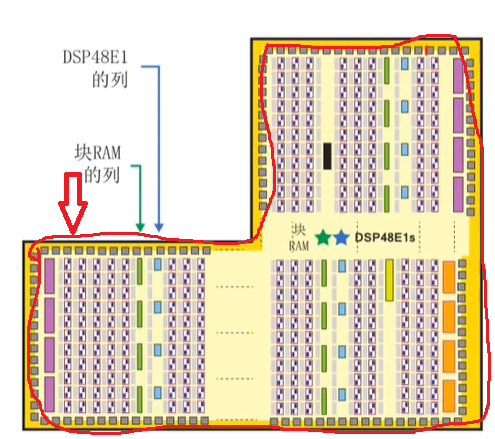

特殊资源 DSP48E1 和块 RAM

(下图绿色部分为RAM,蓝色部分为DSP48E1)

除了通用的部分,还有两个特殊用途的部件:满足密集存储需要的块 RAM 和用于高速算术的 DSP48E1 片。这两个资源都按列排列集成在逻辑阵列中。

- Zynq-7000 里的块 RAM 和 Xilinx 7 系列 FPGA 里的那些块 RAM 是等同的,它们可以实现 RAM、ROM 和先入先出 FIFO 缓冲器,同时还支持纠错编码(Error Correction Coding,ECC)。

- 每个块 RAM 可以存储最多 36KB 的信息,并且可以被配置为一个 36KB 的 RAM 或两个独立的 18KB RAM,把两个或多个块 RAM 组合起来可以形成更大的存储容量。

- 使用块 RAM 就意味着能在芯片内优化的专用存储单元内,用很小的物理空间储存大量的数据,另一种办法是分布式 RAM(Distributed RAM),这是用逻辑部分里的 LUT 来搭建的,块 RAM 往往还能用芯片所支持的最高时钟频率来工作。

-

DSP48E1 片架构图

-

通用输入输出 (PL外围的"黑色小方块")

- Zynq 上的通用输入 / 输出功能(IOB)合起来被称作 SelectIO 资源,它们被组织成 50 个 IOB 一组。每个 IOB 有一个焊盘,是与外部连接来做单个信号的输入或输出的。

- I/O 组被分类为高性能 HP 或高范围 HR,HP 接口的电压最高为 1.8V,通常用作连接存储器和其他芯片的高速接口,而 HR 接口允许高达 3.3V 的电压,适合做各种 IO 标准的连接。两类接口都支持单端和差分信号,单端需要一个 IOB 连接,而差分需要两个。

- 每个 IOB 还包含一个 IOSERDES 资源,可以做并行和串行数据的可编程转换(串行化和反串行化),数据可以是 2 位到 8 位的。

PS架构

- FPU:浮点运算单元

- NEON Engine:可以实现单指令多数据功能,比如处理视频图像,该引擎可以提供并行运算的算法加速(如FFT)

- MMU:内存管理单元,可以实现物理地址到虚拟地址的映射

- 32KB I-Cache:指令

- 32KB D-Cache:数据

- I-Cache和D-Cache组成了一级缓存

- 512KB L2 Cache & Controller:二级缓存,由两个处理器共用

- OCM:即On Chirp Memory(片上存储资源)

- Central Interconnect:中央互联,可以管理不同模块间的通信

- OCM Interconnect:片上存储器互联

- Programable Logic to Memory Interconnect:可编程逻辑单元到存储器互联

- Memory Interfaces:动态存储器接口(如DDR2/3,LPDDR2)

- Memory Interfaces:静态态存储器接口(如SRAM,NAND闪存),与动态存储器的区别是数据是否刷新。

- Clock Generation:时钟生成模块,产生PS内部时钟

- Reset:复位模块

- I/O Peripherals:I/O(General Purpose Input/Output)外设

- AXI Interface:PS与PL的交互接口

- MIO(Multiplexed Input/Output)是PS端与外界交互的引脚,它提供了可以灵活配置的54个引脚(表明外部设备和引脚之间的映射是需要定义的),这样的连接引脚也可以通过扩展MIO实现,EMIO并不是PS和外部连接的直接通路,而是通过共用了PL的I/O资源来实现的,当需要扩展超过54个引脚时可以使用EMIO。

- EMIO(ExtendedMIO):扩展MIO,PS使用PL的IO引脚进行扩展

- XADC:是PL里面的硬核,可以实现数模转换

- DMA Sync:可以实现PS到PL的直接存储访问

- IRQ:中断请求,可以在PL中产生一些中断传递到PS端

- DevC(Config AES/SHA):使用zynq时先启动PS,PS利用该接口配置PL

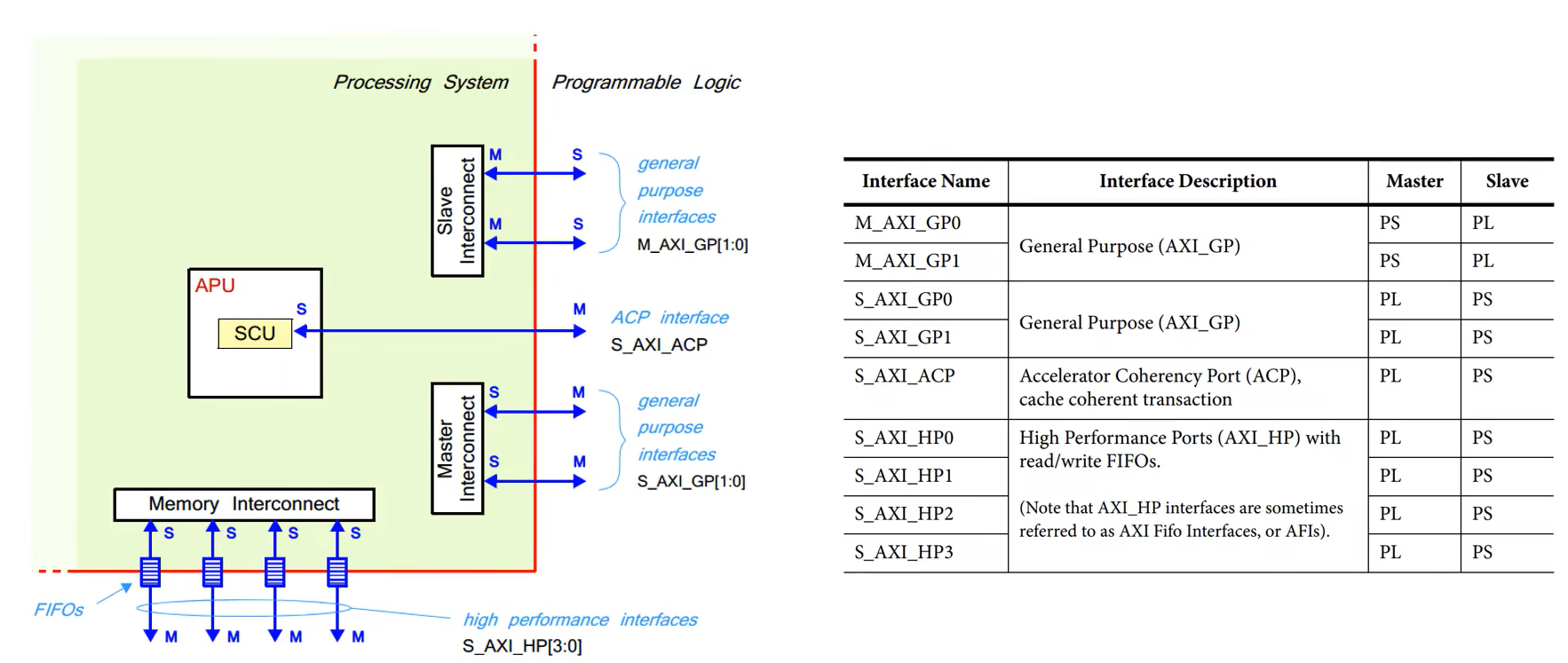

AXI简介

- General-Purpose Ports:属于AXI接口

- High-Performance Ports:高性能接口,属于AXI接口

- ACP接口:加速器一致接口,属于AXI接口,提供PL到PS存储器的低延迟访问

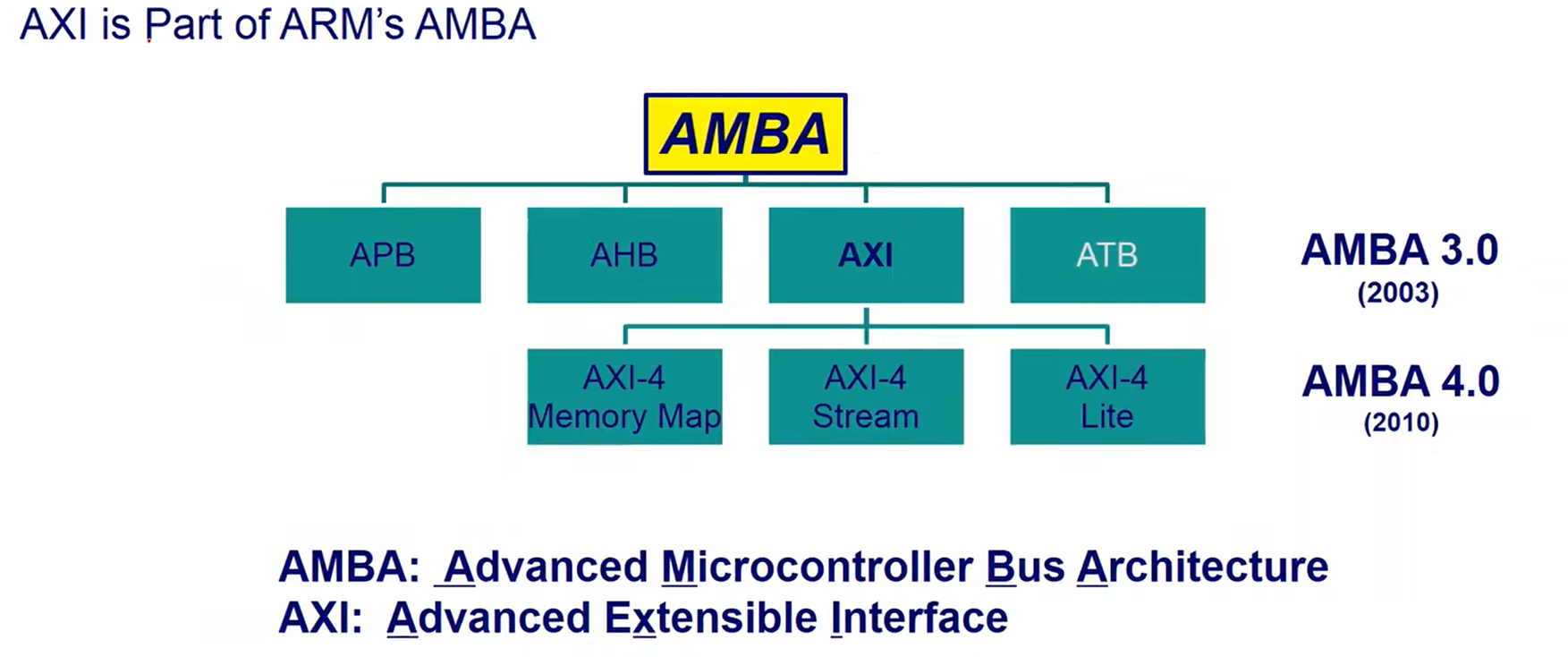

- AXI是ARM的AMBA总线的一部分

- AMBA总线即:高速微控制器总线架构

- AXI即:高级可扩展接口