本篇 PS 端 UART 和 CAN 通信 ,选自ALINX 黑金云课堂 FPGA 免费直播课。该课程由 ALINX 资深工程师团队倾力打造,从 0 到 1 系统化教学,帮助每位工程师跨过 FPGA 开发门槛。

PS 端 UART 概览

PS 端 UART 结构

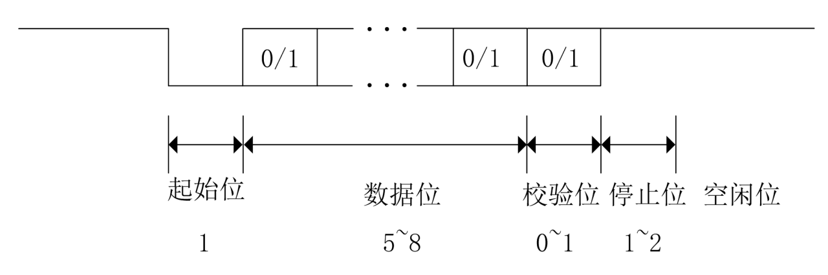

- UART 时序

全双工异步串行通信协议

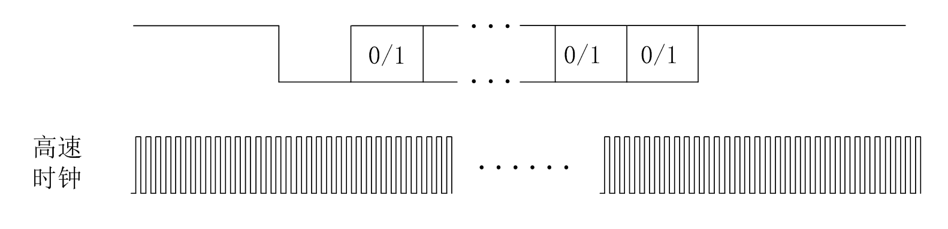

- UART 波特率

利用高速时钟产生不同的波特率,如 9600,115200 等

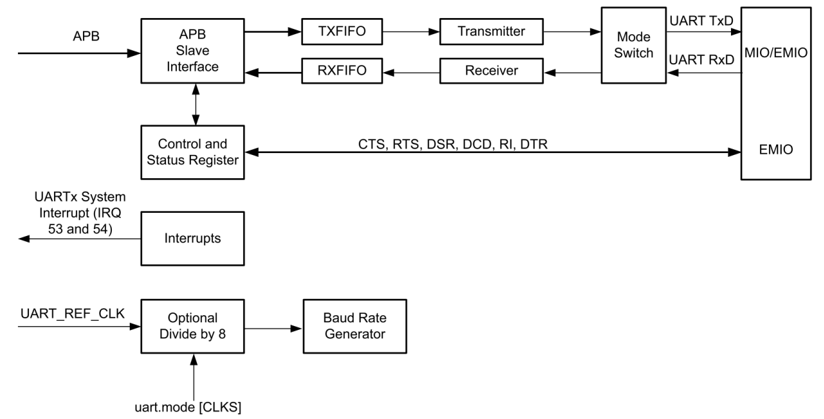

- PS 端 UART 模块

TXFIFO和RXFIFO为64字节

- PS 端 UART 读写例程

PS UART 例程详解可前往 ALINX 视频号进行课程回看。

CAN 通信

CAN 总线协议

- 协议格式

显性电平:逻辑0,低电平

隐性电平:逻辑1,高电平

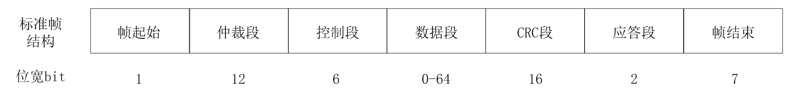

标准帧

- 帧起始:1位,由显性位(低电平)组成

- 仲裁段:11位ID和1位RTR(远程帧发送请求位)组成

- 控制段:6位,1位IDE(识别符扩展位,标准帧为显性,扩展帧为隐性),1位r0为保留位,4位DLC(数据长度),0-8字节数据

- 数据段:0-8字节

- CRC段:15位CRC数据,1位界定符(隐性)

- 应答段:2位,1位为应答间隙,1位为应答界定符。发送机发送两个隐性位,当接收机接收到有效的报文,在应答间隙向发送机发送显性位作为应答

- 帧结尾:由7个隐性位组成

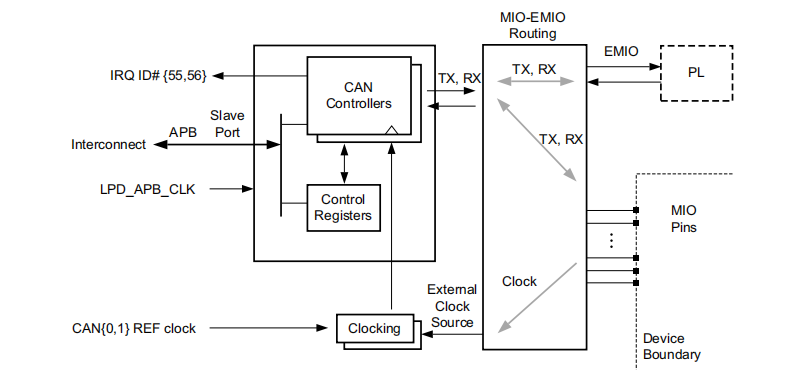

CAN 控制器结构

- CAN 控制器框图

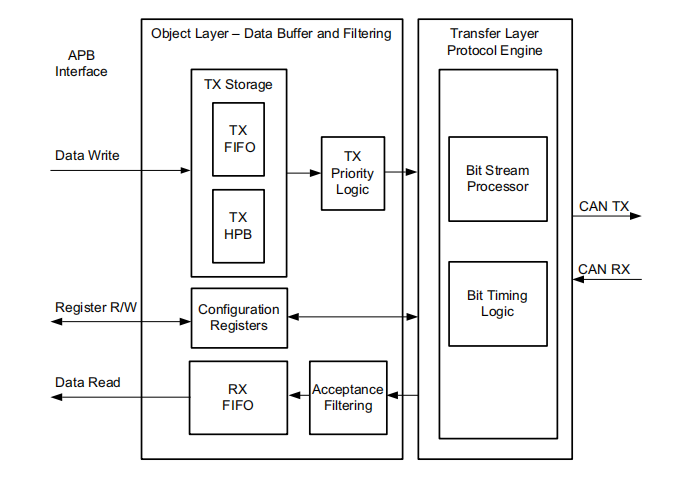

- CAN 控制器内部框图

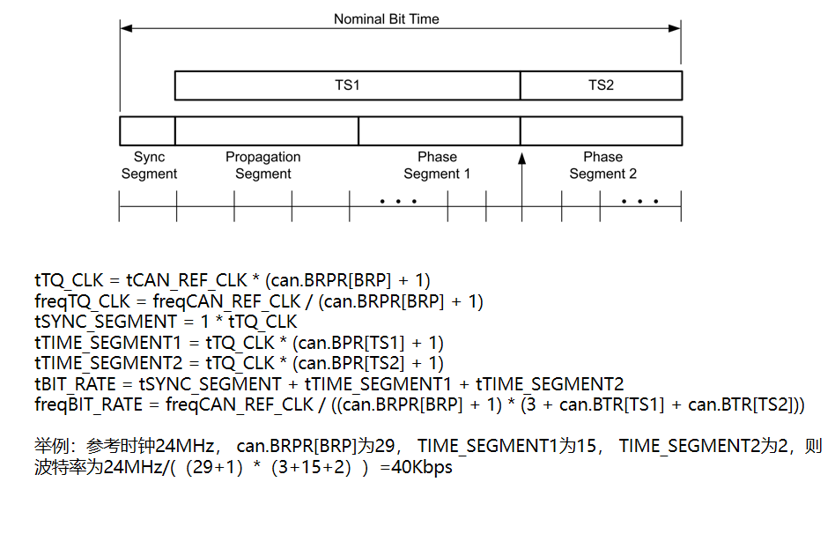

- Bit Timing Logic

更多细节欢迎关注我们黑金云课堂全年免费直播课, 黑金云课堂四月直播日历 我们将在每周二、三、四,同步推进 Verilog开发、Vitis开发、Linux开发三大系列,带你从零开始,稳扎稳打掌握 FPGA 开发全流程!

| 系列 | 内容定位 |

|---|---|

| Verilog开发 | 硬件描述语言基础、逻辑设计、仿真调试 |

| Vitis开发 | Zynq软硬件协同、外设驱动、网络协议栈 |

| Linux开发 | 嵌入式Linux系统移植、驱动编写、应用开发 |