作者:Hello,Panda

大家下午好,晚上好。这里分享一个Lattice Crosslink-NX器件通过MIPI或LVDS输入图像,并通过HDMI输出图像的案例(其实这是个比较冷门的需求,Crosslink-NX器件还是主要做MIPI桥接用)。

咱们知道,Crosslink-NX系列器件的High Speed IO作为LVDS输出时,速率最大值一般是1.25Gbps,但是咱们HDMI输出1080P60则需要IO速率达到148.5MHz×10=1.485Gbps,显示通过它的IO输出最大只能到1920×1080P30,就更别说是4K了。

那么,根据Crosslink-NX系列器件的特性,咱们在有本地显示输出需要时就会考量两种方案:

(1)第一种方案:通过MIPI DSI显示,通过MIPI接口将图像发送到MIPI屏(可能需要做横竖屏转换),一般的1080×1920/60Hz需要一组MIPI D-PHY,2160×3840/60Hz则需要两组MIPI D-PHY,这种方式只能在本地的小屏上显示,且需要做横竖屏的切换;

(2)第二种方案:通过HDMI桥接芯片输出显示到电视。这种方案目前可用的有Sil9136-3和LT9611UXC两种可选方案。Sil9136-3是BT1120转HDMI,在8bit时可实现4K 30Hz显示(输入时钟297MHz),封装是14mm×14mm,通过IIC初始化即可。LT9611UXC是国产龙迅的MIPI桥HDMI的芯片,通过2组4-Lane MIPI可实现RGB888 4K30Hz输出,YUV422 8bit 4K/60Hz输出,性能占优,封装是7.5mm×7.5mm QFN,使用前需要厂家提供一次性烧录固件。

从易用性上讲,Sil9136-3使用简单,配置容易,但是需要占用较多的IO和较大的PCB面积,性能也稍逊一点。LT9611UXC是国产芯片,调试麻烦一些,但性能稍高,IO占用少,PCB面积也少一些,总体而言,对量产产品更加有优势。

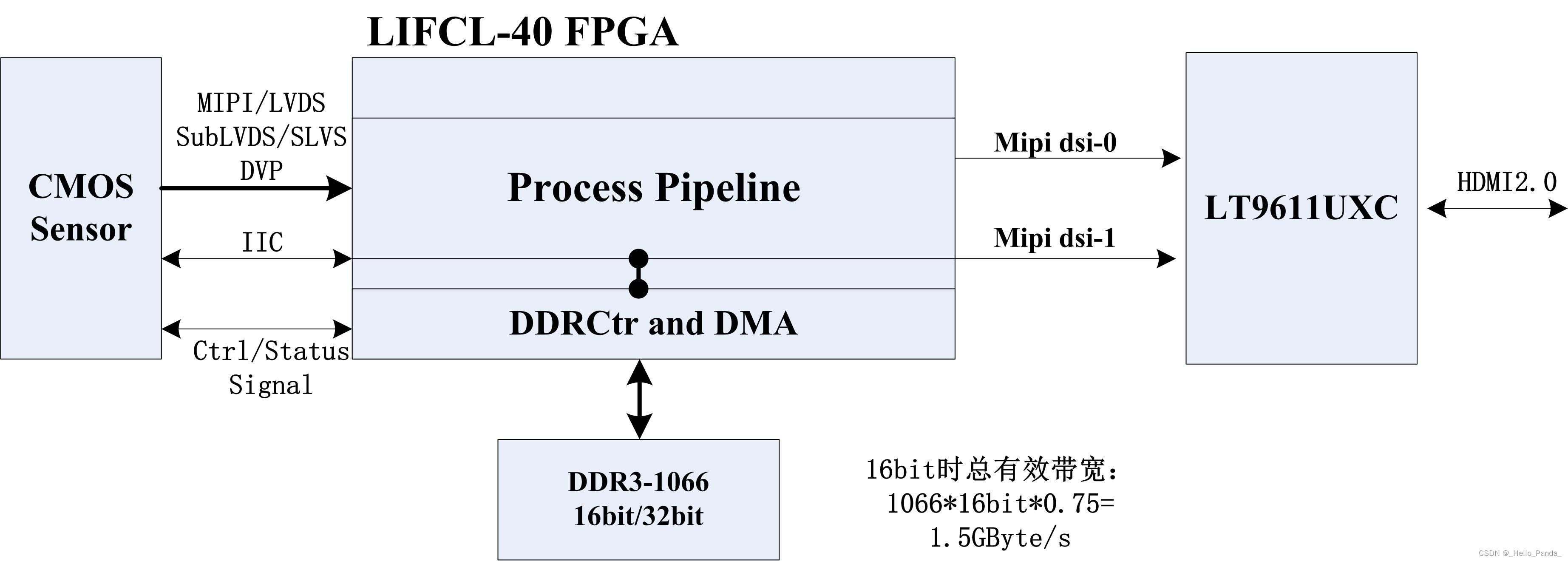

本案例就以LT9611UXC为例描述之,下图1是实现该系统的原理框图。

图1 系统原理框图

如上图1所示,Sensor将图像接收进来,经过Pipeline图像处理后,写入到DDR,MIPI DSI模块将图像数据从DDR读出经LT9611UXC转换成HDMI推到电视显示。

需要注意的是DDR的有效带宽,4K30Hz RGB888一幅图像所需带宽是3840*2160*3*30=712MByte/s,16bit DDR最多可以交互两次;如果是4K/60Hz,则需要32bit DDR。

同样的,也可以不使用DDR,具备严格行场同步的Sensor可以通过显示时序来同步Sensor的XVS和XHS,这样,只需要通过计算Pipeline的行延时精确控制即可实现时序同步,这样就无需使用DDR缓存直接显示。(当然,需要有DDR缓存需求的算法的情况除外)。

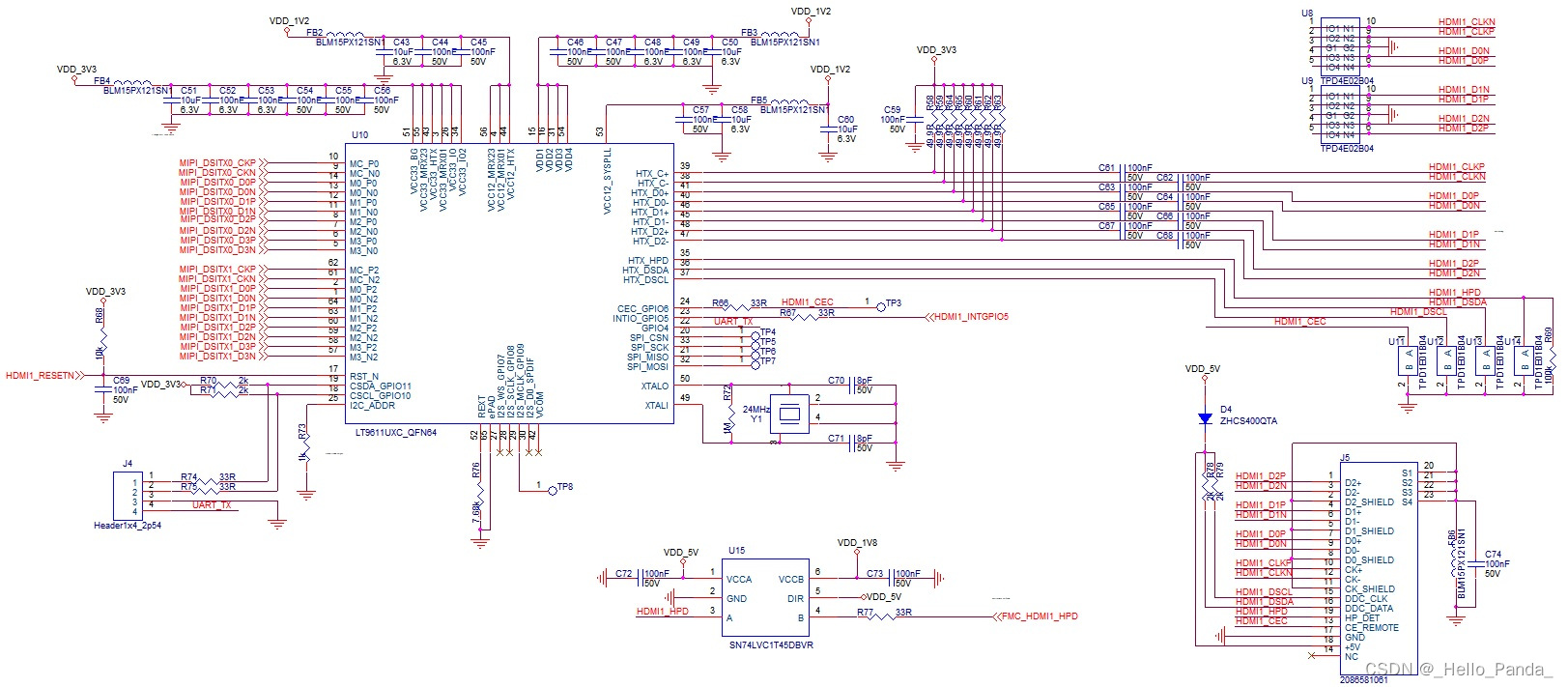

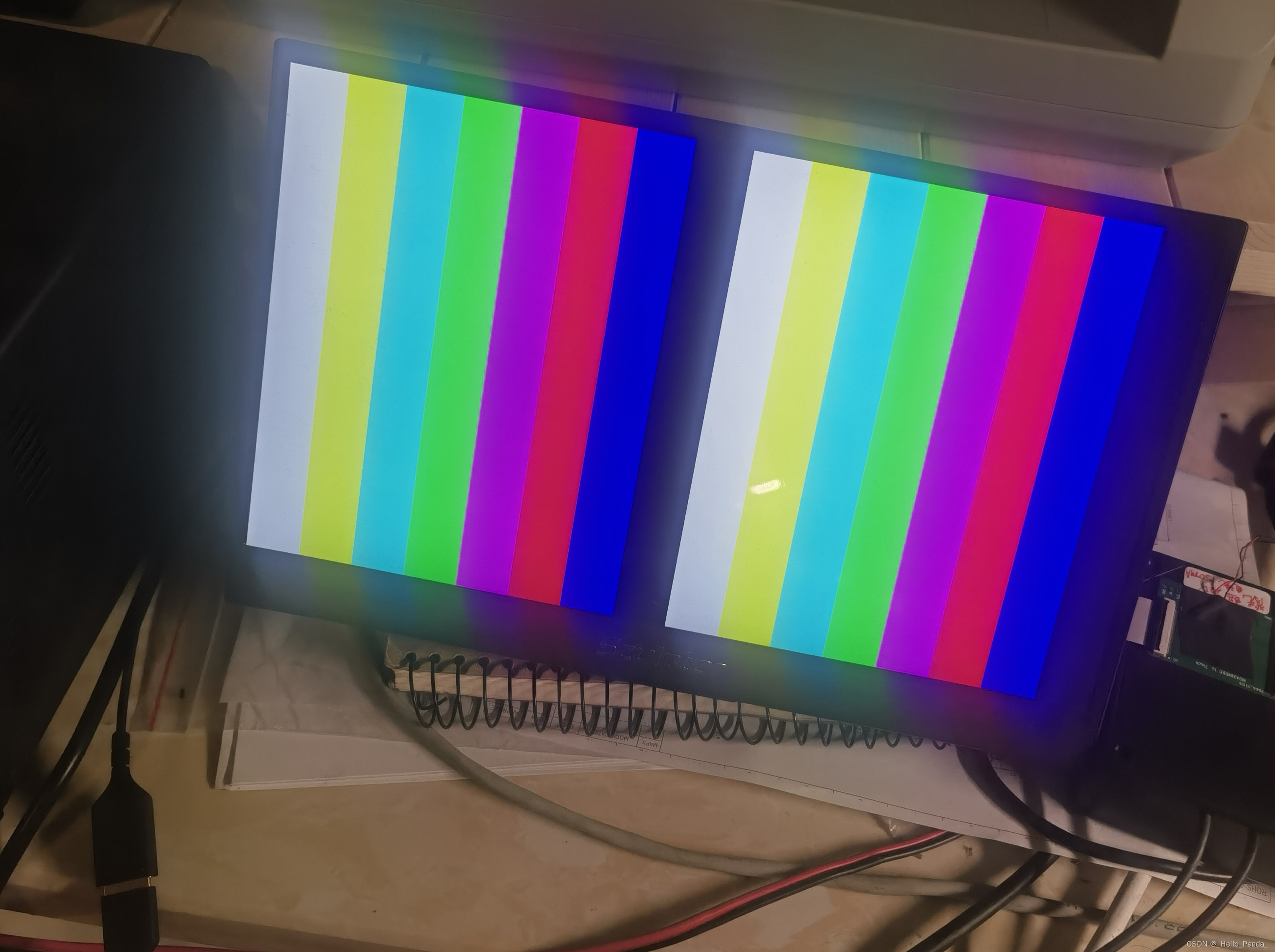

下图2是使用LT9611UXC将MIPI DSI转换成HDMI的电路原理图。图3是显示实际效果。

图2 基于LT9611UXC的MIPI DSI转HDMI电路原理图

图3 显示实际效果