前言

HDMI既可以传输视频信号,也可以传输音频信号。

HDMI接口显示使用DMT时序+TMDS编码来实现。当用FPGA控制HDMI的数据传输时,通常可以采用纯RTL实现TMDS算法或者使用专门的HDMI芯片(如ADV7513)这两种方案来完成。本文主要是介绍如何用FPGA控制ADV7513实现HDMI画面显示和音频播放。

显示器时序(DMT)标准介绍

DMT(Display Monitor Timing)是由VESA(视频电子标准协会)制定的显示器时序标准,用于定义计算机显示器的视频信号参数。是现代数字显示设备的核心规范。开发人员应遵循DMT标准使自己的设计成为符合行业标准的产品。

在深入了解DMT时序之前,首先需要掌握一些与图像相关的基本概念,如像素、分辨率、刷新率、像素时钟等。

1 图像相关的几个基本概念

像素(Pixel):是"图像元素"(Picture Element)的缩写,是构成数字图像(如照片、屏幕显示内容等)的基本单位。可以将其理解为数字图像中的 "最小点",一张图像由无数个像素按照一定规律排列组成。

分辨率:指图像的像素总量,通常以"宽度 × 高度" 的形式表示(单位为像素)。例如:一张分辨率为 640×480 的图片,意味着横向有 640 个像素,纵向有 480 个像素,总像素数307200个。常见的图像分辨率还包括 2560×1440(2K)、3840×2160(4K)等。

刷新率:刷新率是描述显示器每秒刷新画面次数的指标,单位为"赫兹(Hz)"。刷新率数值越高,动态画面越流畅,但需内容和硬件共同支持。选择时需平衡流畅需求、设备性能和功耗,例如日常使用 60Hz 足够,游戏或高频操作场景则可优先考虑 90Hz 及以上刷新率。

像素时钟(Pixel Clock):简称PCLK,是数字视频系统中用于同步像素数据传输的时钟信号。根据行同步时序以及场同步时序可以计算得到像素的时钟=水平总像素*垂直总行数*60, 比如640*480@60分辨率的像素时钟是:

800 * 525 * 60 = 25.2MHz

2 显示器时序介绍

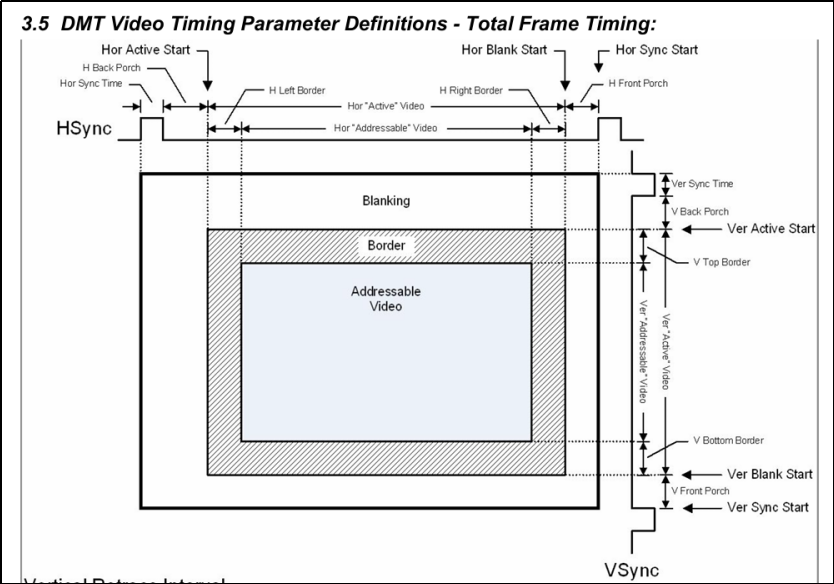

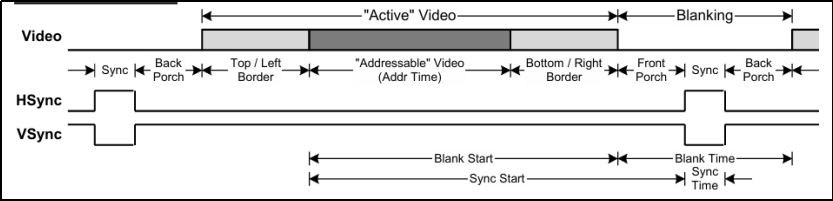

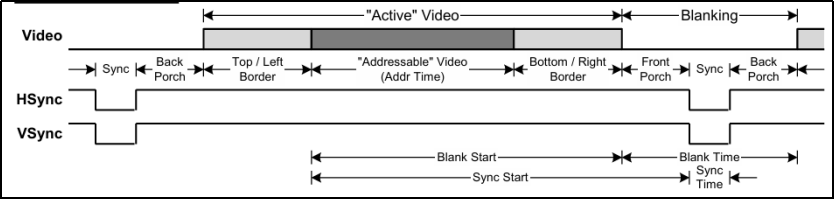

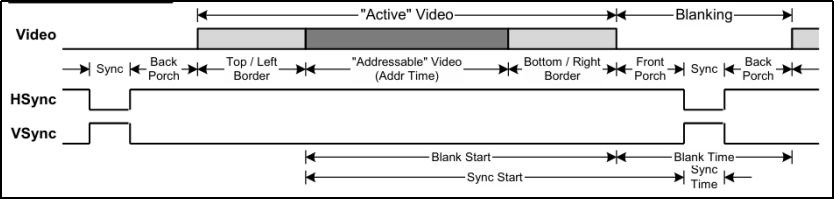

如下是DMT时序,代表显示一整帧的传输时序:

在显示器时序中,sync(同步)、porch(消隐间隔)、和 border(边框)是用于控制显示器如何逐行和逐帧绘制图像的关键参数。这些参数一起定义了每一行和每一帧图像的精确时序。

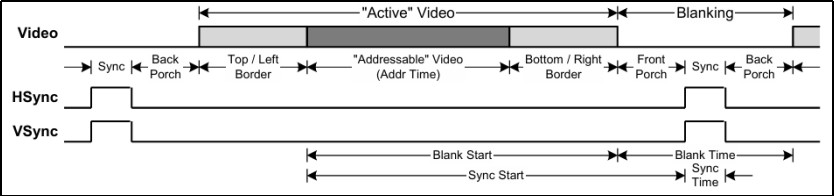

sync(同步): 同步信号分行同步(HSYNC)脉冲和场同步(VSYNC)脉冲。

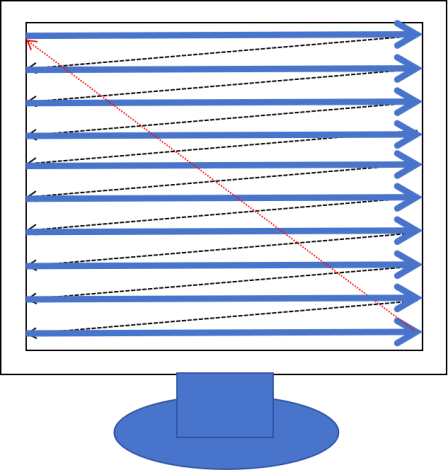

HSYNC用于控制每一行像素的开始和结束。它告诉显示器何时开始绘制新的一行。每当一行像素绘制完成时,HSYNC信号会产生一个脉冲,提示显示器移动到下一行。

VSYNC用于控制一帧图像的开始和结束。当所有行的像素都绘制完毕时,VSYNC信号产生一个脉冲,提示显示器返回到屏幕顶部,准备绘制下一帧。

**porch(消隐间隔):**在传统的CRT显示器的扫描过程中,扫描总是从显示器的左上角开始,水平向前行进,同时扫描点也以较慢的速率向下移动。当扫描点到达显示器右侧边缘时,扫描点快速返回左侧,重新开始在第1行的起点下面进行第2行扫描。当扫描完显示器上所有的行,就形成一帧,然后电子束要从显示器的右下角返回到显示器的左上角,开始新一帧的扫描。

电子束在行与行之间的返回过程以及在帧与帧之间的返回过程(从右下角返回到显示器的左上角)都称之为逆程,扫描正程期间传送图像信号,逆程期间不传送图像信号。电子束逆程扫描在荧光屏上出现回扫线,将对正程的图像造成干扰,影响图像的清晰度。因此需使显示器在行、场扫描逆程期间电子束截止,以消除行、场逆程回扫线,即实现消隐。消隐分为前消隐间隔和后消隐间隔。

-

前消隐间隔(Front Porch):有效视频之后,同步脉冲之前,为同步脉冲的清晰识别提供保障,是行/帧结束的"预告"。

-

后消隐间隔(Back Porch):同步脉冲之后,有效视频之前,提供电路稳定时间,确保准确开始绘制像素。

注:消隐间隔在CRT显示器(阴极射线管显示器)中起到了重要作用,目前为了兼容性和稳定性,消隐间隔在LCD等现代显示器中仍然保留。

border(边框): 通常就是指屏幕四周的黑边。在显示器的时序中,border(边框)区域定义了可见图像之外的部分,通常会显示为屏幕四周的黑边。这些黑边在现代显示器上通常是不可见的,或者仅在特定情况下才会出现,例如在分辨率与显示器实际尺寸不匹配时。边框是图像周围的不可见区域,通常用于在屏幕的可见显示区域和消隐间隔之间提供一个缓冲区。边框区域不显示图像数据,但它在时序中占有一定的时间,以确保图像的稳定性和完整性。避免因显示器电路处理时间不足而导致的图像抖动、扭曲或闪烁。

Addressable video: 位于中间的区域就是我们通常称为的可显示图像区域,也就是分辨率实际描述的区域。这是屏幕上实际用于显示图像内容的部分。

Polarity(极性): 是指同步信号(包括水平同步信号HSYNC和垂直同步信号VSYNC)的信号电平方向,通常标记为正极性(Positive Polarity)或负极性(Negative Polarity)。为了确保不同硬件、软件和标准之间的无缝协作,同步信号的极性有四种可选:

- 行、场同步信号正极性:

- 行同步信号正极性、场同步信号负极性:

- 行、场同步信号负极性:

- 行同步信号负极性、场同步信号正极性:

本教程选择的是行、场同步信号负极性。

3 显示器时序中不同分辨率刷新率的参数

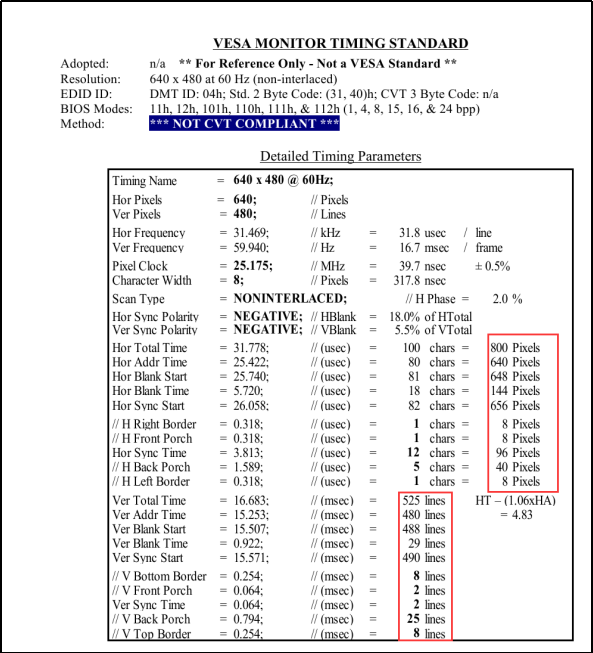

不同分辨率的时序参数各不相同。我们可以通过查阅DMT 文档(下载地址https://vesa.org/vesa-standards/)来获取这些信息。这里以640*480@60为例教大家如何查看相关参数。

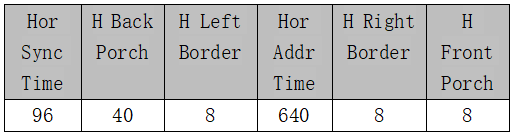

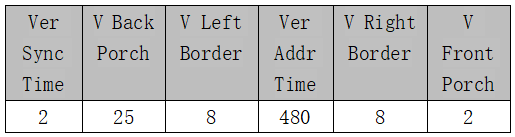

从上图可以分析出行信号的参数(P,像素):

以及场信号的参数(L,行):

不过在实际设计当中一般将H Back Porch和H Left Border合并当作显示后沿(或者称之为行后肩),H Right Border和H Front Porch合并当作显示前沿(或者称之为行前肩)。V Back Porc和V Left Border合并当作场显示后沿(或者称之为场后肩),V Right Border和V Front Porch合并当作场显示前沿(或者称之为场前肩)。

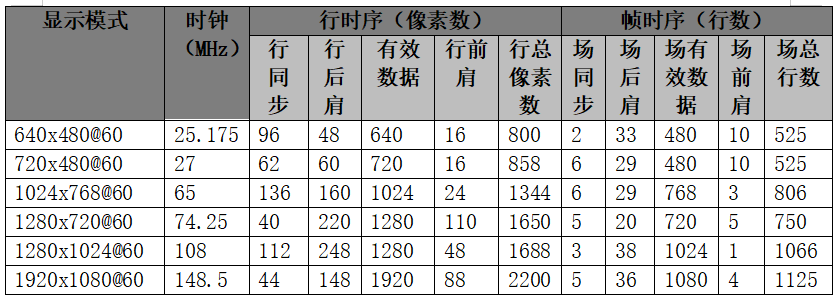

其他常见分辨率的参数查询以此类推,合并后的参数如下表格: